# Aplicación de estrategias Synchornization Free a la resolución de operaciones de Álgebra Lineal Dispersa

Manuel Freire Picón

Programa de Posgrado en Informática Facultad de Ingeniería Universidad de la República

> Montevideo – Uruguay Mayo de 2025

# Aplicación de estrategias Synchornization Free a la resolución de operaciones de Álgebra Lineal Dispersa

Manuel Freire Picón

Tesis de Maestría presentada al Programa de Posgrado en Informática, Facultad de Ingeniería de la Universidad de la República, como parte de los requisitos necesarios para la obtención del título de Magister en Informática.

Director de tesis:

Dr. Ing. Ernesto Dufrechou

Codirector:

Dr. Ing. Pablo Ezzatti

Director académico:

Dr. Ing. Ernesto Dufrechou

Montevideo – Uruguay Mayo de 2025 Freire Picón, Manuel

Aplicación de estrategias Synchornization Free a la resolución de operaciones de Álgebra Lineal Dispersa

/ Manuel Freire Picón. - Montevideo: Universidad de la República, Facultad de Ingeniería, 2025.

XXII, 127 p.: il.; 29,7cm.

Director de tesis:

Ernesto Dufrechou

Codirector:

Pablo Ezzatti

Director académico:

Ernesto Dufrechou

Tesis de Maestría – Universidad de la República, Programa de Informática, 2025.

Referencias bibliográficas: p. 117 – 127.

- 1. Álgebra dispersa, 2. Synchronization Free,

- 3. Computación de alta performance, 4. CUDA, 5. GPU.

#### INTEGRANTES DEL TRIBUNAL DE DEFENSA DE TESIS

| Dra. Lorena Etcheverry |

|------------------------|

| Dr. Gustavo Betarte    |

| Dr. Francisco Igual    |

Montevideo – Uruguay Mayo de 2025

#### RESUMEN

El Álgebra Lineal Numérica dispersa es fundamental en muchas áreas de la computación científica, desde la simulación numérica hasta el aprendizaje automático. Sin embargo, su implementación eficiente en hardware paralelo enfrenta desafíos debido a la baja intensidad computacional y la irregularidad en el acceso a memoria. En el contexto de los métodos iterativos para la resolución de sistemas lineales de gran tamaño, la resolución de sistemas triangulares dispersos (SpTRSV) y la factorización LU incompleta (ILU) representan gran parte del costo computacional.

Esta tesis explora el uso de estrategias synchronization-free para optimizar la ejecución de SpTRSV e ILU en GPUs. En SpTRSV, se estudian las limitaciones del enfoque tradicional basado en la generación de una estructura de niveles y se optimizan implementaciones que siguen el paradigma synchronization-free. Se propone una nueva estrategia para el ordenamiento del cómputo de las filas, así como un formato de almacenamiento diseñado específicamente para acelerar esta rutina. De manera similar, se desarrollan diversas implementaciones de ILU bajo el paradigma synchronization-free, empleando distintas estrategias para la etapa de actualización, el ordenamiento de filas y la distribución de la carga de trabajo entre los hilos.

Los métodos desarrollados son evaluados experimentalmente y comparados con soluciones del estado del arte en diferentes conjuntos de matrices dispersas. Los resultados muestran que las estrategias propuestas logran una reducción significativa en el tiempo de ejecución en SpTRSV y ofrecen resultados competitivos en la ILU.

En resumen, las técnicas synchronization-free demuestran ser una alternativa viable para optimizar el rendimiento en operaciones de álgebra dispersa que tienen dependencias de cómputo, evitando las penalizaciones asociadas a la sincronización explícita y al sobrecosto de lanzamiento de kernels.

Palabras claves:

Álgebra dispersa, Synchronization Free, Computación de alta performance, CUDA, GPU.

#### ABSTRACT

Sparse Numerical Linear Algebra is fundamental in many areas of scientific computing, from numerical simulation to machine learning. However, its efficient implementation on parallel hardware faces challenges due to its low computational intensity and irregular memory access. In the context of iterative methods for solving large linear systems, sparse triangular system solving (SpTRSV) and incomplete LU factorization (ILU) account for a large part of the computational cost.

This thesis explores the use of synchronization-free strategies to optimize the execution of SpTRSV and ILU on GPUs. In SpTRSV, the limitations of the traditional approach based on generating a level structure were studied, and implementations that follow the synchronization-free paradigm were optimized. A new strategy for ordering row computations was proposed, as well as a storage format specifically designed to accelerate this routine. Similarly, several ILU implementations were developed under the synchronization-free paradigm, employing different strategies for the update phase, row ordering, and workload distribution among threads.

The developed methods were experimentally evaluated and compared with state-of-the-art solutions on different sets of sparse matrices. The results show that the proposed strategies achieve a significant reduction in execution time in SpTRSV and offer competitive results on the ILU.

In summary, synchronization-free techniques prove to be a viable alternative for optimizing performance in sparse algebra operations that have computational dependencies, avoiding the penalties associated with explicit synchronization and the overhead of kernel launches.

#### Keywords:

Sparse algebra, Synchronization Free, High performance computing, CUDA, GPU.

# Lista de figuras

| 2.1  | Matriz de ejempio. Los puntos en negro representan no-ceros               |    |

|------|---------------------------------------------------------------------------|----|

|      | mientras que los puntos blancos representan ceros                         | 12 |

| 2.2  | Esquema del formato Coordinate (COO) para una matriz de                   |    |

|      | ejemplo. Extraído de [1]                                                  | 15 |

| 2.3  | Esquema del formato Compressed Sparse Row (CSR) para una                  |    |

|      | matriz de ejemplo. Extraído de [1]. $\ \ldots \ \ldots \ \ldots \ \ldots$ | 16 |

| 2.4  | Esquema del formato ELL para una matriz de ejemplo. Extraído              |    |

|      | y adaptado de [1] $\hdots$                                                | 18 |

| 2.5  | Modelo de ejecución de dos niveles de CUDA. Todos los hilos               |    |

|      | ejecutan el mismo código. Tomado de $[2]$                                 | 22 |

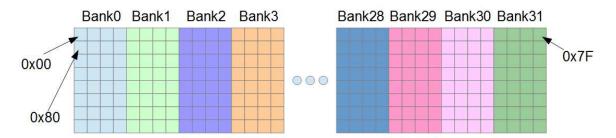

| 2.6  | Ejemplo de la división de memoria compartida en bancos de                 |    |

|      | tamaño 4 Bytes. Extraído de [3]                                           | 24 |

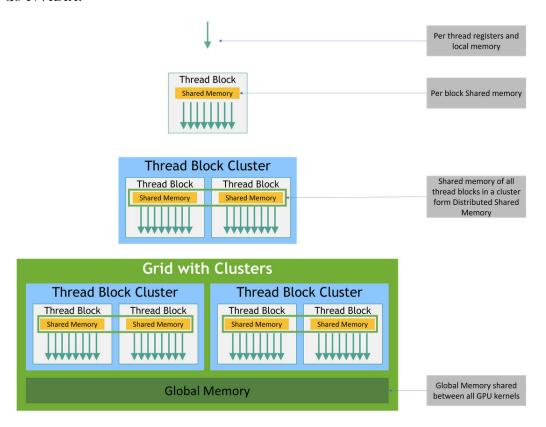

| 2.7  | Esquema de la jerarquía de memoria en CUDA. Extraído de [4].              | 25 |

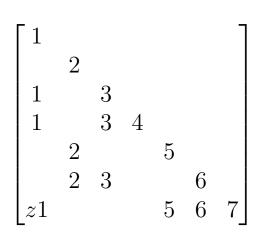

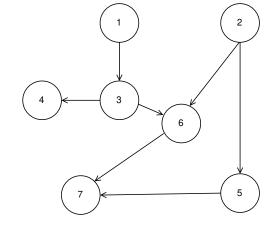

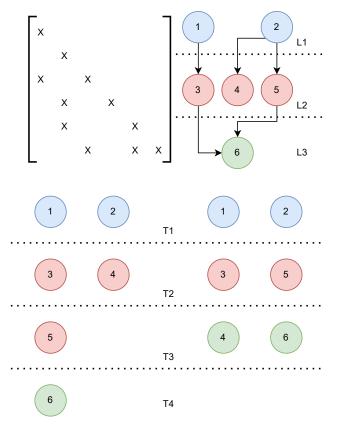

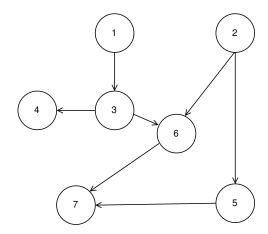

| 2.8  | Matriz dispersa de ejemplo. Los valores no mostrados son ceros.           | 37 |

| 2.9  | Dependencias para la estrategia $self$ -scheduled correspondientes        |    |

|      | a la matriz de la Figura 2.8. Dependencias redundantes fueron             |    |

|      | removidas                                                                 | 37 |

| 2.10 | Estructura de niveles generada a partir de la matriz de ejemplo           |    |

|      | utilizando la estrategia level-set                                        | 40 |

| 3.1  | Esquemas de partición de matrices para los tres algoritmos a              |    |

|      | bloques. Tomado de $[5]$                                                  | 48 |

| 3.2  | Formato Tile aplicado a una matriz de ejemplo. Tomado de [6].             | 48 |

| 3.3  | Matriz de ejemplo y esquema de niveles resultante. Tomada de $[7]$ .      | 50 |

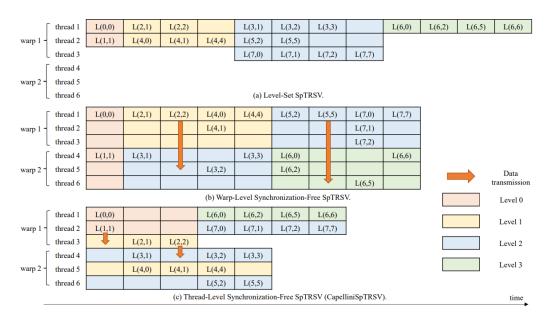

| 3.4  | Esquema de ejecución level-set a nivel de hilos (a), esquema              |    |

|      | sync-free a nivel de $warp$ (b) y esquema de ejecución $sync$ -free       |    |

|      | a nivel de hilos (c). Tomada de [7]                                       | 50 |

| 3.5  | Esquema de ejecución de Yuenyeung. Tomada de [8]                          | 52 |

|      |                                                                           |    |

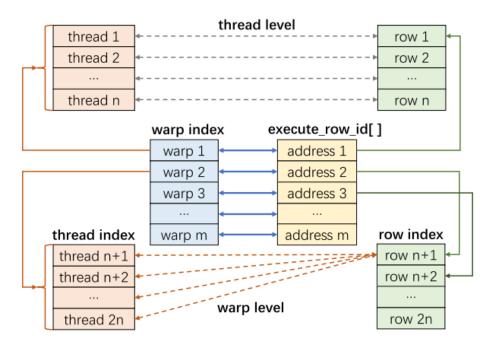

| 4.1  | Ciclo de vida de un $warp$ de $SpTRSV_{mr}$ . El $warp$ recibe el     |    |

|------|-----------------------------------------------------------------------|----|

|      | tamaño de la partición (8 en este caso) y el índice, en el vector     |    |

|      | row_order, de la primera fila a procesar. Tomada de [9]               | 63 |

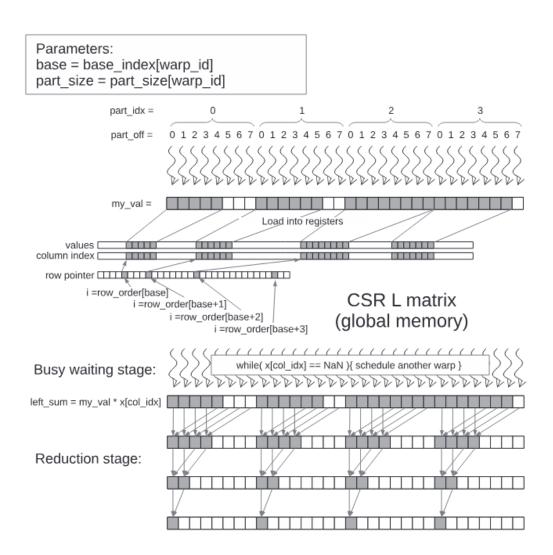

| 4.2  | Formato de almacenamiento de la matriz aplicado a una matriz          |    |

|      | de ejemplo. La primera fila que se muestra en detalle correspon-      |    |

|      | de a un warp particionado de a 4 mientras que las otras dos           |    |

|      | filas a $warps$ que procesan una única fila de más de 32 elementos.   | 66 |

| 4.3  | Ejemplo de la resolución de un sistema lineal en una plataforma       |    |

|      | que puede resolver hasta dos ecuaciones en paralelo. En la parte      |    |

|      | superior se muestra la matriz dispersa y la estructura de niveles     |    |

|      | original. En la parte inferior izquierda la ecuación 6 no puede       |    |

|      | ser resuelta en $T_3$ porque depende de la ecuación 5. En la parte    |    |

|      | inferior derecha, la ecuación 4 es pospuesta y enviada al siguiente   |    |

|      | nivel al no pertenecer al camino crítico                              | 69 |

| 4.4  | Estructura de niveles resultante de la iteración hacia atrás          | 72 |

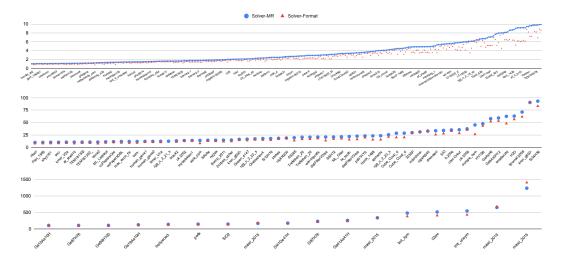

| 4.5  | Tiempo de ejecución de $SpTRSV_{Fmt}$ y $SpTRSV_{mr}$ (en ms).        |    |

|      | Los resultados están ordenados por el tiempo de ejecución de          |    |

|      | $SpTRSV_{mr}$ y divididos en tres grupos de matrices: las que tie-    |    |

|      | nen un tiempo de ejecución entre 1 y 10 ms (arriba), las que          |    |

|      | están entre 10 y 100 (medio), y las que toman más de 100 ms           |    |

|      | (abajo). Matrices que toman menos de 1 ms son dejadas afuera.         | 74 |

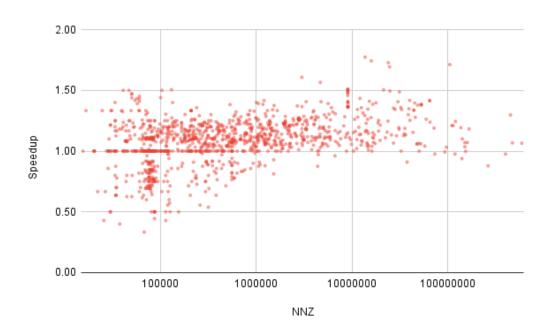

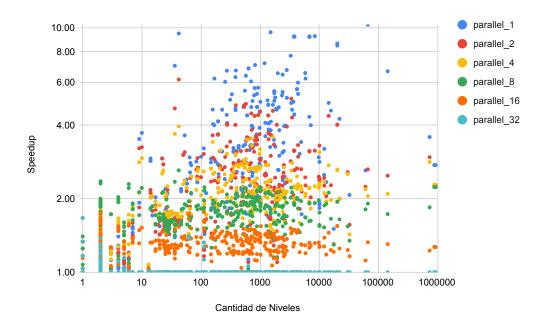

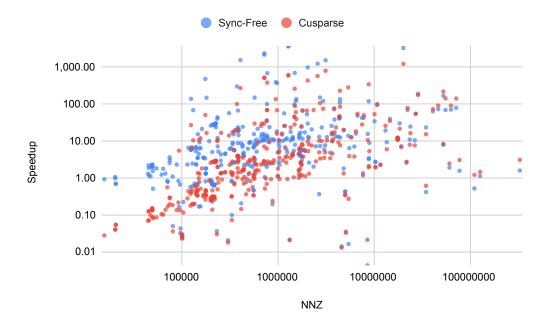

| 4.6  | Valor de $speedup$ de $SpTRSV_{Fmt}$ contra $SpTRSV_{mr}$ en función  |    |

|      | del tamaño de la matriz (tomado como número de no-ceros)              | 75 |

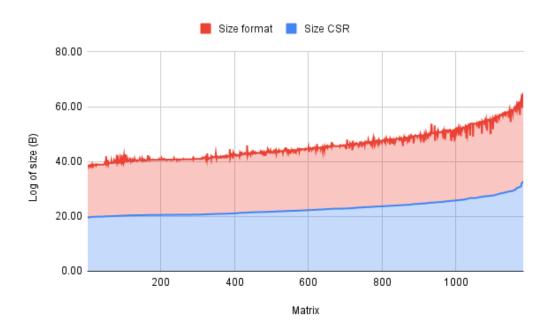

| 4.7  | Logaritmo del costo de memoria (en Bytes) de la estructura            |    |

|      | CSR y la estructura secundaria                                        | 75 |

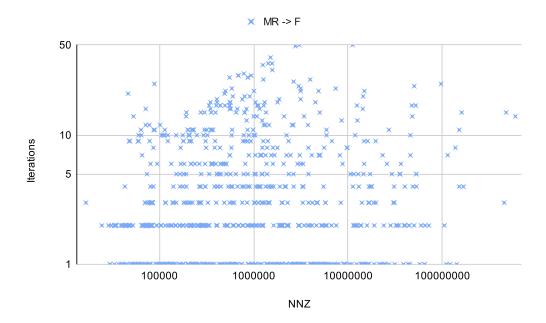

| 4.8  | Número de iteraciones de la etapa de resolución requeridas            |    |

|      | para compensar el costo de ejecutar la etapa de análisis de           |    |

|      | $SpTRSV_{Fmt}$ (F) si se compara con $SpTRSV_{mr}$ (MR)               | 76 |

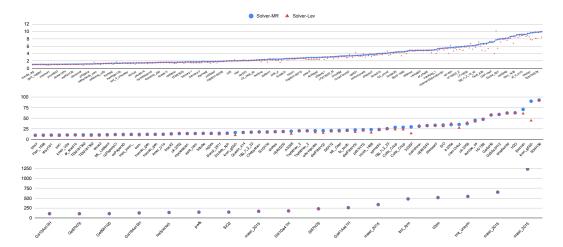

| 4.9  | Tiempo de ejecución de $SpTRSV_{Lev}$ y $SpTRSV_{mr}$ (en ms).        |    |

|      | Los resultados están ordenados por el tiempo de ejecución de          |    |

|      | $SpTRSV_{mr}$ y divididos en tres grupos de matrices: las que tie-    |    |

|      | nen un tiempo de ejecución entre 1 y 10 ms (arriba), las que          |    |

|      | están entre 10 y 100 (medio), y las que toman más de 100 ms           |    |

|      | (abajo). Matrices que toman menos de 1 ms son dejadas afuera.         | 77 |

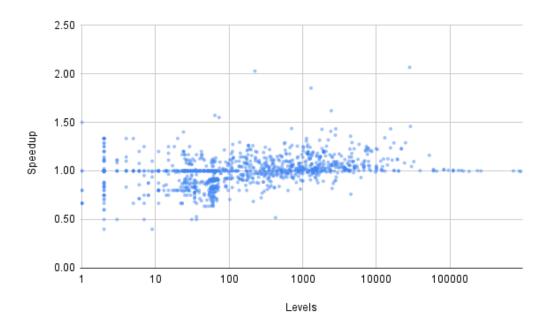

| 4.10 | Valor de $speedup$ de la etapa de resolución de $SpTRSV_{Lev}$ contra |    |

|      | $SpTRSV_{mr}$ en función del número de niveles                        | 78 |

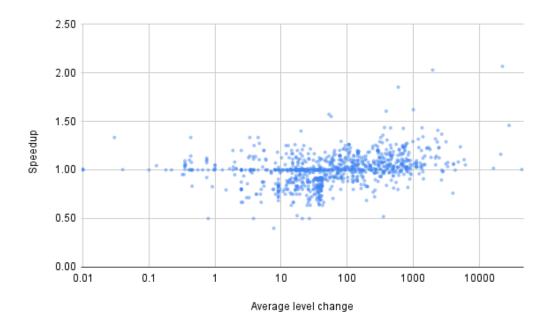

| 4.11 | Resultados de $speedup$ de $SpTRSV_{Lev}$ contra $SpTRSV_{mr}$ como función del promedio de cambios de nivel en las filas de la matriz.                                                                                                                                                                                                             | 79 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

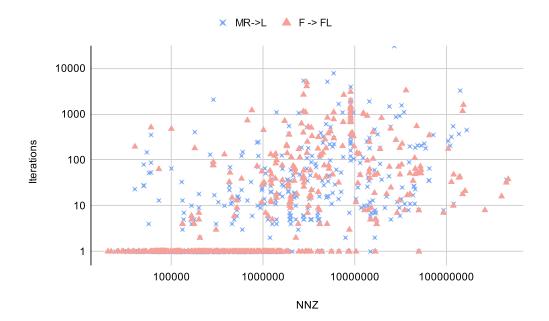

| 4.12 | Número de iteraciones requeridos para justificar la ejecución del análisis que genera la nueva estructura de niveles si se compara con $SpTRSV_{mr}$ (MR->L) y con $SpTRSV_{Fmt}$ (F->FL). Esta gráfica muestra todas las matrices en las que la nueva estrategia de resolución supera a $SpTRSV_{mr}$ o $SpTRSV_{Fmt}$                             | 81 |

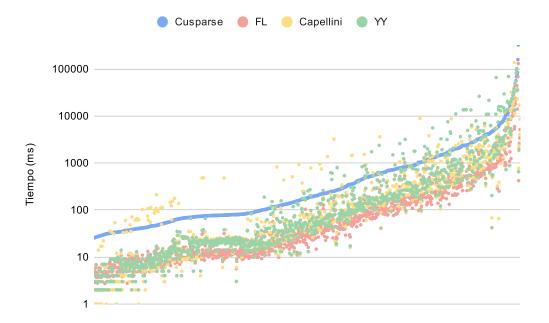

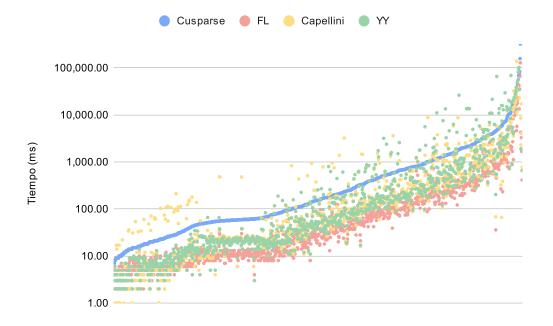

| 4.13 | Comparación del tiempo de ejecución de 100 iteraciones de la etapa de resolución más el análisis para $SpTRSV_{FL}$ (FL) y otras rutinas disponibles públicamente: CUSPARSE, CAPELLINI y YUENYEUNG (YY). Cada punto es una matriz. Las matrices se encuentran ordenadas en función del tiempo de ejecución de CUSPARSE                              | 83 |

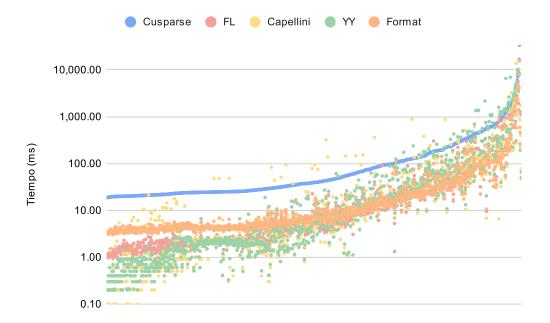

| 4.14 | Comparación del tiempo de ejecución de 10 iteraciones de la etapa de resolución más el análisis para $SpTRSV_{FL}$ (FL), de la versión $SpTRSV_{Fmt}$ y otras rutinas disponibles públicamente: CUSPARSE, CAPELLINI y YUENYEUNG (YY). Cada punto es una matriz. Las matrices se encuentran ordenadas en función del tiempo de ejecución de CUSPARSE | 84 |

| 4.15 | Comparación del tiempo de ejecución de la etapa de resolución de $SpTRSV_{FL}$ (FL) y otras rutinas disponibles públicamente: CUSPARSE, CAPELLINI y YUENYEUNG (YY). Cada punto es una matriz. Las matrices se encuentran ordenadas en función del tiempo de ejecución de CUSPARSE                                                                   | 85 |

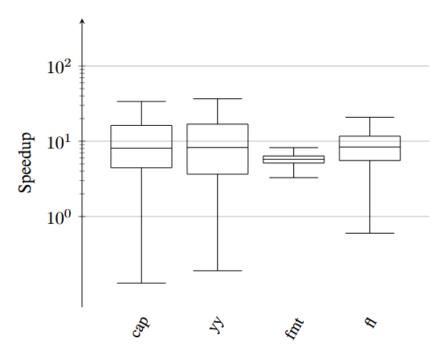

| 4.16 | Boxplots de las distribuciones del valor de $speedup$ en comparación con Cusparse para las rutinas Capellini, Yuenyeung, $SpTRSV_{Fmt}$ y $SpTRSV_{FL}$                                                                                                                                                                                             | 86 |

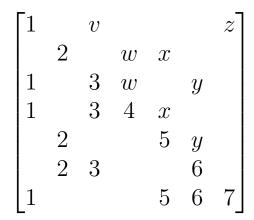

| 5.1  | Matriz de ejemplo. El triángulo inferior y la diagonal es idéntico a la Figura 2.8, pero esta ha sido expandida para agregar elementos arriba de la diagonal. Los elementos no mostrados son coros                                                                                                                                                  | 90 |

| 5.2  | Dependencias para la estrategia <i>sync-free</i> correspondientes a la matriz de la Figura 5.1. Dependencias redundantes fueron re-                                                                                                                                                                                                                 |    |

|      | movidas                                                                                                                                                                                                                                                                                                                                             | 90 |

| 5.3  | Dependencias entre los elementos de la fila 7 de la matriz de la                     |       |

|------|--------------------------------------------------------------------------------------|-------|

|      | Figura 5.1. Se mantienen solamente los elementos de otras filas                      |       |

|      | que son relevantes para las dependencias                                             | 96    |

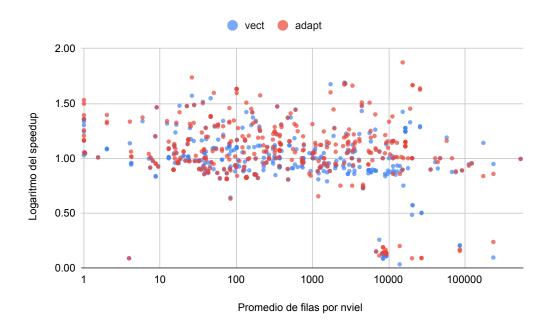

| 5.4  | Valor de speedup de $ILU_{shared}$ , $ILU_{vect}$ e $ILU_{adapt}$ con respecto       |       |

|      | a la peor de ellas en función del promedio de la cantidad de filas                   |       |

|      | por nivel                                                                            | 99    |

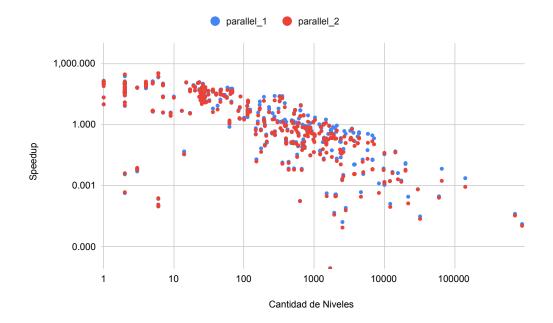

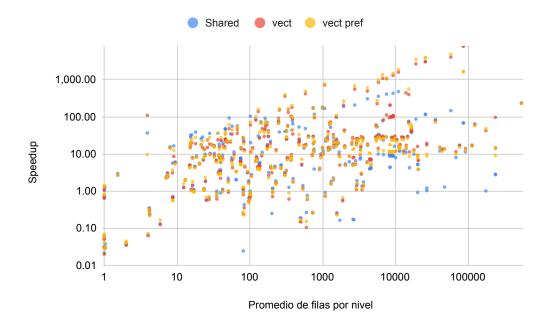

| 5.5  | Valor de $speedup$ de las distintas variantes de $ILU_{parallel}$ compa-             |       |

|      | radas contra la que peores resultados obtiene en función de la                       |       |

|      | cantidad de niveles de la matriz                                                     | 100   |

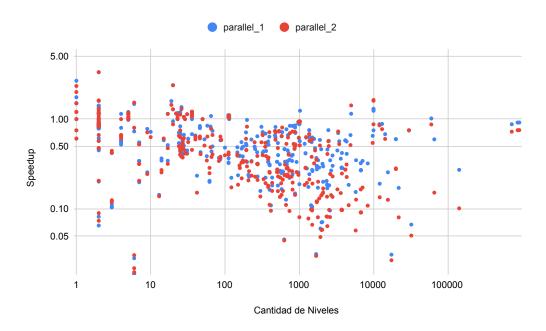

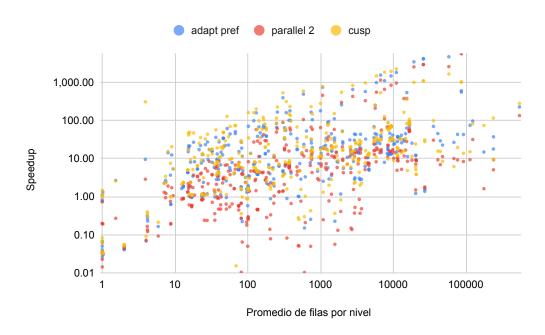

| 5.6  | Valor de $speedup$ de las las variantes de $ILU_{parallel}$ contra                   |       |

|      | $ILU_{shared}$ (a) $ILU_{adapt}$ (b) en función de la cantidad de nive-              |       |

|      | les de la matriz                                                                     | 102   |

| 5.7  | Valor de speedup de la aplicación de la estrategia de prefetch a                     |       |

|      | las variantes $ILU_{vect}$ e $ILU_{adapt}$                                           | 103   |

| 5.8  | Resultados de <i>speedup</i> contra Intel MKL de las rutinas                         |       |

|      | $ILU_{shared}$ , $ILU_{vect}$ (con y sin prefetch) (a) y las rutinas $ILU_{adapt}$ , |       |

|      | $ILU_{parallel}$ con dos hilos y CUSPARSE (b). Todos los valores son                 |       |

|      | presentados en función del promedio de filas por nivel                               | 105   |

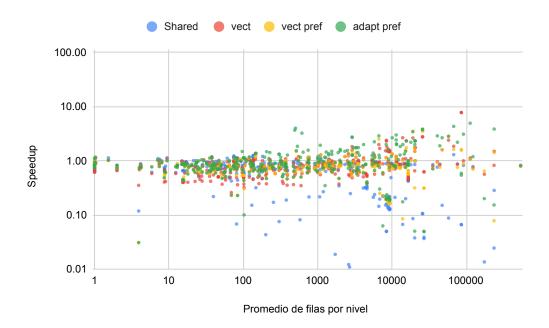

| 5.9  | Valor de speedup de $ILU_{shared}$ , $ILU_{vect}$ (con y sin $prefetch$ ) e          |       |

|      | $ILU_{adapt}$ contra CUSPARSE en función del promedio de filas por                   |       |

|      | nivel                                                                                | 106   |

| 5.10 | Resultados de $speedup$ contra INTEL MKL de $ILU_{levs}$ y CUS-                      |       |

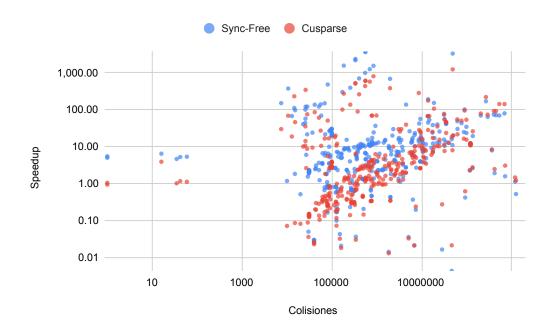

|      | PARSE expresados en función de no-ceros (a) y colisiones (b)                         | 108   |

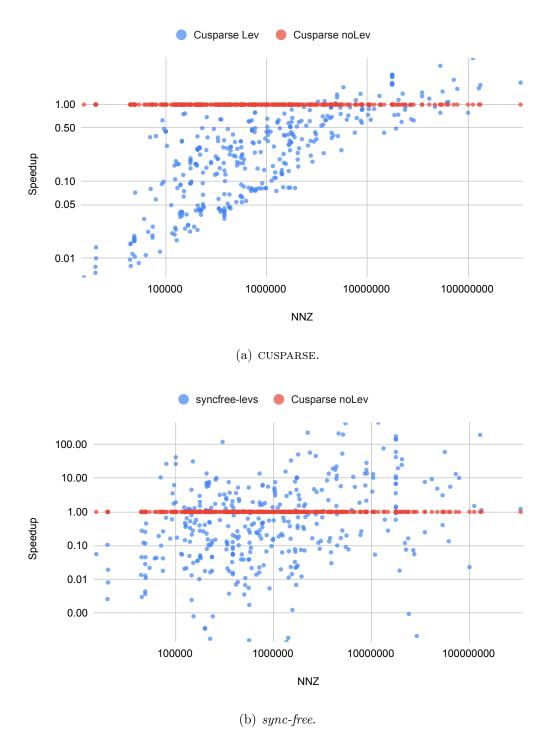

| 5.11 | Valor de $speedup$ de $ILU_{levs}$ contra CUSPARSE utilizando CUS-                   |       |

|      | PARSE_SOLVE_POLICY_USE_LEVEL en función del número de no-                            |       |

|      | ceros (NNZ)                                                                          | 109   |

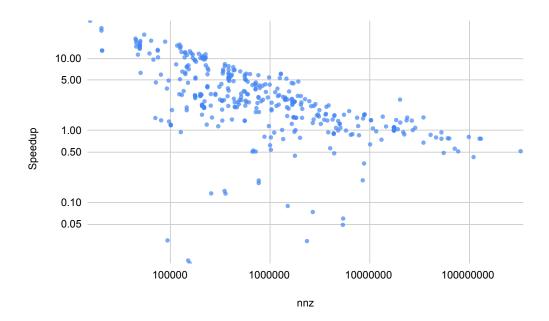

| 5.12 | Valor de $speedup$ de $ILU_{levs}$ contra CUSPARSE utilizando CUS-                   |       |

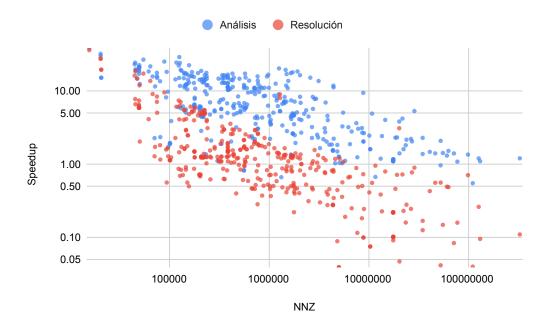

|      | PARSE_SOLVE_POLICY_USE_LEVEL dividido en las etapas de aná-                          |       |

|      | lisis (azul) y resolución (rojo) en función del número de no-ceros                   |       |

|      | (NNZ)                                                                                | 110   |

| 5.13 | Resultados de <i>speedup</i> contra CUSPARSE sin procesamiento                       |       |

|      | de CUSPARSE utilizando CUSPARSE_SOLVE_POLICY_USE_LEVEL                               |       |

|      | (arriba) e $ILU_{levs}$ (abajo)                                                      | . 111 |

# Lista de tablas

| 3.1 | Resumen de los trabajos evaluados para la resolución de siste-                                                                                                     |     |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | mas triangulares                                                                                                                                                   | 53  |

| 3.2 | Resumen de cuáles trabajos superan a otros y si el conjunto de evaluación es pequeño (< 40 matrices) o grande ( $\geq$ 40)                                         | 53  |

| 4.1 | Resumen de los valores de <i>speedup</i> contra CUSPARSE de las 4 rutinas                                                                                          | 85  |

| 4.2 | Tiempo de ejecución agregado de cada rutina para todas las matrices y <i>speedup</i> contra CUSPARSE de este tiempo en el escenario de 10 iteraciones más análisis | 86  |

| 5.1 | Cantidad de matrices, promedio y mediana de speedup de las distintas variables de $ILU_{parallel}$                                                                 | 101 |

# Tabla de contenidos

| Li       | sta d | le figu | ras                                                      | XIII              |

|----------|-------|---------|----------------------------------------------------------|-------------------|

| Li       | sta d | le tabl | as                                                       | XVII              |

| 1        | Intr  | roducc  | ión                                                      | 1                 |

|          | 1.1   | SpTR    | SV e ILU en el ALN dispersa                              | . 2               |

|          | 1.2   | Plataf  | ormas heterogéneas de Hardware y GPUs                    | . 6               |

|          | 1.3   | Métod   | los Synchronization-Free                                 | . 7               |

|          | 1.4   | Objet   | ivos y organización de la tesis                          | . 10              |

| <b>2</b> | Cor   | ceptos  | s preliminares                                           | 11                |

|          | 2.1   | Matri   | ces Dispersas                                            | . 11              |

|          |       | 2.1.1   | Formatos de almacenamiento de matrices dispersas         | . 12              |

|          | 2.2   | Unida   | des de Procesamiento Gráfico (GPU)                       | . 19              |

|          |       | 2.2.1   | Arquitectura de dispositivo unificada de cómputo (CUDA   | A) 21             |

|          |       | 2.2.2   | Sincronización en GPU                                    | . 26              |

|          | 2.3   | Opera   | ciones de Álgebra Dispersa                               | . 28              |

|          |       | 2.3.1   | Multiplicación Matriz Dispersa Vector (SpMV) $$          | . 29              |

|          |       | 2.3.2   | Resolución de Sistemas Triangulares Dispersos ( $SpTRSV$ | <sup>7</sup> ) 30 |

|          |       | 2.3.3   | Multiplicación de Matriz Dispersa por Matriz Dispersa    |                   |

|          |       |         | (SpGEMM)                                                 | . 32              |

|          |       | 2.3.4   | Factorización LU incompleta                              | . 33              |

|          | 2.4   | Parad   | igma Self Scheduled                                      | . 36              |

|          |       | 2.4.1   | Paradigma level-set                                      | . 39              |

|          |       | 2.4.2   | Self-scheduled en GPU (o Sync-Free)                      | . 40              |

| 3        | Tra   | bajo r  | elacionado                                               | 45                |

|          | 3.1   | Uso d   | e técnicas <i>sync-free</i> en ALN dispera               | . 45              |

|   | 3.2  | ьцара                                                                                  | de resolución del kernel SpTRSV                                      | 17                                                       |

|---|------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------|

|   |      | 3.2.1                                                                                  | Comparación de las distintas implementaciones                        | 52                                                       |

|   | 3.3  | Etapa                                                                                  | de análisis del kernel SpTRSV                                        | 53                                                       |

|   | 3.4  | Otras                                                                                  | aplicaciones                                                         | 56                                                       |

|   | 3.5  | Concl                                                                                  | usiones                                                              | 59                                                       |

| 4 | Pro  | puesta                                                                                 | a para la mejora de la resolución de Sistemas Trian-                 |                                                          |

|   | gula | ares D                                                                                 | ispersos                                                             | 31                                                       |

|   | 4.1  | Línea                                                                                  | base $(SpTRSV_{mr})$                                                 | 31                                                       |

|   | 4.2  | Propu                                                                                  | iestas                                                               | 64                                                       |

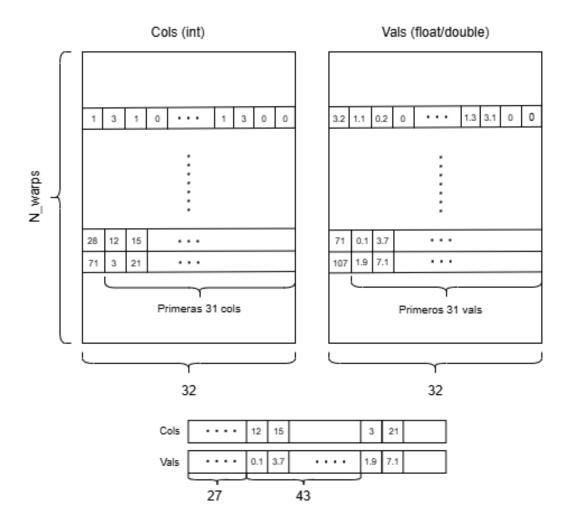

|   |      | 4.2.1                                                                                  | Nuevo formato de almacenamiento $(HYB_{syncfree})$                   | 64                                                       |

|   |      | 4.2.2                                                                                  | Cambio en la estructura de niveles                                   | 68                                                       |

|   | 4.3  | Evalu                                                                                  | ación experimental                                                   | 72                                                       |

|   |      | 4.3.1                                                                                  | Evaluación de $SpTRSV_{Fmt}$                                         | 73                                                       |

|   |      | 4.3.2                                                                                  | Evaluación de $SpTRSV_{Lev}$                                         | 77                                                       |

|   |      | 4.3.3                                                                                  | Comparación con el estado del arte                                   | 31                                                       |

|   | 4.4  | Come                                                                                   | ntarios finales                                                      | 37                                                       |

| 5 | Pro  | puesta                                                                                 | a para la mejora de la factorización LU incompleta 8                 | 39                                                       |

|   | 5.1  | Dropp                                                                                  |                                                                      |                                                          |

|   |      | Tropu                                                                                  | iestas                                                               | 90                                                       |

|   |      | 5.1.1                                                                                  | estas                                                                | 90                                                       |

|   |      | _                                                                                      |                                                                      |                                                          |

|   |      | _                                                                                      | Actualización vía intersección de los vectores en memoria            | 92                                                       |

|   |      | 5.1.1                                                                                  | Actualización vía intersección de los vectores en memoria compartida | 92<br>93                                                 |

|   |      | 5.1.1<br>5.1.2                                                                         | Actualización vía intersección de los vectores en memoria compartida | 92<br>93                                                 |

|   |      | <ul><li>5.1.1</li><li>5.1.2</li><li>5.1.3</li></ul>                                    | Actualización vía intersección de los vectores en memoria compartida | 92<br>93<br>94                                           |

|   |      | 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4                                                       | Actualización vía intersección de los vectores en memoria compartida | 92<br>93<br>94<br>95<br>96                               |

|   | 5.2  | 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6                                     | Actualización vía intersección de los vectores en memoria compartida | 92<br>93<br>94<br>95<br>96                               |

|   | 5.2  | 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6                                     | Actualización vía intersección de los vectores en memoria compartida | 92<br>93<br>94<br>95<br>96<br>97                         |

|   | 5.2  | 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>Evalu                            | Actualización vía intersección de los vectores en memoria compartida | 92<br>93<br>94<br>95<br>96<br>97<br>98                   |

|   | 5.2  | 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>Evalu<br>5.2.1                   | Actualización vía intersección de los vectores en memoria compartida | 92<br>93<br>94<br>95<br>96<br>97<br>98<br>98             |

|   | 5.2  | 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>Evalu<br>5.2.1<br>5.2.2          | Actualización vía intersección de los vectores en memoria compartida | 92<br>93<br>94<br>95<br>96<br>97<br>98<br>98             |

|   | 5.2  | 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>Evalu<br>5.2.1<br>5.2.2<br>5.2.3 | Actualización vía intersección de los vectores en memoria compartida | 92<br>93<br>94<br>95<br>96<br>97<br>98<br>98<br>90<br>03 |

| 6                | Conclusiones y Trabajo Futuro |                      |       |  |  |  |

|------------------|-------------------------------|----------------------|-------|--|--|--|

|                  | 6.1                           | Conclusiones         | . 113 |  |  |  |

|                  | 6.2                           | Publicaciones        | . 114 |  |  |  |

|                  | 6.3                           | Trabajo Futuro       | . 115 |  |  |  |

| $\mathbf{R}_{0}$ | efere                         | ncias bibliográficas | 117   |  |  |  |

### Capítulo 1

#### Introducción

El Álgebra Lineal Numérica es una piedra angular de la computación científica, teniendo un rango de aplicación en campos que van desde la física a la ciencia de datos [10, 11]. Muchas tareas como simulaciones o redes neuronales tienen su cuello de botella en rutinas de álgebra lineal. El álgebra dispersa añade desafíos no presentes en el álgebra densa, en especial relativos a su baja intensidad computacional (ratio de operaciones de punto flotante por byte accedido a memoria) y de no localidad de datos (los datos requeridos en cada punto no están necesariamente cercanos en memoria) [12].

Siguiendo la metodología empleada en el álgebra densa, en la que los métodos numéricos se construyen en términos de un conjunto acotado de operaciones básicas determinado por la especificación BLAS (Basic Linear Algebra Subprograms) [13], el álgebra dispersa también cuenta con su juego de operaciones fundamentales. Debido a las características de los algoritmos sobre matrices, este conjunto es bastante más reducido que el determinado por BLAS. Del análisis de los métodos más utilizados para resolver sistemas de ecuaciones lineales, así como problemas de vectores y valores propios sobre matrices dispersas, surge que los principales cuellos de botella desde el punto de vista computacional ocurren en la solución de sistemas de ecuaciones triangulares (operación denominada SpTRSV) y, en menor medida, en el producto matriz-vector (SpMV) [14]. Además, una importante familia de métodos para resolver problemas dispersos de gran tamaño (los métodos llamados iterativos), frecuentemente se valen de factorizaciones aproximadas o incompletas de la matriz dispersa para acelerar su convergencia, lo que agrega operaciones como la Factorización LU Incompleta (ILU) al conjunto de rutinas fundamentales sobre matrices dispersas.

Si bien las operaciones SpMV, SpTRSV e ILU, no son las únicas operaciones básicas definidas sobre matrices dispersas, sí gozan de una relevancia para la ciencia y la ingeniería que ha atraído la atención de la comunidad dedicada a la computación de alto desempeño durante un largo tiempo. Como consecuencia, la implementación paralela de la SpTRSV y la ILU ha sido estudiada para varias plataformas de hardware. En particular, el desarrollo de las GPU en la última década ha impulsado los trabajos sobre esta plataforma. Las GPUs son plataformas muy utilizadas en el álgebra lineal debido a su gran poder de cómputo y, especialmente en el caso del álgebra lineal dispersa, su gran ancho de banda de memoria. Sin embargo, para sacar provecho de las GPUs es necesario mantener una gran ocupación (tener suficiente paralelismo para mantener una gran cantidad de procesadores ocupados) y explotar eficientemente el ancho de banda de acceso a memoria.

En el caso de las operaciones SpTRSV e ILU, un obstáculo importante para lograr lo anterior es el manejo de las dependencias entre el procesamiento de distintas filas de la matriz. Esto implica el empleo de distintos mecanismos de sincronización entre hilos, lo cual agrega un costo que se no se encuentra en otras operaciones como la SpMV. Durante años, el paradigma dominante para el manejo de esta sincronización en diversos tipos de hardware consistió en el preprocesamiento de la matriz para determinar un esquema fijo de ejecución de los hilos donde se respetaran estas dependencias [15, 16]. En los últimos tiempos, un nuevo conjunto de algoritmos, denominados Synchronization-Free (sync-free), ha ganado relevancia. A diferencia de los anteriores, estos se basan en planificar la ejecución de los hilos conforme avanza el procesamiento de la matriz, obligando a algunos hilos a esperar hasta que otros resuelven sus dependencias. En estos últimos se centra la temática de la tesis.

#### 1.1. SpTRSV e ILU en el ALN dispersa

Uno de los ejemplos más relevantes del ALN dispersa es la resolución de ecuaciones en derivadas parciales (PDEs por sus siglas en inglés -Partial Differential Equations-). Estas ecuaciones son una herramienta muy importante para modelar diversos problemas que abarcan áreas tan dispares como la física o la economía [17, 18]. Sin embargo, la complejidad y el número de parámetros involucrados suelen hacer inviables las soluciones analíticas. Por ello, la estra-

tegia más común es discretizar el dominio del problema en una malla finita de elementos o puntos, lo cual es la base de los métodos de diferencias finitas, volúmenes finitos o elementos finitos. Este tipo de estrategias genera grandes sistemas de ecuaciones lineales del tipo Ax = b, donde A es la matriz de coeficientes, x el vector de las incógnitas, y b el de los valores independientes. Debido a que los coeficientes expresan relaciones entre partes cercanas del dominio, la matriz A tiende a tener grandes dimensiones y una baja proporción de coeficientes distintos de cero ya que cada punto de la malla se relaciona con los elementos cercanos.

La resolución de estos sistemas es, en general, la parte más costosa de estos métodos, tanto en cuanto a tiempo de cómputo como a consumo de memoria [14]. Para resolverlos, existen dos grandes enfoques: directo e iterativo. El primero consiste en aplicar una serie de transformaciones a la matriz para llegar a un sistema equivalente pero más fácil de resolver (por ejemplo, las estrategias basadas en la eliminación Gaussiana llevan a una matriz diagonal) [19]. La gran ventaja de estos métodos es que obtienen resultados exactos (a menos de los errores inevitables debido al uso de punto flotante). Los métodos iterativos, por otro lado, parten de una solución inicial y la mejoran en iteraciones sucesivas hasta cumplir cierto criterio de calidad de la solución (o exceder un máximo número de iteraciones). Estos métodos se convierten en la alternativa viable con sistemas de gran escala, ya que los métodos directos no escalan bien con el tamaño del problema y sus requerimientos (cómputo y memoria) se vuelven prohibitivos en sistemas de gran tamaño [14].

Existen dos grandes grupos de métodos iterativos: estacionarios y métodos de Krylov. El primer grupo son métodos que reformulan el sistema Ax = b sustituyendo A por M - N, con M siendo una matriz sencilla de invertir. Esto permite reescribir el sistema como (M-N)x = b generando la iteración  $x^{k+1} = x^k + M^{-1}(b - Ax^k)$ . Ejemplos de estos grupos incluyen Jacobi y Gauss-Seidel. La principal desventaja de estas estrategias es que convergen únicamente en casos específicos.

Por otro lado, los métodos de Krylov, como el método del Gradiente Conjugado (CG) y GMRES, construyen un subespacio a partir de las potencias sucesivas del sistema aplicadas al vector b. El objetivo es aproximar la solución del sistema dentro de estos subespacios, minimizando el error ( $e^k = x - x^k$ ) o el residuo ( $r^k = b - Ax^k$ ) según el criterio específico del método. Este enfoque permite una adaptación iterativa que, en términos teóricos, puede garantizar la

convergencia bajo ciertas condiciones [20]. Sin embargo, en sistemas grandes la convergencia de estos métodos puede ser muy lenta o no ocurrir en la práctica. Es decir, el progreso que se hace en cada iteración es, en el mejor de los casos, muy pequeño. La convergencia depende sustancialmente de la distribución de los valores propios, lo que se refleja en el número de condición (el coeficiente de los valores propios de mayor y menor magnitud de la matriz). Si este número es muy alto, se dice que el problema está mal condicionado, lo que implica que pequeñas variaciones (o errores) en los datos de entrada generan grandes diferencias en los resultados [21, 22].

Para mejorar esta convergencia se utiliza el precondicionamiento. En algunos casos se puede aprovechar información específica del problema para diseñar precondicionadores adecuados al mismo. Este conjunto de precondicionadores, conocidos como geométricos, utiliza información de la malla o discretización del dominio para mejorar la convergencia del método iterativo. Sin embargo, en muchos casos no se cuenta con información de la geometría subyacente del problema. En este contexto, se utilizan los precondicionadores algebraicos, los cuales se construyen directamente a partir de la matriz del sistema [14].

Una forma de ver el precondicionamiento consiste en multiplicar al sistema Ax = b de los dos lados por una matriz  $M^{-1}$  tal que el número de condición de  $M^{-1}A$  mejore, y resolver el sistema equivalente  $M^{-1}Ax = M^{-1}b$ . En este sentido, idealmente la matriz  $M^{-1}$  es "relativamente similar" a  $A^{-1}$  o, lo que es lo mismo, se quiere hallar una matriz M similar a A pero fácilmente invertible. Por lo anterior, una buena elección de M tiene implicancia directa en la cantidad de iteraciones que requerirá el método iterativo. Si bien la multiplicación del sistema por  $M^{-1}$  reduce el número de iteraciones, implica la necesidad de invertir la matriz M, algo potencialmente mucho más costoso, ya que generalmente  $M^{-1}$  será una matriz densa. En general, la multiplicación del sistema por  $M^{-1}$  no se hace de manera explícita sino que en su lugar se obtiene una aproximación dispersa  $M^{-1} \approx A^{-1}$  y se realiza el producto matriz-vector  $z^k = M^{-1}r^k$  en cada iteración del método, o se obtiene una factorización de  $M \approx A$  y resuelve el sistema equivalente  $Mz^k = r^k$ , donde  $r^k$  sería el residuo de cada iteración. Este comportamiento puede observarse en la línea 7 del Algoritmo 1, donde se muestra un pseudocódigo del método de Gradiente Conjugado Precondicionado (PCG por sus siglas en inglés -Preconditioned Conjugate Gradient-).

Uno de los precondicionadores algebraicos más utilizados es la factorización

## Algoritmo 1 Pseudocódigo del método del gradiente conjugado precondicionado.

```

// In: A: Matriz simétrica y definida positiva, b: Vector de

resultados

// In: M: Precondicionador, x0: Solución inicial, tol: Tolerancia,

max_iter: Máximo número de iteraciones

// Out: x: Solución aproximada

//Inicializaciones

r_0 = b - A \times x_0

Resolver Mz_0 = r_0 // Solución de sistema triangular en vez de M^{-1}r_0

p_0 = z_0

x = x_0

for k = 0 to max_iter do:

lpha_k = (r_0^T 	imes z_0)/(p_0^T 	imes A 	imes p_0) // Cálculo de lpha_k

11

x=x+lpha_k	imes p_0 // Actualización de la solución

r_1 = r_0 - \alpha_k \times A \times p_0 // Cálculo del nuevo residuo

13

// Si converge retornar

if ||r_1|| < \text{tol do}:

return x

17

endif

18

19

Resolver Mz_1=r_1 // Solución del sistema en lugar de

multiplicar por M^{-1}

eta_k = (r_1^T 	imes z_1)/(r_0^T 	imes z_0) // Cálculo de eta_k

p_1 = z_1 + eta_k 	imes p_0 // Actualización de la dirección de búsqueda

22

23

// Actualizaciones

r_0 = r_1

z_0 = z_1

p_0 = p_1

endfor

return x

```

LU incompleta (ILU). Esta operación consiste en hallar dos matrices dispersas (L, triangular inferior y U, triangular superior) que cumplan que  $LU \approx A$ . La ventaja de definir M = LU es que la resolución del sistema  $Mz^k = r^k$  es equivalente a hacer dos resoluciones triangulares:  $Ly = r^k$  y  $Uz^k = y$ .

Gran parte del costo de las iteraciones (y por ende de la resolución de Ax = b) queda definido por la aplicación del precondicionador sobre el residuo. Por esto, los kernels para computar el precondicionador (ILU) y la resolución

# 1.2. Plataformas heterogéneas de Hardware y GPUs

La evolución de la computación ha estado guiada por el objetivo de aumentar la velocidad y capacidad de procesamiento o, en otras palabras, el poder de cómputo. Los primeros sistemas de computación contaban con una única unidad central de procesamiento (CPU, por sus siglas en inglés -Central Processing Unit-), lo que implicaba que el procesamiento de las tareas debía realizarse de manera secuencial. En este contexto, la estrategia predominante para mejorar el desempeño consistió en aumentar la frecuencia de reloj de los procesadores. Sin embargo, este enfoque encontró límites físicos debido al incremento del consumo energético y la generación de calor, los cuales comenzaron a contrarrestar las ganancias en velocidad de cómputo. Ante estas limitaciones, la industria viró hacia arquitecturas capaces de ejecutar múltiples tareas en paralelo, lo que marcó el inicio de la computación paralela como un paradigma dominante [23].

A principios de la década de 2000, comenzaron a surgir distintos dispositivos de hardware especializados, como las GPUs, que revolucionaron el campo del cómputo de alto desempeño. Originalmente diseñadas para acelerar el procesamiento gráfico en videojuegos, las GPUs se caracterizan por contar con una gran cantidad de unidades de procesamiento dedicadas a realizar cálculos en paralelo. Esta arquitectura motivó su exploración y eventual adopción en el cálculo científico y otras aplicaciones generales, inicialmente mediante la adaptación de implementaciones a las operaciones gráficas predefinidas. Posteriormente, con el desarrollo de entornos de programación como CUDA y OpenCL, se amplió su uso para resolver problemas de cómputo intensivo en diversas disciplinas, desde la simulación numérica hasta la inteligencia artificial. En particular, las GPUs son altamente eficientes cuando se requiere realizar la misma operación sobre un conjunto masivo de datos relativamente independientes, una característica que las hace idóneas para algoritmos con alto grado de paralelismo. En estos dispositivos, las tareas se organizan en kernels (funciones que ejecuta en la GPU), que son despachados para ejecutarse en

<sup>&</sup>lt;sup>1</sup>Junto con la multiplicación matriz dispersa - vector (SpMV).

paralelo por grandes cantidades de hilos que repiten el mismo cómputo sobre distintos datos.

El crecimiento y diversificación de las plataformas de hardware propició el advenimiento del cómputo heterogéneo, donde distintos tipos de procesadores con capacidades especializadas trabajan de manera conjunta dentro de un mismo sistema [24]. Esta estrategia permite aprovechar las ventajas de cada arquitectura: por ejemplo, las CPUs son adecuadas para la ejecución de tareas secuenciales y operaciones con alta dependencia de control, mientras que las GPUs destacan en cargas de trabajo altamente paralelizables y de gran volumen de datos. Además de las GPUs, han emergido otros aceleradores especializados como las Field-Programmable Gate Arrays (FPGAs) y las Tensor Processing Units (TPUs), optimizados para aplicaciones específicas como el procesamiento de señales o el aprendizaje profundo.

No obstante, el uso eficiente de plataformas heterogéneas presenta desafíos significativos. La comunicación y coordinación entre los distintos procesadores introduce costos de sincronización, los cuales pueden ser significativos en aplicaciones con alta interdependencia entre hilos o con baja intensidad computacional. En sistemas masivamente paralelos, la sincronización entre hilos puede convertirse en un cuello de botella, afectando el rendimiento global si no se emplean estrategias específicas para mitigar su costo. Por otro lado, la transferencia de datos entre dispositivos de diferentes arquitecturas introduce latencias adicionales. Para abordar estos desafíos, debe ponerse foco en el desarrollo de estrategias que reduzcan el costo de la sincronización y la comunicación en general.

#### 1.3. Métodos Synchronization-Free

Para resolver un sistema triangular de manera exacta, el procedimiento que se emplea es el de sustitución hacia adelante (cuando es una matriz triangular inferior) o hacia atrás (cuando es una matriz triangular superior). Este procedimiento consiste en recorrer las ecuaciones en orden, sustituyendo todas las incógnitas correspondientes a las ecuaciones previas por los valores ya calculados.

En el caso de la factorización LU (tanto completa como no), se debe transformar A usando la eliminación Gaussiana, es decir, transformando en 0 los elementos debajo de la diagonal mediante la resta de múltiplos de las filas

anteriores. Los multiplicadores usados para crear estos ceros se almacenan en L, mientras que U guarda los coeficientes restantes. La diferencia entre la factorización LU e ILU es que en la segunda se garantiza que las matrices L y U sean dispersas<sup>2</sup> aunque la multiplicación de estas dos matrices no resulta exactamente en la obtención de la matriz original, sino una "relativamente parecida". Al igual que en la SpTRSV, las filas son recorridas en orden y de izquierda a derecha.

Ambas operaciones tienen características que hacen que no sea trivial generar implementaciones paralelas de dichas rutinas. Por ejemplo, su baja intensidad aritmética (son problemas memory bound), la falta de equilibrio en la carga (el procesamiento de algunas filas requiere significativamente más tiempo y cómputo que otras) y las dependencias entre las distintas tareas. En particular, estas dependencias son una gran limitante del paralelismo. En matrices densas, el paralelismo puede darse al impactar el resultado de una fila i que se ha terminado de procesar, en múltiples filas a la vez, ya sea para sustituir la incógnita (TRSV) o hacer 0 el valor (LU). Sin embargo, las filas no pueden procesarse completamente en paralelo ya que, para impactar los valores de una fila, esta debe haberse terminado de procesar. Por el contrario, cuando se trabaja con operaciones de matrices dispersas, la mayoría de las filas dependen solamente de un conjunto reducido de filas, por lo que existen conjuntos de filas independientes que pueden ser procesadas en paralelo. En concreto, en ambas rutinas toda fila i depende de una fila j (j < i) si tiene una entrada no-cero en la columna j, ya que requiere el valor de la incógnita  $x_i$  (o del pivot, en ILU) para poder calcular sus propios valores. En matrices en las que existen muchas dependencias, o dependencias transitivas que serializan el cálculo (como por ejemplo, matrices tri-diagonales), el costo de sincronización puede ser relevante en el total de la rutina, contrarrestando las ganancias producto del paralelismo.

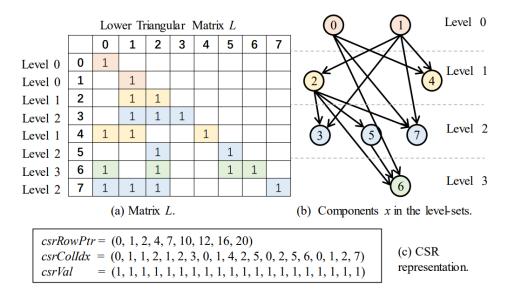

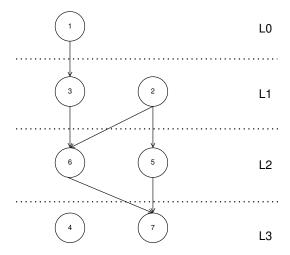

En GPU existen dos grandes paradigmas para implementar la *SpTRSV* y ordenar el cómputo de las filas según sus dependencias: *level-set* [16] y *self-scheduled* (o *sync-free*) [25]. El primero se compone de dos etapas: primero se ejecuta un preprocesamiento (análisis) y, posteriormente, se procesa el cálculo dividido en varios pasos, cada uno de los cuales procesa un conjunto de filas en

$<sup>^2</sup>$ En el caso de la ILU-0 el patrón de dispersión se mantiene exactamente igual a A mientras que en ILU-k se permite cierto grado de fill-in (es decir, de que algunas entradas que eran 0 en la matriz A tengan un no-cero en L o U).

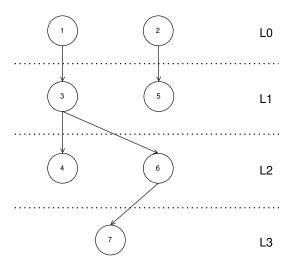

paralelo (resolución). La etapa de análisis genera conjuntos llamados niveles de filas que pueden ejecutarse en paralelo (no dependen entre ellas) y únicamente dependen de filas en niveles inferiores. Luego, la etapa de resolución lanza un kernel que procesa las filas del primer nivel; una vez terminado, se lanza otro para el segundo y así sucesivamente. Este orden de ejecución garantiza que cuando una fila es procesada, todas sus dependencias están resueltas, y permite evitar deadlocks<sup>3</sup>. Si bien el preprocesamiento puede ser costoso, este puede ser reutilizado para sucesivas resoluciones con distintos valores de b u otras operaciones sobre una matriz con el mismo patrón de dispersión (variación de los coeficientes) generando que el costo sea compensado. En este paradigma, el costo de sincronización está dado por el de lanzamiento de cada uno de los kernels que, si bien individualmente es insignificante, en contextos con muchos niveles y pocas filas por nivel, puede acumularse y convertirse en una parte significativa del tiempo total.

El paradigma sync-free busca resolver la problemática mencionada anteriormente y eliminar el costo de sincronización entre los niveles. Para esto, se elimina el preprocesamiento y se procesan las filas en el orden dado por la matriz. Si bien el orden de ejecución también evita los deadlocks (cuando una fila i comienza a ejecutar, ya lo hicieron todas las filas j con j < i de las que podría depender) a priori podría generar condiciones de carrera<sup>4</sup>. Para evitar esto, los hilos que ejecutan cada fila chequean si las dependencias están cumplidas mediante polling (o espera activa) antes de procesarla. Las estrategias de espera activa ( $busy\ waiting$ ) generalmente no son recomendables, ya que implican un gran costo al utilizar tiempo de cómputo en consultar constantemente por la disponibilidad de un recurso. Sin embargo, gracias a la forma en que el hardware de la GPU planifica la ejecución de los hilos, en la práctica se generan bloqueos implícitos al hacer estas consultas y otros hilos pueden ejecutar mientras unos preguntan por sus dependencias.

$<sup>^3</sup>$ Situación dentro de un sistema informático en la que dos o más tareas por ejemplo: hilos o procesos se esperan mutuamente para terminar o continuar su trabajo. Esta situación detiene las tareas y les impide continuar pudiendo bloquear otras tareas o potencialmente el sistema entero. En el caso concreto del SpTRSV en GPU esto puede darse si todos los procesadores son utilizados para procesar filas que dependen de otras que están esperando para ejecutar

<sup>&</sup>lt;sup>4</sup>Una condición de carrera es la condición de un sistema electrónico, software u otro sistema en el que el comportamiento sustantivo del sistema depende de la secuencia o el tiempo en el que suceden otros eventos incontrolables.

#### 1.4. Objetivos y organización de la tesis

En este trabajo se aborda el uso de métodos sync-free en arquitecturas de hardware masivamente paralelas para acelerar operaciones de álgebra lineal dispersa con un importante costo de sincronización, como la SpTRSV y la ILU. Concretamente, en el caso de la operación SpTRSV se continúan esfuerzos presentados en [9, 26] para mejorar el desempeño computacional de la resolución de sistemas triangulares dispersos explorando nuevos patrones de cómputo y formatos de almacenamiento especializados. Se presentan dos contribuciones principales: un formato de almacenamiento especialmente diseñado para mejorar el acceso a memoria de la operación y una nueva estrategia para ordenar el cómputo de las filas. Los resultados experimentales muestran que estos cambios mejoran el tiempo de cómputo de las rutinas.

Posteriormente, producto de su patrón de dependencias similar, se explora la aplicación de técnicas sync-free a la factorización LU incompleta. Contrario a lo que ocurre con la SpTRSV, no se encontraron otros trabajos que apliquen el paradigma sync-free a esta operación, por lo que se dedicaron los esfuerzos a proponer una suite de rutinas con distintas estrategias y compararlas entre sí.

La estructura de este manuscrito es la siguiente. En el Capítulo 2 se presentan los conceptos básicos para la comprensión de esta tesis. Se explican las matrices dispersas con especial énfasis en estrategias para almacenarlas en memoria. También se introducen las características fundamentales de las GPUs, las principales operaciones del álgebra lineal dispersa y el paradigma de cómputo utilizado en este trabajo (sync-free). Posteriormente, en el Capítulo 3 se presenta una revisión del estado del arte en lo relativo a la aplicación del paradigma sync-free a distintas rutinas del álgebra lineal. Se constata que gran parte de los esfuerzos fueron puestos en la aceleración de la SpTRSV pero también existen trabajos sobre otras rutinas. En el Capítulo 4 se describen los aportes relativos a la resolución de sistemas triangulares dispersos. A continuación, en el Capítulo 5 se compendian los aportes relativos a la ILU. Finalmente, en el Capítulo 6 se presentan las conclusiones de la tesis y posibles líneas de trabajo futuro.

### Capítulo 2

## Conceptos preliminares

En este capítulo se presentan los conceptos preliminares relevantes para la comprensión del trabajo de maestría. En la Sección 2.1 se presentan las matrices dispersas y, en especial, las estrategias para almacenarlas en memoria. En la Sección 2.2 se comentan las características fundamentales de las tarjetas de procesamiento gráfico (conocidas como GPU por sus siglas en inglés -Grafics Processing Units-), la principal plataforma de cómputo utilizada en esta tesis. Posteriormente, en la Sección 2.3 se describen las principales operaciones de álgebra dispersa [14, 19, 27]. Finalmente, en la Sección 2.4 se explica el paradigma de cómputo self scheduled.

#### 2.1. Matrices Dispersas

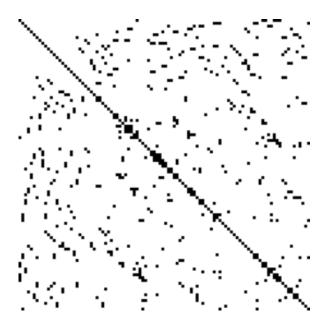

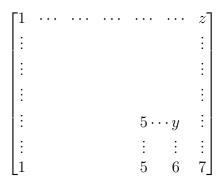

No existe una definición única, o de consenso, para las matrices dispersas. Una idea intuitiva es que las matrices dispersas son matrices en las que la mayoría de sus coeficientes tienen valor 0<sup>1</sup>. Dado que la baja proporción de no-ceros es la única condición que debe cumplir una matriz para ser dispersa, esto genera que exista una amplia variedad de tipos de matrices según sus características y el campo de aplicación del que provienen [12]. Algunos ejemplos de los diversos campos de aplicación son la resolución de ecuaciones en derivadas parciales utilizando métodos de elementos finitos (FEM por sus siglas en inglés -Finite Element Methods-), la simulación de circuitos o las operaciones de grafos que se usan en redes sociales. La Figura 2.1 presenta un ejemplo de una matriz dispersa que cuenta con no-ceros en toda la diagonal.

<sup>&</sup>lt;sup>1</sup>Puede ser dispersa respecto a otro valor.

**Figura 2.1:** Matriz de ejemplo. Los puntos en negro representan no-ceros mientras que los puntos blancos representan ceros.

Las matrices dispersas pueden ser clasificadas según características como si son cuadradas o rectangulares, la cantidad de no-ceros, de filas o de columnas. Además, independientemente de estas métricas, existen características relativas al patrón de dispersión (cómo están organizados los coeficientes no-ceros) como, por ejemplo, si la matriz es simétrica, de banda, a bloques, etc. Finalmente, si se consideran los valores de los coeficientes y no únicamente el patrón de dispersión, se pueden caracterizar por ciertas propiedades numéricas como el número de condición, el rango, si es numéricamente simétrica o si es definida positiva. Las matrices de cierto tipo de aplicación en muchos casos comparten algunas características, por ejemplo, las matrices que surgen de ecuaciones en derivadas parciales con grillas regulares de dos dimensiones son esencialmente pentadiagonales debido a la forma en que se vinculan los elementos de la grilla [12].

# 2.1.1. Formatos de almacenamiento de matrices dispersas

Cuando se almacenan matrices densas no existen demasiadas alternativas. En general, se utiliza un arreglo de  $n \times m$  elementos donde n y m con la cantidad de filas y columnas respectivamente. La única variable a considerar es si se almacenan contiguamente en memoria los elementos de una misma fila

(conocido como ordenamiento  $row\ major$ ) o columna ( $column\ major$ ). La gran ventaja de estas estrategias es que, una vez que se sabe el ordenamiento de los datos, los índices de fila y columna están implícitos en la posición de memoria, es decir, el elemento ij se encuentra en la posición  $i \times m + j$  si es  $row\ major$  o  $j \times n + i$  si no<sup>2</sup>.

Esta estrategia de almacenamiento cuenta con dos principales ventajas. La primera y más evidente consiste en que es posible acceder en O(1) a cualquier elemento si se tienen sus índices. Esto posibilita implementaciones sencillas para operaciones de álgebra numérica como la suma de matrices, multiplicación escalar o trasposición. La segunda ventaja es que este tipo de almacenamiento permite explotar la localidad espacial de los datos, ya que todos los elementos que están cercanos en la matriz están cercanos en memoria. Esto permite mejores patrones de acceso a memoria y uso de caché cuando se implementan las operaciones mencionadas anteriormente.

Por otro lado, las matrices dispersas generan desafíos adicionales a la hora de almacenarlas. Aunque la estrategia de utilizar un arreglo es eficiente en el caso denso, en el disperso generaría un desperdicio de memoria importante al almacenar una gran cantidad de entradas con valor cero. Incluso en el caso de que la cantidad de memoria no fuera un problema, esto también generaría dificultades en las operaciones; repetir las estrategias de álgebra densa implicaría una gran cantidad de cálculos inútiles al operar con ceros.

A diferencia del caso denso, el cómo almacenar matrices dispersas es un problema abierto y que está estrictamente relacionado con el patrón de matriz con el que se trabaja y la operación que se desea computar. A lo largo del tiempo han surgido distintos formatos de almacenamiento que buscan a la vez no almacenar los coeficientes con valor cero y tener patrones de acceso a datos que permitan implementaciones eficientes de las operaciones de álgebra. En otras palabras, la multiplicidad de factores a considerar (ahorro de memoria, desempeño de las operaciones, el patrón de dispersión de la matriz, características subyacentes del hardware en el que se ejecuta, entre otros) hace que no exista un formato de almacenamiento que sea mejor que los otros para todos los casos (ni todas las plataformas de hardware).

En este sentido, existen dos grandes enfoques. Por un lado, hay enfoques generalistas que buscan funcionar bien en un amplio abanico de matrices y operaciones en base a no explotar características particulares del patrón de

<sup>&</sup>lt;sup>2</sup>Notación tipo C (o 0-based), en FORTRAN (1-based) sería  $(i-1) \times m + j$

dispersión de las matrices en cuestión. En el otro extremo, es posible optimizar la estrategia de almacenamiento para aplicaciones o dispositivos específicos a costa de no ser transferibles a otros casos de uso.

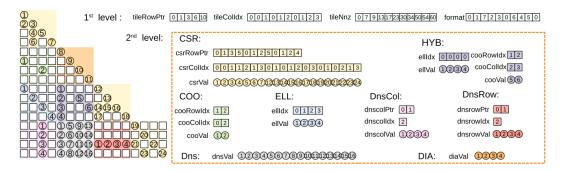

#### A. Formato de Coordenadas (COO)

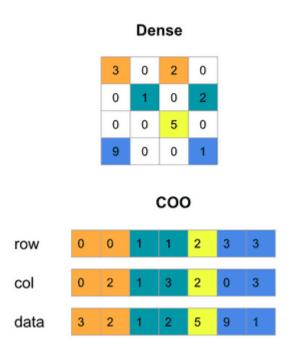

Quizá la estrategia más intuitiva entre las estrategias generalistas es el formato de coordenadas (COO). Este formato no almacena los ceros y mantiene los coeficientes en un arreglo unidimensional. Al no almacenar todos los coeficientes, es necesario asociar a cada uno los índices de fila y columna de manera explícita utilizando dos arreglos extra. En resumen el formato representa a una matriz como tres arreglos unidimensionales: (data, row, col). Los dos últimos son arreglos de enteros que mantienen los índices de fila y columna respectivamente, mientras que el primero guarda los coeficientes distintos a cero, generalmente en punto flotante. Un esquema con una matriz de ejemplo puede verse en la Figura 2.2. Esta estrategia tiene dos grandes problemas. El primero es que se pierde la regularidad de los datos. Si se compara con el acceso directo que se tiene en las matrices densas se pasa de un acceso en O(1) a uno  $O(nnz)^3$  o, en caso de que esté ordenada O(log(nnz)). El segundo problema se muestra en la Figura 2.2 en donde los vectores de fila o columna se presentan entradas repetidas. En este caso, como los elementos están ordenados por fila, las primeras dos entradas guardan información repetida y lo mismo sucede con las últimas dos. Aunque se logra una importante reducción de memoria si se compara con la estrategia densa, si se utiliza punto flotante de doble precisión para los coeficientes distintos de cero y 4 bytes para almacenar los enteros, el 50% de la memoria utilizada por COO es un sobrecosto de almacenar los índices, algo que en rutinas acotadas por memoria (como muchas operaciones de álgebra lineal dispersa) es un claro problema.

La reducción del *overhead* es una línea que ha motivado varios esfuerzos. Dang et al. propusieron el formato Sliced Coordinate format (SCOO) [28, 29] que subdivide la matriz en partes llamadas slices. Por otro lado Yan et al. propusieron el formato Block-based Compressed Common Coordinate (BC-COO) [30] que divide la matriz en bloques y luego almacena estos bloques utilizando COO lo que genera una reducción del sobrecosto de índices por elemento.

<sup>&</sup>lt;sup>3</sup>Número de no-ceros en la matriz.

**Figura 2.2:** Esquema del formato Coordinate (COO) para una matriz de ejemplo. Extraído de [1].

#### B. Compressed Sparse Row (CSR)

El repetimiento de información en el vector de índices de fila en COO motiva el formato comprimido por fila o Compressed Sparse Row (CSR) [31]. CSR es uno de los formatos más utilizados en la práctica y, al igual que COO, sigue un enfoque generalista. Este formato sigue una idea similar a COO, ordenando los elementos según su índice de fila. Los dos primeros vectores, val y col idx, son exactamente iguales que en COO y mantienen el valor del coeficiente e índice de columna respectivamente. Por el contrario, para eliminar la redundancia mencionada anteriormente, el tercer vector row ptr mantiene el índice del primer valor de cada fila en los otros dos vectores. Es decir, el elemento i del vector row\_ptr es el índice del primer valor en data y col correspondiente a la fila i. Un ejemplo con la misma matriz se puede ver en la Figura 2.3. Esta estrategia logra una mayor compresión que COO ya que, para almacenar una matriz cuadrada de dimensión n con nnz coeficientes distintos de cero, en lugar de utilizar  $16 \times nnz$  bytes, requiere  $12 \times nnz + 4 \times n$  bytes. Este ahorro de memoria impacta directamente en la eficiencia de muchas rutinas de álgebra dispersa clasificados como memory bound. El ahorro aumenta cuanto mayor sea la cantidad de no-ceros promedio por fila. Por otro lado, CSR agrega un nivel de indirección, algo que genera problemas especialmente cuando se quiere acceder por columna. En estos casos, dado que los valores no están contiguos en memoria en el peor de los casos puede recorrerse todo el arreglo val. Adicionalmente, si se quiere acceder a una entrada específica primero debe accederse al vector  $row\_ptr$  y, una vez que se tiene el puntero a donde comienza la fila, se hace una búsqueda lineal por el índice de columna.

Al ser tan difundido CSR tiene muchas optimizaciones para distintas áreas. Por ejemplo, Feng et al. propusieron el formato SIC [32] que combina filas para optimizar la operación SpMV. Para esto agrupa de a c filas y alterna los elementos de éstas permitiendo un mejor acceso a memoria en las plataformas de hardware utilizadas. Cuando se utiliza un parámetro c que no es múltiplo de n se debe hacer  $zero\ padding$  al final. Otra estrategia en esta línea es el Compressed Multirow Storage format (CMRS) [33] de Koza et al. que también sigue una idea de agrupar las filas en una estructura que llaman strip. La ventaja de esta estrategia es que no usa  $zero\ padding$  ya que el strip no tiene un tamaño fijo.

**Figura 2.3:** Esquema del formato Compressed Sparse Row (CSR) para una matriz de ejemplo. Extraído de [1].

Por último, CSC es un formato análogo a CSR, excepto que agrupa los noceros de la matriz por columnas y comprime el vector de índices de columnas en lugar del vector de índices de fila.

#### C. ELLPACK-ITPAK (ELL)

Otra estrategia, que no tiene un enfoque tan generalista, es el formato ELLPACK-ITPAK (ELL). El formato almacena una matriz de tamaño  $m \times n$  en un par de arreglos de tamaño  $c \times n$  donde:

$$c = \max_{0 \le j < m} \{ nnz(j) \}, \tag{2.1}$$

y nnz(j) es el número de elementos distintos a cero en la fila j. Esta estrategia busca regularizar la estructura a efectos de mejorar el rendimiento de distintas operaciones, ya que el acceso a los datos es similar al utilizado en álgebra densa. Como se verá más adelante en la tesis, esta técnica puede ser especialmente beneficiosa en GPUs NVIDIA para mejorar el acceso a memoria en operaciones como la SpMV.

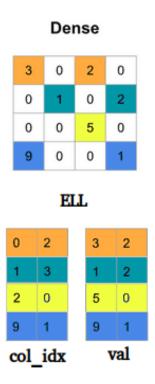

El primer arreglo (val) mantiene los coeficientes de cada fila mientras que el otro (col) guarda los dos índices de columna. Como el objetivo es alinear los datos y generar que el índice de fila esté implícito las filas que tienen menos de c elementos son rellenadas con 0s al final en ambos arreglos. Al igual que en CSR los valores de uno y otro arreglo están relacionados por la posición en memoria, es decir que los elementos de la posición i en col y val tienen los índices de columna y valor del mismo coeficiente. Continuando con el mismo ejemplo, en la Figura 2.4 se muestra el formato ELL aplicada a la misma matriz de la Figura 2.2.

Es evidente que ELL tiene buenos resultados en casos, como el del ejemplo, donde la cantidad de no-ceros entre las distintas filas es similar. Por el contrario, en los casos de matrices que tienen unas pocas filas mucho más grandes que el resto el sobrecosto del *zero padding* se hace prohibitivo.

La poca adaptabilidad de ELL ha motivado varios trabajos. Una primera idea es el Sliced-Ell (SELL-C) [34] que divide la matriz en subpartes o slices para las que calcula un  $c_i$  local y el zero padding se hace hasta ese número y no hasta el c global. Esto reduce el número de ceros explícitos que se necesita guardar. Una mejora a SELL-C fue propuesta por Barbieri et al. quienes aplicaron reordenamientos previo al fraccionamiento y propusieron el formato hacked-ELL (HLL) [35]. Otra modificación (o generalización) a SELL-C fue propuesta por Kreutzer et al. [36]. Finalmente, Antz et al. propusieron el for-

Figura 2.4: Esquema del formato ELL para una matriz de ejemplo. Extraído y adaptado de [1]

mato Sliced ELLPACK with Padding (SELL-P) [37] que mejora el acceso a memoria de SELL-C. Este formato introduce *padding* adicional para permitir que la longitud de cada *slice* sea múltiplo del tamaño de *warp* permitiendo acceso alineados a memoria.

Para reducir debilidades de algún formato específico es común intentar combinar formatos complementarios. Un ejemplo en esta línea es el formato HYB [38] propuesto por Bell y Garland que combina ELL y COO. En concreto se elige un valor k tal que 2/3 de las filas sean más cortas que k y se toma c = k. Por el contrario, para las filas más largas que k los últimos elementos son guardados en formato COO.

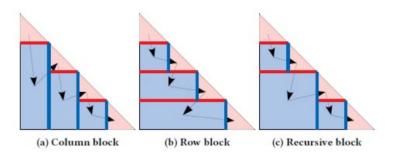

#### D. Formatos a bloques

Otra línea de trabajo popular para reducir el sobrecosto de almacenar los índices explícitamente es el uso de formatos a bloques. La idea general consiste en subdividir la matriz en bloques regulares y tratarlos como unidades de una matriz de bloques almacenada en un formato de almacenamiento disperso. Cada bloque, a su vez, se almacena en un formato denso (incluyendo los ceros

que contenga) o en un formato que permita acceder a sus elementos con un menor costo de almacenamiento de índices. Los formatos que utilizan esta premisa tienen buen rendimiento en matrices que tienen los coeficientes no-cero agrupados en ciertas partes de la matriz y muchas áreas sin ningún elemento. Por el contrario, si los coeficientes no-cero se encuentran repartidos de manera más equitativa a lo largo de la matriz el costo de almacenar ceros de manera explícita compensará la ganancias en los índices. Algunas ideas en esta línea fueron presentadas en los apartados anteriores, a continuación se presentan otros trabajos que usan esta estrategia.

Weber et al. propusieron BIN-CSR, un formato que agrupa las filas en bloques que se almacenan en ELL [39]. El formato funciona bien si el largo promedio de las filas de un mismo bin (grupo de filas) es similar al máximo largo. Por otro lado, Yan et al. presentaron el formato Block-based Compressed Common Coordinate [30]. El formato usa la idea de COO a nivel de bloques. Otra estrategia en este sentido es BCSR [40] que fue propuesto por Choi et al. en 2010. Similar al formato anterior aplica CSR a la matriz de bloques.

La revisión que se presenta en en este apartado no pretende ser un estado del arte exhaustivo de formatos de almacenamiento sino que busca explicar algunas de las propuestas más relevantes y que guardan relación con el trabajo. Existen distintos formatos de almacenamiento que buscan explotar distintas características específicas de un subconjunto de matrices. En esta línea, se han propuesto formatos como DIA o JAD [41] enfocados en matrices con estructuras diagonales. Una revisión más detallada se puede encontrar en [42].

# 2.2. Unidades de Procesamiento Gráfico (GPU)

Las unidades de procesamiento gráfico son una de las arquitecturas de hardware más utilizadas en la última década en el área de la computación de alto rendimiento (HPC por sus siglas en inglés -High Performance Computing-). El desarrollo de estos dispositivos, compuestos por una gran cantidad de procesadores capaces de ejecutar un elevado número de cálculos de forma paralela, fue impulsado, inicialmente, por la industria de los videojuegos. A diferencia de lo que ocurre con las CPU la gran mayoría de los transistores de una GPU son dedicados a cómputo en lugar de otras tareas (predicción de branches, cache de datos, etc.). Esta capacidad de cómputo paralelo y su relativamente bajo costo económico en comparación con otras plataformas de HPC propiciaron que las GPUs se comenzaran a adoptar para el cómputo de propósito general, es decir, tareas no relacionadas con el despliegue de gráficos en la pantalla.

Originalmente, hacer cómputo general en GPU tenía una gran dificultad, ya que se debía mapear las implementaciones a operaciones definidas en el pipeline gráfico [43]. Esta situación generaba que solamente pequeños grupos de expertos fueran capaces de sacar provecho de la arquitectura de las GPUs. En el año 2006, NVIDIA presentó la arquitectura CUDA (Arquitectura Unificada de Dispositivos de Cómputo por sus siglas en inglés) que permitió desarrollar rutinas de cómputo general en GPU independientemente de las primitivas de pipeline gráfico. CUDA es a la vez una arquitectura de cómputo paralelo y cuenta con una API que permite desarrollar rutinas de cómputo general que se ejecuten en tarjetas gráficas de NVIDIA utilizando una variación del lengua-je C (CUDA C). Esto motivó su adopción masiva por parte de la comunidad de cómputo científico. NVIDIA presentó su paradigma SIMT (Single Instruction Multiple Thread con puntos en común con el SIMD de la taxonomía de Flynn [44]) para describir la arquitectura de estos dispositivos.

A nivel de hardware, los núcleos de cómputo de las GPUs se organizan en un conjunto de *Streaming Multiprocessors* (SM). Los SM están compuestos por un grupo de procesadores que comparten registros y distintas memorias (cache L1, memoria compartida, cache constante y cache de texturas). Dependiendo de la arquitectura, cuentan con uno o más warp scheduler<sup>4</sup> Los SMs se agrupan en GPU Processing Clusters (GPCs). Estos son, básicamente, un conjunto de Texture Processing Clusters (parejas de SMs, no tienen una correspondencia con el modelo de programación de CUDA) más una raster engine (una unidad responsable de convertir gráficos vectoriales -definidos por ecuaciones matemáticas- en imágenes compuestas de píxeles). Toda esta estructura es transparente al programador y, por lo tanto, con el correr de las diferentes arquitecturas NVIDIA ha ido variando tanto la cantidad de procesadores por SM como la cantidad de SMs por GPC. Por lo anterior, no existen números generales que se mantengan a lo largo del tiempo, como sí existen en algunos agrupamientos a nivel de software como el warp <sup>5</sup>.

$<sup>^4</sup>$ Unidad que gestiona la ejecución de un warp como una unidad aunque ejecute en más de un ciclo de reloj. Similar a un program counter en CPU pero con la complejidad inherente del paralelismo.

$<sup>^{5}</sup>$ En CUDA, un warp es el conjunto básico de ejecución: 32 hilos que ejecutan de manera

Con respecto a la memoria, todas las tarjetas cuentan con una memoria RAM llamada memoria global compartida por todos los SM y cuya latencia es alta, ya que es una memoria off-chip. Para el manejo de esta memoria CUDA brinda ciertas funciones como cudaMalloc, cudaFree y cudaMemcpy para reservar, liberar y copiar memoria respectivamente. También off-chip se cuenta con las memorias constante y de texturas, ambas son de solo lectura, es decir, solo pueden ser escritas por el programa que ejecuta en la CPU. Pueden ser utilizadas para almacenar parámetros que vayan a ser utilizados en muchas ejecuciones. Finalmente, se cuenta con una caché L2, global para todas las SM.

Un segundo nivel en la jerarquía de memoria es la memoria compartida. Esta memoria es interna de cada SM y, al ser *on-chip*, tiene mucho mayor velocidad y ancho de banda que las memorias *off-chip*. La memoria compartida toma su nombre del hecho de que todos los hilos que se ejecutan en la misma SM tendrán acceso a ella y podrán cooperar utilizándola. A su vez, las SM cuentan con una caché L1 privada para cada una de ellas.

Finalmente, el último nivel de la jerarquía son los registros, que son la memoria más escasa y con menos latencia.

## 2.2.1. Arquitectura de dispositivo unificada de cómputo (CUDA)

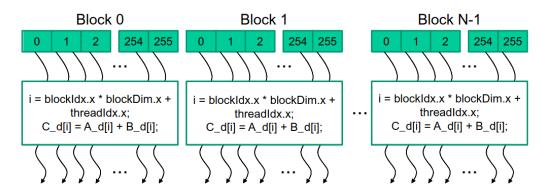

Los programas en CUDA cuentan con dos partes definidas: el código que ejecuta en la CPU (también llamado código host) y los kernels que ejecuta en la GPU (código device). Generalmente los kernels son invocados por código host, por ejemplo un main en CPU. Los kernels se definen mediante la directiva \_global\_. Al momento de invocar un kernel el código host explicita cuántos hilos (y con qué organización) ejecutarán dicha rutina, algo conocido popularmente como la grilla de ejecución. La grilla se organiza como un arreglo tridimensional de agrupaciones de hilos llamadas bloques. Estos bloques también son tridimensionales y están compuestos por hasta 1024 hilos. Finalmente, los hilos se agrupan en conjuntos de 32 hilos llamados warps.

Notar que los *kernels* son ejecutados por todos los hilos en paralelo; la diferencia de comportamiento entre los hilos se debe al uso de sus identificadores para acceder a memoria o evaluar *branches* lógicas. Por lo anterior, CUDA es una instancia específica del paradigma de programación de siste-

colaborativa.

mas paralelos SPMD (Un Programa Múltiples Datos por sus siglas en inglés) [45]. Esta instancia, como se dijo anteriormente, es conocida como  $Single\ Program\ Multiple\ Threads$  (SPMT) La cantidad y organización de los hilos que ejecutan un kernel se define al momento de la invocación, poniendo  $\ll GridDims, BlockDims, Ns \gg$  entre el nombre de la función y la lista de parámetros. La variable GridDims es de tipo  $dim3^6$  y se utiliza para especificar el tamaño de la grilla en bloques en las tres dimensiones (GridDims.x, GridDims.y, GridDims.z). La variable BlockDims es análoga para el tamaño del bloque en hilos.