# El Procesamiento Paralelo, Enfoque Cualitativo y Simulación

Leslie Murray<sup>†</sup>

Escuela de Ingeniería Electrónica Universidad Nacional de Rosario Argentina

Mayo 26, 2000.

#### Resumen

El presente trabajo constituye un material de apoyo en la introducción de ciertos conceptos básicos del procesamiento paralelo y afines. Es de interés que las ideas aquí vertidas resulten de aplicación práctica en proyectos interdisciplinarios relacionando fundamentalmente las áreas de Computación y Electrónica Digital. He concentrado la atención particularmente en dos de esos aspectos que resultan característicos y que constituyen parte de la esencia misma del mecanismo de ejecución simultánea de programas dentro de una misma máquina; son ellos: 1) La forma en que se organiza la memoria del sistema y 2) Los métodos a través de los cuales se garantiza la ejecución sincronizada de los diferentes procesos. Se abordan luego temas relacionados con los dos simuladores de arquitecturas de procesamiento paralelo (Limes y MulSim) utilizados para implementar y analizar algunas de las ideas anteriores, se comentan los fundamentos de su funcionamiento y su modo de uso con vistas a la realización de una serie de ensayos, cosa que se hace en último lugar.

## 1. Introducción

En 1966 según algunos, en 1972 según otros, Flynn estableció una clasificación según la cual todo sistema de cómputo pertenece a una de las siguientes cuatro categorías: **SISD** (*Single Instruction stream - Single Data stream*), **SIMD** (*Single Instruction stream - Multiple Data stream*), **MISD** (*Multiple Instruction stream - Multiple Data stream*). A la categoría SISD corresponde el modelo de computador tradicional (Von Neumann), en el que más allá de las variantes, se lleva acabo un procesamiento secuencial mediante la ejecución de una única instrucción sobre un único dato por vez (ej. cargar el contenido de una dirección de memoria en un acumulador, sumar 1 al contenido de un registro, etc.).

Dentro del tipo SIMD se consideran los sistemas que a partir de una única instrucción son capaces de procesar un conjunto o array de datos en forma simultánea, con la particularidad de ejecutar la misma instrucción sobre cada uno de sus elementos. Estos sistemas se componen de varias unidades funcionales idénticas (Unidades Aritmético-Lógicas, Registros de Direcciones de Memoria, etc.) comandadas todas ellas desde una única unidad de control encargada de recibir y procesar cada instrucción a ejecutar. Podría considerarse que, aunque en forma restringida, esta arquitectura incorpora en cierta medida el paralelismo desde el momento que es capaz de ejecutar "algunas tareas" (no "cualquier tarea") en forma simultánea, concretamente puede realizar N operaciones O, sobre N datos D, al mismo tiempo. En rigor no se puede

<sup>†</sup> Este informe, realizado en el marco de mi programa de Maestría en Informática, PEDECIBA, Facultad de Ingeniería, Universidad de la República, Uruguay, fue aportado como material de apoyo a un curso de la Cátedra "Arquitectura y Diseño de Computadoras" de la Facultad de Ciencias Exactas, Ingeniería y Agrimensura, Universidad Nacional de Rosario, Argentina. Un especial agradecimiento a los Ingenieros Sergio Geninatti y Santiago E. Roatta, por la colaboración y orientación recibida.

concebir una máquina cuyo modo de operación sea exclusivamente SIMD dado que es imposible pensar en tareas sobre segmentos de datos tales que absolutamente todos tengan aspecto vectorial. Para que esta modalidad pueda ser implementada, la arquitectura correspondiente deberá combinar necesariamente las prestaciones SIMD con las SISD.

La categoría MISD corresponde a configuraciones en las que un tren de unidades de procesamiento se surte por uno de sus extremos de un dato extraído de memoria y devuelve un resultado a la misma memoria por el extremo opuesto, en tanto cada unidad del tren toma por entrada al dato procesado por la unidad anterior y da por salida el que será tomado como entrada por la unidad siguiente. La característica MI está en el hecho de que cada unidad de procesamiento va ejecutando una operación distinta sobre un único dato (SD) que va avanzando hasta convertirse en el resultado.

MIMD es un modelo en el cual el sistema puede considerarse de alguna forma particionado en unidades con capacidad de, 1) Desarrollar su propio cómputo y 2) Comunicarse con las demás; de modo que al ejecutar cada una de ellas un determinado flujo de instrucciones (SI) sobre su propio flujo de datos (SD) se logra que en conjunto, múltiples flujos de instrucciones (MI) actúen sobre otros tantos flujos de datos

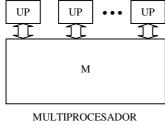

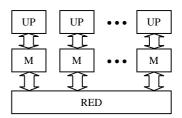

SISD constituye, como ya se dijo, el modelo clásico de arquitectura de computadoras en el que se basaron los diseños a lo largo de muchos años. En procura de lograr aumentos de performance, la producción de máquinas comerciales ha ido incorporando elementos de los demás modelos. En mayor medida SIMD y en menor MISD sirven al diseño de computadores de propósito específico pero no de equipos de distribución masiva, en tanto la última categoría MIMD constituye no sólo la más ambiciosa combinación posible de las dos variables (Instruction stream - Data stream) sino el fundamento mismo del procesamiento paralelo en su expresión más completa. Para Kai Hwang [Advanced Computer Architecture - p.11] "...sistemas de cómputo paralelo son aquellos capaces de ejecutar programas en el modo MIMD...". Estos sistemas a su vez pueden clasificarse en dos grandes categorías, los Multiprocesadores o sistemas de memoria compartida en los cuales la comunicación entre las distintas unidades se realiza, en forma implícita a través de variables compartidas dentro de una única memoria principal y los Multicomputadores o sistemas de memoria distribuida en los que la comunicación explícita entre unidades se realiza a través de una Red de paso de mensajes y donde cada unidad de procesamiento opera sobre su propia memoria.

(Memoria Compartida)

MULTICOMPUTADOR (Memoria Distribuida)

El mecanismo de paso de mensajes es el que permite a los procesos de un Multicomputador correr en forma integrada, coherente y sincronizada a fin de que la ejecución de cada uno resulte una cooperación con la ejecución global de una aplicación que, en pos de obtener un mejor rendimiento, haya sido distribuida entre las distintas unidades. Este paradigma se apoya en dos operaciones básicas, una para enviar mensajes, SEND y otra para recibirlos, RECEIVE. La idea es que cualquiera sea la topología de la red que de soporte al paso de los mensajes se establezcan canales a través de los cuales dos procesos P y Q puedan intercambiar información, por ejemplo del siguiente modo: SEND(P,m); RECEIVE(Q,m). En este caso el proceso O envía el mensaje m al proceso P mediante la emisión, a través del canal establecido, de la sentencia SEND dirigida explícitamente al proceso P el cual recibe el mensaje m del proceso Q y acusa recibo de él, a modo de confirmación, mediante la emisión a través del mismo canal de la sentencia RECEIVE en la que especifica el destinatario de la misma (no de m), o sea Q. Este tipo de comunicación implica el establecimiento de un canal (en tiempo y espacio) entre procesos para lo cual ambos deben estar simultáneamente en condiciones de comunicarse, de ahí el nombre de sincrónico. Su contrapartida es el modo asincrónico en el que la comunicación se realiza a través de buffers que actúan como buzones de correo. En este caso el proceso que envía el mensaje se despreocupa respecto a sí el destinatario está o no en condiciones de recibirlo. No obstante las demoras pueden sobrevenir mientras el proceso que hubiera enviado un mensaje no reciba la confirmación departe del proceso que lo hubiese recibido. Los mensajes pueden ser datos, información de sincronización, señales de interrupción, etc.

En los Multiprocesadores la implementación y ejecución de procesos paralelos difiere esencialmente del paso de mensajes ya que contempla una única forma de comunicación entre ellos, bastante más restringida pero por cierto mucho más rápida, materializada a través de lecturas/escrituras de posiciones compartidas de memoria en las que se alojen variables reconocidas por todos los procesos o sea de carácter global. Es éste modelo de computador paralelo el que vamos a abordar con mayor detalle, tanto que desde aquí y hasta el final del presente trabajo toda mención a sistema de cómputo/computador de procesamiento paralelo será implícitamente una referencia a un Multiprocesador.

He hecho alusión a memoria "compartida" y "distribuida" porque es la terminología habitualmente utilizada para clasificar los sistemas de memoria de Multiprocesadores y Multicomputadores, pero de hecho no se trata de calificativos que representen el opuesto uno del otro. Lo contrario de compartido es privado y esa es la clasificación que más apropiadamente describiría la situación. Que las CPUs direccionen todas el mismo espacio de memoria o que cada una tenga su propio juego de direcciones es lo que pretenden señalar las definiciones de Multiprocesador y Multicomputador y no si la memoria es distribuida o centralizada, porque ello tiene que ver con su ubicación física, aunque en general las compartidas estén centralizadas y las privadas distribuidas. Hago esta aclaración no sólo porque implica definir las cosas con propiedad sino porque además refuerza el concepto de lo que se debe entender por cada uno de los dos modelos.

Hay argumentos variados a favor de uno y otro; para los defensores de Multicomputadores los sistemas de memoria compartida admiten un tráfico limitado sin importar cuanta memoria caché utilicen (ver Jerarquía de Memoria) debiendo por lo tanto resultar acotado el número de procesadores. En favor de Multiprocesadores se pregona que sólo se justifica distribuir la memoria si el problema es suficientemente paralelizable como para demandar un gran número procesadores y también que la memoria distribuida incrementa la dificultad de programación ya que el programador o el compilador deben decidir cómo organizar los datos en los módulos de memoria de modo de reducir la comunicación. Algo que se puede afirmar sin temor a equivocarse es que el tipo de aplicación que se pretenda ejecutar tendrá una gravitación importante en el modelo de computador paralelo que pudiera resultar más apropiado y por otro lado que las dificultades que presenta la programación paralela son tales que se va a requerir no sólo gran entrenamiento y preparación de los futuros programadores en ese sentido sino una extraordinaria adaptación de los compiladores para poder explotar todas las ventajas del paralelismo.

## 2. Jerarquía de Memoria

### 2.1. Introducción

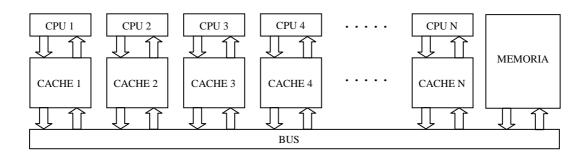

Según Hennessy & Patterson "...el rendimiento de un programa en multiprocesador depende de la eficiencia del sistema para compartir los datos...". Vamos a abordar la metodología a través de la cual un equipo dotado de N procesadores (CPU), cada uno con su respectiva memoria cache (MC), y una única memoria principal (MP) administra esos recursos a fin de lograr que las aplicaciones corran "repartidas" entre las N unidades CPU-MC, compartiendo un único espacio de datos en la MP. Para ello analizaremos en primer término los distintos modos de operación de cada una de las N unidades CPU-MC-MP es decir las pautas que rigen ese modelo (jerarquía de memoria), tal como si se tratara de una unidad monoprocesadora.

Aunque este criterio en algunos casos pueda sufrir modificaciones, una MC guardará coherencia con su correspondiente MP siempre que, considerando el espacio de cualquiera de las dos memorias dividido en una cantidad entera bloques o líneas, toda línea que esté presente en la MC esté también en la MP. Los bloques (o líneas) se irán subiendo desde la MP hacia la MC a medida que vayan siendo requeridos por la CPU, explotándose así los principios de localidad temporal y espacial que dicen que los elementos referenciados alguna vez por un programa tenderán a ser referenciados nuevamente "pronto" y que al referenciarse un elemento determinado cobran alta probabilidad de ser referenciados los ubicados físicamente "próximos" al mismo. Así es que toda referencia a memoria realizada por la CPU será dirigida primeramente a la MC, sea esta una lectura o una escritura. Si se intenta leer un dato y la línea que lo contiene está en la MC de allí se toma y eso constituye un éxito de lectura (read hit), caso contrario se produce un fallo de lectura (read miss). (Veremos más adelante situaciones en las que se producen fallos de lectura aún cuando la línea esté en la MC). Ante un fallo de lectura el recurso inevitable y costoso, de ahí que deba evitarse, es llevar el dato a la CPU desde la MP, previa escritura de la línea que lo contiene en la MC (recordar principios de localidad). ¿Qué sucede en las escrituras?, cuando la CPU intenta escribir en una dirección de memoria (dato), también procura hacerlo primeramente en la MC y lo hace si la línea que contiene esa dirección ha sido previamente subida a la misma, eso sería un éxito de escritura (write hit). Acto seguido existen dos posibilidades, bajar inmediatamente la línea modificada a la MP, escritura directa (write through) o esperar y no bajarla hasta que algún otro proceso intente borrarla de la MC, post escritura (write back). ¿Cuándo y por qué habría de ser borrada una línea de la MC? en términos gruesos la MP es voluminosa y lenta mientras que la MC es reducida y rápida, se procura entonces que la MC albergue solamente los datos frecuentemente referenciados y si la política de ubicación de líneas en ella es buena, esos datos permanecerán en MC durante un tiempo razonablemente prolongado, pero la importante diferencia de tamaño entre ambas memorias hace que permanentemente estén subiendo líneas desde la MP y que consecuentemente algunas de la MC vayan siendo reemplazadas. Básicamente hay tres políticas de reemplazo para cuando una línea subida desde MP debe alojarse en MC, totalmente asociativa, si la línea puede ubicarse en cualquier posición de la MC, correspondencia directa, si la línea subida sólo puede ir a una única posición (por ejemplo a través de una función de hashing aplicada a la dirección original) y asociativa por conjuntos, que sería una situación intermedia en la que la línea subida puede ir a cualquier posición de un conjunto perfectamente determinado. Recordando que estábamos intentando escribir sobre una posición de memoria, queda por último la posibilidad de que la línea sobre la que se intente escribir no esté en la MC, eso es un fallo de escritura (write miss). En este caso la CPU puede proceder de dos formas, bajar hasta la MP y escribir directamente sobre ella, acto seguido o bien subir inmediatamente la línea modificada a la MC, modalidad conocida como "ubicar en escritura" o bien no hacerlo, "no ubicar en escritura"; o bien la MC fallada puede pedir primeramente la línea a la MP y luego escribirla (ya se verá la utilidad de esta opción en el protocolo de Berkeley en el que la línea solicitada podría obtenerse de otra MC y no necesariamente de MP).

|                                 | Memoria Caché          | Memoria Principal                 |

|---------------------------------|------------------------|-----------------------------------|

| Tamaño Total                    | 1 a 256 Kb             | 4 a 2.048 Mb                      |

| Tamaño de Bloque                | 4 a 128 bytes          | 512 a 8.192 bytes                 |

| Tiempo de Acierto               | 1 a 4 ciclos de reloj  | 1 a 10 ciclos de reloj            |

| Penalización de Fallo [TA]+[TT] | 8 a 32 ciclos de reloj | 100.000 a 600.000 ciclos de reloj |

| Tiempo de Acceso [TA]           | 6 a 10 ciclos de reloj | 100.000 a 500.000 ciclos de reloj |

| Tiempo de Transferencia [TT]    | 2 a 22 ciclos de reloj | 10.000 a 100.000 ciclos de reloj  |

| Frecuencia de Fallos            | 1% a 20%               | 0,00001% a 0,001%                 |

Rangos de valores típicos de parámetros clave de una Jerarquía de memoria

## 2.2. Multiprocesadores

En un esquema monoprocesador con sólo una CPU, una MC y una MP, el problema de coherencia se resuelve entonces estableciendo reglas de acuerdo a las pautas que se acaban de comentar. La política a aplicar resulta simple y permite pocas variantes. Pero en una arquitectura multiprocesador, digamos de N unidades CPU-MC con sólo una MP, el problema de los accesos a memoria se complica y surge una enorme variedad de soluciones. Téngase en cuenta que en general sobre cada unidad estará corriendo un proceso distinto, aún cuando entre todos conformen una única aplicación, generándose entonces una competencia por el acceso a las posiciones de memoria que habrá que manejar estableciendo políticas que garanticen tanto la sincronización como la validez y coherencia de los datos leídos y escritos.

Una de las posibles arquitecturas para implementar la jerarquía de memoria en un esquema multiprocesador es la que se conoce como Memoria Compartida sobre Bus Común. Cada unidad CPU-MC avanzará en su cómputo tanto como le sea posible prescindiendo de las demás. Una unidad de control que no se muestra en la figura se encargará de la administración del bus permitiendo a cada MC volcar información cuando así lo solicite, atendiendo también los pedidos de acceso a memoria, mientras que un puerto especial de cada MC estará leyendo el bus permanentemente.

A diferencia de un sistema monoprocesador en el que la MC no tiene otro objetivo que acelerar el cómputo gracias a su tecnología de construcción, en sistemas multiprocesadores también tiene por finalidad distribuir, en la medida de lo posible, tanto datos como instrucciones entre las correspondientes unidades para evitar que la MP sea solicitada en forma alternada y continua por todas las CPUs, debiendo esperar cada una su turno mientras las demás van consiguiendo el acceso. Veamos esto con mas detalle en el siguiente ejemplo: imaginemos una MP (ideal) que permitiera accesos completos en sólo un ciclo de reloj. Esta solución neutralizaría la necesidad de MC en un sistema monoprocesador, nada podría haber más rápido que esta MP, pero ¿sucederá lo mismo en un sistema multiprocesador? Decididamente no, si se prescinde de las MC cada unidad verá reducida su velocidad de cómputo en un orden igual al número de unidades del sistema con relación a la velocidad a la que cada unidad monoprocesadora CPU-MC-MP es capaz de correr, velocidad a la cual una adecuada elección de MC podría acercar razonablemente al multiprocesador. (La no existencia de MC en un sistema multiprocesador debería independizar la velocidad de cómputo respecto a la cantidad de procesadores acercándola a la velocidad lograda con un único procesador o sea al sistema multitarea equivalente ya que las unidades no podrían trabajar simultáneamente. En la realidad esta tendencia se ve atenuada por la proporción de operaciones que la CPU realiza a nivel de registros, es decir independizada de la memoria).

Existen básicamente dos tipos de protocolo para mantener la coherencia entre los datos de MC y MP de Multiprocesadores (protocolos de coherencia cache), los basados en directorio, en los que cierta información sobre cada línea de la memoria se almacena en un espacio único (directorio o tabla) y los de espionaje (snoopy) en los que cada línea alojada en la MC contiene, junto con los datos, cierta información sobre esa línea (su validez, etc.) siendo esa información generada a partir de otra recogida mediante controladores de cada MC que al estar "espiando" (snooping) permanentemente el bus levantan información de interés cuando la detectan. Resumiendo, en los protocolos de directorio, el mismo alberga información del tipo: todas las cache que tienen copia de cada línea, la relación que existe entre el contenido de una línea de MC y su correspondiente en MP, etc., en tanto en los de espionaje toda esa información acompaña cada línea presente en la MC. A propósito, sería conveniente comentar la terminología empleada habitualmente para describir el estado de una línea de MC, VALIDA significa que tiene exactamente el mismo contenido que su correspondiente en MP, SUCIA que la información que contiene difiere de la que existe en su correspondiente en MP no obstante lo cual es válida (caso de post escritura en el que la línea de MC ha sufrido modificaciones por parte de la CPU pero todavía no ha sido desalojada) e INVALIDA cuando el contenido además de diferir del de su correspondiente en MP carece de validez.

Se puede percibir ya el objetivo de estos protocolos en el hecho de permitir a una CPU que en los accesos a memoria tenga exclusividad para escribir un objeto y que pueda disponer de la copia más actualizada al leer un objeto. Vamos a concentrarnos de aquí en más en los de tipo snoopy aclarando que las ideas son igualmente aplicables a los de directorio, salvo en la forma de gestionar la información sobre el estado de cada línea. Los problemas a resolver son del tipo: ¿qué deberán hacer todas las cache que tengan copia de una determinada línea cuando sobre alguna de ellas se haya protagonizado un fallo y haya sido necesario actualizarla?, ¿deberán actualizarla también?, ¿deberán invalidarla?, ... ¿qué deberá suceder cuando se escriba sobre una MC?, ... De aquí en más pasa a jugar un papel importante el modo de operación que tenga cada unidad CPU-MC-MP en cuanto a sí aplica escritura directa o post escritura, si ubica en escritura o si no lo hace, etc. y también todo lo que tenga que ver con las respuestas a las preguntas formuladas más arriba, generándose a partir de allí dos tipos de protocolo de espionaje: los de invalidación en escritura en los que cuando una CPU se dispone a escribir sobre su MC anuncia sobre el bus qué línea va a modificar para que todas las cache restantes chequeen si tienen o no esa línea y en caso afirmativo invaliden su contenido luego de lo cual se produce la escritura y los de difusión o actualización en escritura, en los que la CPU que va a escribir difunde sobre el bus no sólo la identificación de la línea a modificar sino también el nuevo dato, permitiendo a todas las MC que tengan esa línea, actualizarla. Habitualmente en la difusión en escritura los bloques se identifican como compartidos o privados según puedan existir copias en varias MC o en una sola; se suele aplicar en cada caso una modalidad distinta para difundir la información hacia las MC, en el caso de datos compartidos la mecánica es similar a la de escritura directa (write through) es decir la información se difunde ni bien es escrita en una de las MC mientras que para los datos privados se procede como en post escritura (write back), produciéndose la difusión sólo cuando una línea con información actualizada va a ser desalojada.

Como es de suponer la invalidación provocará una elevación en la tasa de fallos pero es un proceso muy rápido, en tanto la difusión es lenta pero tiende a mantener los fallos en un nivel bajo. También cabe observar que los datos fuertemente afectados de localidad para una unidad CPU-MC podrían no serlo para las demás por lo que de ningún modo está garantizada la utilidad de las actualizaciones en todos los casos. Existe una infinita variedad de combinaciones de: capacidad de MC y de MP, tamaño de línea, latencia de las memorias, etc., y además todos los programas tienen distinto comportamiento y por ende diferente

demanda de recursos. Como si todo esto fuera poco, en programas paralelos existe el componente adicional de la distribución de tareas (*scheduling*) entre las distintas unidades CPU-MC-MP lo que puede llegar a ocasionar variantes de performance para una misma aplicación en una misma arquitectura. Todos estos planteos contribuyen a señalar la simulación como casi único método viable para extraer conclusiones comparativas a partir de esta inmensa cantidad de variantes.

### 2.3. Protocolo de Invalidación basado en Post Escritura

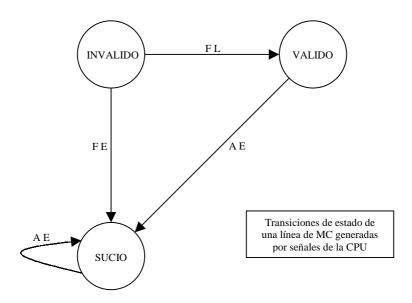

Vamos a presentar seguidamente un sencillo protocolo de coherencia cache de invalidación en escritura basado en post escritura:

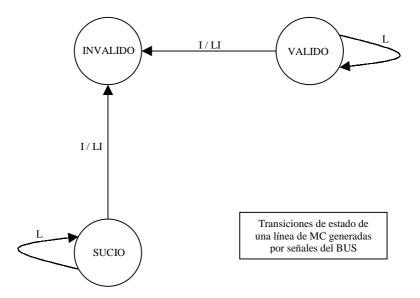

El diagrama de transición de estados finitos se explica por sí solo. Representa todas las posibles evoluciones del estado de una línea de MC. F y A indican fallo o acierto mientras que L y E, lectura y escritura. No hemos tomado en cuenta la entrada A L porque nunca produce cambio de estado.

Un rápido análisis muestra un hecho evidente, que todas las escrituras sean éstas provenientes de F o A llevan la línea al estado SUCIO mientras que las lecturas (recordemos que sólo consideramos fallos) la conducen al estado VALIDO. Esta mecánica guarda estrecha relación con el modo de post escritura de este protocolo. Al estado VALIDO se lo suele llamar también estado de SOLO LECTURA porque en él se permanece ante sucesivas lecturas, mientras que una escritura hace que se salga de él. Del mismo modo se acostumbra llamar LECTURA/ESCRITURA al estado SUCIO porque ante una sucesión de A sean éstos de lectura o de escritura no se produce conmutación.

Como se puede observar las señales de entrada al diagrama, es decir las que provocan los cambios de estado, son en todos los casos acciones de la CPU. Pero el estado de una línea de MC puede conmutar no sólo en respuesta a una acción de la CPU a la que pertenece, sino también a partir de señales de otras MC que reciba a través del bus, por ejemplo una orden de invalidación (recuérdese que hay un controlador por cada MC "espiando" el bus en procura de detectar señales que la tengan por destinataria). Es por eso que se acostumbra acompañar otro diagrama de transición de estados vinculado a estas señales simplemente por una cuestión de claridad porque en rigor un protocolo quedará completamente determinado mediante un único diagrama producto de la superposición de los dos que estamos presentando.

Hay tres posibles señales que una línea de MC puede detectar que otra MC le dirige a través del bus; L: lectura, cuando otra MC intenta leer su copia de esa línea, I: invalidación, cuando otra MC ordena la invalidación su copia de la línea y LI: lectura+invalidación, cuando se ordena llevar a cabo las dos tareas (las ordenes de invalidar son volcadas al bus sólo cuando una línea es escrita). En este protocolo informar que una copia ha sido leída en otra MC no presenta utilidad, lo que sucede es que todos los accesos son notificados al bus (sean estos lecturas o escrituras) siendo indispensable identificar el tipo de operación realizada.

A diferencia de este protocolo, uno de invalidación pero basado en escritura directa tendría sólo dos estados (VALIDO e INVALIDO), la aparición del tercer estado (SUCIO) es producto de la política de post escritura. El análisis sería similar, de hecho más simple.

En los protocolos de tipo *snoopy* el estado de cada línea, como ya se dijo, está representado por algunos bits que a ese fin se adicionan a la misma. Adecuando la lógica de un procesador es posible dar cualquier significado a esos bits haciendo que la coherencia sea garantizada por la política que cada uno considere más adecuada, generándose así una diversidad infinita de protocolos.

## 2.4. Protocolo de Berkeley

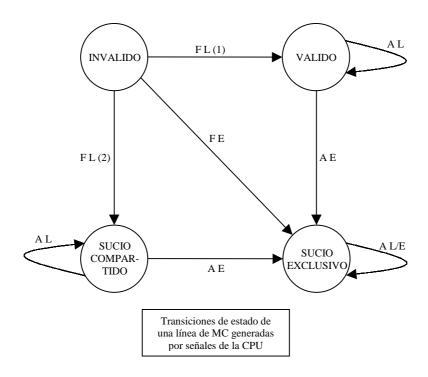

El protocolo de Berkeley, al igual que el protocolo elemental que se acaba de presentar, opera mediante invalidación en escritura y post escritura pero implementa dos mejoras importantes, producto de la descomposición del estado SUCIO en dos, capaces de representar cualidades muy útiles: la **propiedad** y la **exclusividad** sobre las líneas. La MC que tenga la propiedad sobre una línea será la encargada de asistir los pedidos de actualización de otras MC detectados sobre el bus.

En el arranque todas las líneas serán propiedad de la MP y a medida que la CPU las vaya escribiendo, la MC escrita irá adquiriendo la propiedad sobre la o las líneas nuevas y así sucesivamente, es decir la MC más recientemente actualizada será la propietaria de la línea modificada, resultando así no más de una propietaria por línea (recordar que se opera por invalidación).

Ante un fallo en cualquier MC, la propietaria de la línea sobre la que se produzca el fallo (si existe) se encargará de proveer la línea a la MC fallada, ahorrándole el costoso trabajo de ir a buscarla a MP. Obviamente esta asistencia entre cachés reduce notablemente el trafico MP-MC haciendo decrecer la penalización en aproximadamente un orden de magnitud.

Las líneas en estado VALIDO o INVALIDO no tienen "dueño", solamente determinan alguna forma de propiedad los estados SUCIOS; en ellos una línea puede pertenecer a una MC en forma exclusiva o compartida. Si sólo una MC cuenta con una línea, la propiedad será exclusiva, si alguna otra la posee la propiedad será compartida. La ventaja de que el estado indique el tipo de propiedad está en el hecho que cuando se escriben líneas de propiedad exclusiva no se vuelca al bus la señal de invalidación para las demás MC lográndose una disminución de tráfico en el bus.

Como se dijo, una línea de MC en estado SUCIO EXCLUSIVO aloja información actualizada, que no está presente en ninguna línea de ninguna otra MC y que difiere de su correspondiente línea en MP. El estado SUCIO COMPARTIDO indica que la información es actualizada y diferente de la correspondiente en MP pero que está en más de una MC.

Veamos dos cosas para cada uno de los cuatro estados: (a) por qué vía puede ser alcanzado y (b) cuales son las posibles alternativas para salir del mismo.

INVALIDO: (a) cuando la línea existe en la MC y detecta una señal de invalidación con su dirección en el bus. (b) ante un F L la línea o bien es subida desde MP y el estado pasado a VALIDO o bien es traída desde otra MC (la "dueña") y el estado pasado a SUCIO COMPARTIDO. Ante un F E lo más adecuado en este protocolo es primeramente pedir la línea, modificarla y luego escribirla en MC ¿por qué hacer esto en lugar de bajar hasta MP, escribirla y luego subirla hasta la MC invalidando las demás copias? por la sencilla razón que es muy factible, aunque no seguro, que exista otra MC en condiciones de asistir la lectura ahorrándose muy probablemente un acceso a MP. Por eso un F E lleva la línea a estado SUCIO EXCLUSIVO.

<u>VALIDO</u>: (a) toda vez que se produzca un F L (lo cual únicamente puede suceder en el estado INVALIDO) y que éste sea asistido desde MP y no desde otra MC. (b) Por supuesto que en este estado no se conciben fallos, los A L no afectarán el estado de la línea mientras que los A E la llevarán a SUCIO EXCLUSIVO (recordar criterio de post escritura).

<u>SUCIO EXCLUSIVO</u>: (a) desde los estados VALIDO e INVALIDO según lo visto en los ítems -b- de los dos puntos anteriores. (b) Sucesivos aciertos de L y/o E no harán cambiar de estado a la línea, mientras que fallos no son posibles en este estado. Luego es imposible salir de este estado, la única posibilidad de cambio está en el reemplazo de la línea.

<u>SUCIO COMPARTIDO</u>: (a) cuando hay un F L en una línea en estado INVALIDO y ésta es asistida por otra MC, luego de la asistencia tanto la asistida como la asistente van a quedar con la misma línea, por ende en el mismo estado, es decir el estado de la asistente, SUCIO COMPARTIDO. (b) En este estado no puede haber fallos, A L no lo modifican, sólo un A E porque le quita el carácter de COMPARTIDO para pasarlo a EXCLUSIVO.

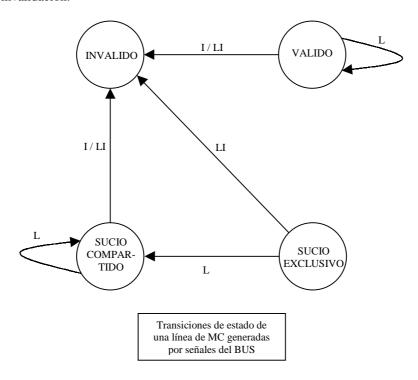

Esta es la forma de analizar el diagrama que de por sí es autoexplicativo y sobre el que también cabe la descomposición en dos según el origen de las señales consideradas, por lo que se muestra seguidamente la parte correspondiente a señales de entrada provenientes del bus. Aquí también hay tres posibles señales que una línea de MC puede detectar que otra MC le dirige a través del bus, recordemos; L: lectura, cuando otra MC intenta leer esa línea, I: invalidación, cuando otra MC ordena la invalidación de la línea y LI: lectura+invalidación, cuando se ordena llevar a cabo las dos tareas (las ordenes de invalidar son volcadas al bus sólo cuando una línea es escrita). Cabe recalcar una vez más que no estamos frente a un segundo diagrama de transición de estados sino a uno único descompuesto en dos para facilitar su interpretación, la forma de arribar a cada estado en este esquema es, obviamente, la misma que en el anterior. Sólo cabe comentar las transiciones posibles desde cada uno.

<u>INVALIDO</u>: en este estado una línea no puede ser destinataria de ninguna señal por parte de otra MC pues la información que contiene no es de utilidad para ser leída por nadie ni tiene sentido de ser invalidada puesto que ya lo está.

<u>VALIDO</u>: si otra MC protagoniza un F L, pide a través del bus la línea y al existir la misma en estado VALIDO la lee quedando luego ambas en este estado. Pero si la otra MC ha sufrido un F E, también va a

pedir la línea al lugar dónde está en estado VALIDO, pero acto seguido tendrá que invalidar la línea leída porque la va a escribir dejándola en estado SUCIO EXCLUSIVO.

<u>SUCIO EXCLUSIVO</u>: en este estado nunca se puede recibir un pedido de invalidación porque SUCIO EXCLUSIVO implica la línea más actualizada de todo el sistema. Sólo tienen sentidos pedidos de L o LI.

<u>SUCIO COMPARTIDO</u>: Al igual que VALIDO, puede recibir cualquiera de las tres señales, permaneciendo sin cambio si se le hace una lectura y pasando a INVALIDO en cualquiera de las dos variantes de invalidación.

## 2.5. Otros protocolos

Como se dijo, existe una infinita diversidad de variantes para implementar las ideas expuestas hasta aquí bajo la forma de protocolos de coherencia caché. Vamos a comentar brevemente las ideas fundamentales de los más conocidos.

Protocolo de Illinois. Se basa en los mismos principios que el de Berkeley (invalidación en escritura basado en post escritura), extendiéndose algunos de los conceptos, por ejemplo el de propiedad, permitiendo la existencia de mas de un dueño para una única línea y estableciendo un orden de prioridad para que respetando ese orden cualquiera de los dueños asista un pedido de actualización de otra MC. También se procede no difundiendo señal de invalidación si la línea afectada no es compartida.

Protocolo Firefly. A diferencia de Berkeley e Illinois, Firefly es un protocolo de difusión en escritura por lo que no cuenta con estado INVALIDO ya que, prescindiendo del arranque, nunca una línea puede alcanzar ese estado. En cuanto a la asistencia entre MC maneja un criterio similar al de Illinois sólo que no se designa la unidad asistente de acuerdo a un orden de prioridad sino que permite que todas las MC en condiciones de asistir lo hagan simultáneamente. Si bien esto último redunda en una simplificación, ocasiona una elevación en el número de bloqueos de procesadores.

*Protocolo Dragon*. Así como Firefly lleva las ideas de Illinois al terreno de la difusión en escritura, Dragon hace lo propio con Berkeley. No tiene estado INVALIDO y retoma la idea de propiedad haciendo que sólo el dueño de una línea pueda asistir a otra MC y eventualmente la MP cuando no haya otro dueño.

No existe una definición terminante en cuanto a cual de las modalidades es mejor, sí invalidación o difusión. Esta cuestión está fuertemente influenciada por: la aplicación que se quiera ejecutar, la cantidad de procesadores, el criterio para la distribución de tareas entre los mismos, etc. Se han desarrollado por

eso modificaciones en la idea de recoger lo mejor de cada modalidad. Vamos a comentar dos políticas que pueden ser aplicadas para modificar las versiones clásicas de los protocolos presentados hasta ahora dando origen a sus versiones híbridas.

Read Broadcast (difusión de lectura). El punto débil de los protocolos de invalidación está en la alta tasa de fallos por invalidación, es decir fallos en los que incurre una CPU cuando al acceder a la línea buscada la encuentra pero ve que ha sido previamente invalidada por otra MC. El objetivo de este método es reducir esa tasa de fallos. Para ello procede de la siguiente manera: cuando una MC "detecta" que otra MC está leyendo una línea cuya copia posee en estado inválido, aprovecha para actualizarla, aún cuando de momento no la necesite. Esto constituye una especie de "difusión o actualización" no de escritura sino de lectura (read Broadcast) por lo que la aplicación de este método a protocolos de invalidación como Berkeley o Illinois da origen a sus respectivas versiones híbridas.

Snooping Competitivo. El punto débil de los protocolos de difusión es la excesiva utilización del bus y los consecuentes bloqueos de CPU debidos a actualizaciones innecesarias. Para solucionar este problema se propone lo siguiente: una línea de MC será invalidada luego de que haya sido actualizada un número "grande" de veces sin haber sido solicitada por la CPU. La forma de implementar esta idea es mediante el agregado de un contador por cada línea de MC de manera que cuando la CPU la referencie, el contador sea seteado a su máximo valor, con cada actualización el contador se decremente en uno y al llegar a cero la línea sea invalidada. En teoría Firefly y Dragon deberían tornarse más flexibles mediante este agregado que da origen a sus versiones híbridas. No obstante, al igual que en Read Broadcast, existe siempre una gran dependencia de factores externos que torna imposible determinar el mejor modelo, lo adecuado es ensayarlos, y como ya se anticipó nada mejor que simularlos, para determinar las condiciones bajo las cuales cada uno ofrece la mejor solución.

## 3. Sincronización

### 3.1. Introducción

Cuando un programa paralelo arranca, lo hace en una de las unidades CPU-MC-MP de la máquina multiprocesadora, tal como lo hacen los programas secuenciales en máquinas monoprocesadoras. De ahí en más los procesos que se van lanzando en distintas unidades quedan corriendo simultáneamente en tanto no se produzcan situaciones de conflicto. Mientras el cómputo de cada uno pueda evolucionar sólo mediante accesos a posiciones de memoria que no sean requeridas por más de una unidad a la vez, y mientras ningún tramo de proceso requiera la condición de no ser interrumpido, podríamos decir que los procesos no se "molestarán" entre sí y podrán evolucionar incluso hasta completarse. Al igual que en máquinas monoprocesadoras con Sistemas Operativos (SO) multitarea, en máquinas multiprocesadoras también existe la posibilidad de que se quieran correr más procesos que la cantidad total de CPUs, en cuyo caso aun cuando determinados procesos no se afecten mutuamente ni tengan problemas de sincronización, también podría darse la necesidad de interrumpirlos e incluso de removerlos (transitoriamente) de sus respectivas unidades. De manera que la "manipulación" de procesos en un sistema multiprocesador (lanzamiento, remoción, bloqueo, etc.) es muy similar a la de una máquina monoprocesadora con SO multitarea, con la única diferencia (en cuanto a sincronización se refiere) en la disponibilidad de CPUs para distribuir procesos y con la consecuente posibilidad, por supuesto, de que varios de ellos puedan efectivamente estar en ejecución simultáneamente.

El tema que vamos a abordar tiene que ver con la forma de evitar que uno o más procesos (en general corriendo en distintas unidades) se solapen en la escala de tiempo precisamente en segmentos que contengan demandas sobre los mismos recursos (por ejemplo la o las mismas variables globales, la misma unidad de Entrada/Salida, etc.). Un caso elemental de este tipo de conflicto lo constituye el intento simultáneo, por parte de más de una CPU, de acceder a la misma posición de MP.

En general, mediante mecanismos de hardware, cada vez que una CPU consigue el acceso a MP a través del bus, todas las demás ven bloqueada esa posibilidad. El bus actúa entonces como uno de los medios para a arbitrar sobre los múltiples intentos de acceder a la MP, al menos durante los ciclos que ese acceso lo mantiene ocupado. Esta es una facilidad que el hardware debe ofrecer inevitablemente ya que por ejemplo una memoria, del tipo que sea, ¡no puede ser direccionada por más de una dirección a la vez!. Ilustremos estas ideas mediante un ejemplo suponiendo que una CPU intenta incrementar en 1 el valor de una variable global residente en la MP. Hay procesadores cuyo lenguaje ensamblador cuenta con una única instrucción para esa tarea, lo cual ni remotamente significa que puede ser ejecutada en un ciclo, ni

en dos... Digamos que podría ser necesario para ello, por ejemplo, leer el valor almacenado, subirlo hasta un registro de la CPU, sumarle 1 y recién entonces procurar escribirlo en la misma posición desde la que fue leído. ¿Qué sucedería si otro proceso que hubiera conseguido el acceso a MP desde otra CPU leyera el valor a incrementar inmediatamente después de que lo haya hecho el proceso que lo iba a incrementar?, al decir "inmediatamente después" me refiero a "antes de que el incremento haya sido realizado", porque la CPU que intentaba incrementar tendrá la exclusividad sobre el bus para leer, perdiéndola luego al iniciar los cómputos siguientes e intentando recuperarla recién para escribir el valor incrementado. Aquí hay una cuestión importantísima a destacar, si el segundo proceso, el que sólo iba a leer, accede a la variable en un instante cronológicamente posterior a aquel en el que lo hizo el que intentaba incrementar, eso significa que precisamente en ese orden fueron "pensadas" ambas tareas por el programador (o por el compilador) y que por lo tanto el segundo proceso debería leer el valor incrementado de la variable. ¡No sucederá así por supuesto! a menos que se implemente algún mecanismo corrector.

Este ejemplo que pone de manifiesto un problema sobre una única instrucción, puede generalizarse a tramos completos de código. Estos tramos se denominan *Zona Crítica* (ZC) y pueden definirse de la siguiente manera: una ZC es un segmento de código que debe ser ejecutado por una única unidad a la vez y cuya ejecución una vez iniciada debe completarse sin interrupciones. Por supuesto y aunque no se mencione en la definición, queda claro que el carácter crítico va indivisiblemente ligado al hecho de que ese segmento de código ha de operar sobre recursos de carácter global, aunque ésta condición no sea excluyente; un programador podrá decidir proteger un tramo de programa dándole el carácter de ZC cualesquiera sean las características de los recursos requeridos por el mismo. Lo que debe quedar claro es que, en multiprocesadores, proteger una ZC no es sino darle a la CPU que la va a ejecutar la exclusividad sobre la MP durante los ciclos que le tome esa ejecución.

Este tipo de problema conduce a la necesidad de implementar algo así como mecanismos de protección y dado que para proteger una ZC de un proceso a veces es necesario detener otros (ya se verá cómo) hasta que haya sido ejecutada la ZC protegida, la resultante en la escala de tiempo es una especie de reacomodamiento relativo entre los procesos tendiente a garantizar el orden previsto por la programación. En esto consiste la sincronización.

## 3.2. Spin Lock

#### 3.2.1. Spin Lock Binario

Este mecanismo (netamente de software) se basa en la utilización de una única variable global compartida por todos los procesos que tengan ZCs que proteger. Inicialmente esta variable se setea en el valor 0 que representa desbloqueo (**unlock**). El proceso que logra leer ese 0 es autorizado a entrar en su ZC no sin que antes setee el valor 1 en la variable, lo que representará bloqueo (**lock**) para todos los demás procesos que la estén leyendo o intentando leer. Esas lecturas son realizadas por los procesos interesados desde loops que los mantienen "dando vueltas" (**spinning**) hasta que consiguen leer el valor 0.

Este mecanismo se apoya en lo que se conoce como protocolo de espera ocupada (*busy-wait protocol*) porque los procesos que aguardan para ingresar a su ZC permanecen corriendo, manteniendo ocupadas sus respectivas CPUs, intentando superar el bloqueo continuamente. Este protocolo tiene la ventaja de que el proceso que aguarda por el objeto compartido (en este caso la MP para poder ejecutar su ZC) tiene una respuesta inmediata ni bien el mismo queda disponible, pero el inconveniente es que sigue consumiendo recursos del sistema mientras los loops (*spinning*) están corriendo.

Su contrapartida es el protocolo de espera durmiendo (*sleep-wait protocol*). En este modo de operación los procesos son removidos de sus respectivas unidades y colocados en colas de espera (a dormir). Los procesos suspendidos deben ser notificados de los eventos por los que están aguardando, pero mientras están durmiendo liberan una cantidad importante de recursos, por ejemplo ¡la unidad completa! para que

comience a correr en ella otro proceso. En sistemas multiprocesadores el incremento de complejidad del hardware para implementar protocolos de espera durmiendo es importante frente a los de espera ocupada. En particular el mecanismo **spin lock** se aplica preferentemente con protocolos de espera ocupada.

#### 3.2.2. Spin Lock generalizado con n posibles valores

El Spin Lock binario deja en manos del mecanismo arbitrador del bus la prioridad para que el recurso compartido sea asignado. Cada vez que la variable x toma el valor 0 es probable que muchas unidades pretendan leerla simultáneamente. La concesión del bus para poder llevar acabo la lectura es resuelta a favor de una determinada unidad y en detrimento de las demás mediante un mecanismo propio del sistema multiprocesador, que por supuesto deberá contemplar el orden cronológico de las solicitudes para garantizar la sincronización, pero que no podrá ser forzado por el programador. Si la intención es conceder los bloqueos según un orden preestablecido, el programador deberá apelar a una solución como la siguiente,

```

var x: (1, 2, ..., n)

/Se declara la variable global x en el dominio (1,2,...,n)/

x := 1

/Se concede el bloqueo al Proceso 1/

Proceso P_i i=1,2,\ldots,n-1

repetir

:

/Se inserta el loop con espera ocupada justo antes de la ZC/

hasta x:=i

:

/Mientras Proceso i esté dentro de su ZC los demás Procesos

ven bloqueado el acceso a la suya/

x := i+1

/Se libera el acceso al Proceso siguiente/

Proceso Pn

repetir

hasta x:=n

:

:

/Se libera el acceso al primer Proceso/

x := 1

```

Este mecanismo garantiza exclusión mutua al costo de un incremento en los tiempos de espera mientras el bloqueo se va desplazando entre los n procesos ordenados circularmente. Los procesos deberán esperar ("su turno") aún en caso de no haber conflictos por requerimientos simultáneos y si uno quedara bloqueado todos los demás se bloquearían también.

#### 3.2.3. Test&Set

Para que los algoritmos mostrados más arriba tengan un funcionamiento efectivo deberán ser adecuados al hardware del sistema entre otras cosas en lo siguiente: desde que en la variable de bloqueo x es leído el valor que autoriza el ingreso a la ZC y hasta que en esa variable es seteado el valor que impide ese ingreso al resto de los procesos, la unidad a la que en principio le ha sido concedido el bloqueo debe ejecutar varias operaciones (ver Introducción) pudiendo suceder que la variable de bloqueo sea nuevamente leída antes de que le haya sido seteado el valor de protección. Una alternativa para ese problema es la operación (de hardware) Test&Set que permite ejecutar en forma atómica estas acciones,

```

Test&Set(x,y_i):

<y_i:=x; x:=1>

```

$y_i$  es un variable local de cada proceso que ha de quedar con el mismo valor de la variable x al cabo de la ejecución de la primitiva Test&Set. Paralelamente y sin que ningún otro proceso la pueda acceder, la variable x tomará el valor 1 antes de completarse la ejecución de Test&Set. La resultante es una ejecución atómica de una secuencia de dos operaciones que, de otro modo, puede resultar interferida por otro proceso con graves consecuencias para la sincronización. Será necesario entonces reformular los algoritmos anteriores incorporando la mejora provista por este mecanismo. El caso de n procesos entre los que sólo se pretende exclusión mutua no presenta inconvenientes y la aplicación de la primitiva Test&Set es directa. En el caso que los n procesos se quieren sincronizar forzando un orden circular preestablecido aparece un pequeño inconveniente en el hecho que la primitiva Test&Set tal como se presentó fuerza a 1

el valor de x una vez ejecutada. El valor 1 significaba bloqueo del acceso a su ZC para todos los procesos pero ahora, en caso de mantenerse la convención del problema resuelto mediante spin lock, significaría desbloqueo para el proceso  $P_1$ . La solución propuesta pasa por: reservar el valor x=1 para bloqueo a todos los procesos y dar el acceso al proceso  $P_i$  cuando x=i+1 (en lugar de x=i).

```

var x:(1,2,...,n,n+1)

var x:(0,1)

x := 0

x := 2

Proceso P_i i=1,2,\ldots,n

Proceso P_i i=1,2,\ldots,n-1

var y_i : (0,1)

var y_i : (0,1)

repetir

repetir

Test\&Set(x,y_i)

Test\&Set(x,y_i)

hasta y_i := 0

hasta y_i := i+1

x := 0

x := y_i + 1

Proceso Pn

var y_n:(0,1)

repetir

Test\&Set(x,y_n)

hasta y_n := n+1

x := 2

```

Distintos fabricantes dan a este tipo de operación nombres como: Fetch&Add, Compare&Swap,... Y además otros mecanismos similares son provistos para operaciones de carácter atómico tanto en *lecturas*, *escrituras*, *lectura-modificación-escritura*, etc. Veamos entonces los algoritmos,

### 3.3. Semáforos

Los semáforos son un medio para implementar sincronización aplicado en sistemas con protocolos de espera durmiendo. Los hay de dos tipos, binario y de conteo.

#### 3.3.1. Semáforos binarios

Un semáforo binario es una variable booleana (s) capaz de tomar los valores 0 o 1. Cada recurso compartido (en particular las ZCs) puede asociarse a un semáforo. Luego de la declaración e inicialización sólo dos operaciones primitivas (de carácter atómico) pueden ejecutarse sobre s,

- P(s) resta 1 al valor de s en tanto y en cuanto el valor de s no sea 0.

- V(s) suma 1 al valor de s en tanto y en cuanto el valor de s no sea 1.

A través de una adecuada convención, los semáforos binarios se corresponden en esencia con las variables de bloqueo (lock) empleadas en protocolos de espera ocupada para resolver problemas de exclusión mutua. Veamos entonces la aplicación de este mecanismo al problema resuelto anteriormente mediante spin lock, aceptando para ello una convención adicional: un intento de P(s) cuando s=0 pondrá a dormir al proceso que haya hecho el intento, mientras que toda operación V(s) despertará al proceso que esté al tope de la cola de procesos durmiendo en tanto ésta no esté vacía.

El primer proceso (digamos  $P_k$ ) que consigue ejecutar P(s) accede inmediatamente a su ZC. Todos los demás procesos que intenten hacer P(s) mientras está en ejecución la ZC de  $P_k$  se encuentran con s=0 y se ponen a dormir. Cuando  $P_k$  ejecuta V(s) despierta al primer proceso de la cola (si lo hubiese) y lo pone en estado *listo*, o sea en condiciones de ejecutar inmediatamente su P(s).

#### 3.3.2. Semáforos de conteo

En el caso de semáforos de conteo la variable s ya no es booleana sino entera no-negativa y capaz de tomar los (n+1) valores: 0,1,2,....,n. Un semáforo de conteo se comporta como una colección de n permisos que actúan sobre otras tantas copias de un recurso compartido (un dato, una variable, un array, una ZC, etc.) de modo que permite atender cada pedido del recurso concediendo permiso sobre el mismo hasta tanto todas sus copias hayan sido concedidas. Formalmente se definen también dos operaciones primitivas y de carácter atómico,

- P(s) resta 1 al valor de s en tanto y en cuanto s>0, caso contrario coloca el proceso a dormir.

- V(s) suma 1 al valor de s y eventualmente despierta un proceso dormido a la espera de ejecutar P(s).

Intuitivamente P(s) corresponde a un pedido de permiso, mientras que V(s) representa la devolución del permiso recibido una vez que se ha hecho uso de una copia del recurso compartido asociado con el semáforo. Todo segmento de código delimitado por el par de primitivas (P,V) resulta así imposible de ser interrumpido por otro proceso.

Supongamos por ejemplo que quisiéramos limitar a 3 el número máximo de procesos corriendo simultáneamente en nuestro equipo multiprocesador mediante el uso de un semáforo de conteo.

semáforo s: s:=3

| Т              | Proceso i | Proceso j | Proceso k | Proceso 1 | s:  |

|----------------|-----------|-----------|-----------|-----------|-----|

| t <sub>0</sub> |           |           |           |           | s=3 |

| $t_1$          |           | P(s)      |           |           | s=2 |

| $t_2$          | P(s)      | :         |           |           | s=1 |

| $t_3$          | :         | :         | P(s)      |           | s=0 |

| $t_4$          | :         | :         | :         |           |     |

| $t_5$          | :         | :         | :         |           |     |

| $t_6$          | :         | :         | :         |           |     |

| $t_7$          | :         | :         | :         | P(s)      | (a) |

| $t_8$          | :         | :         | :         | :         |     |

| t <sub>9</sub> | V(s)      | :         | :         | :         | (b) |

| $t_{10}$       |           | :         | V(s)      | :         |     |

| $t_{11}$       |           | V(s)      |           | :         |     |

- (a) en t₁ se intenta lanzar el Proceso l pero éste no puede ejecutar P(s) porque s=0 por lo tanto es puesto a dormir.

- (b) en t<sub>9</sub> el Proceso i ejecuta su V(s) con dos consecuencias: se lleva el valor de s de 0 a 1 y se despierta al Proceso l para que ejecute su P(s) y comience a correr.

Veamos ahora una aplicación de semáforos sobre el clásico problema PRODUCTOR-CONSUMIDOR. Proceso PRODUCTOR es aquel que produce items que son demandados por un proceso CONSUMIDOR. Los items producidos son alojados en una cola o buffer en espera de ser requeridos de modo que no puede alojarse más que un número máximo de items y no pueden extraerse items si el buffer/cola está vacío. En general un conjunto de PRODUCTORES y otro de CONSUMIDORES (vinculados por el mismo tipo de item) estarán corriendo simultáneamente, en el mejor de los casos, en distintas unidades de procesamiento. Tanto la colocación como la extracción de items se compone de una cantidad de pasos que por motivos similares a los expuestos hasta aquí (ver Introducción) conviene que sean ejecutados sin ser interrumpidos por otro pedido de colocación/extracción, es decir merecen ser tratados como procesos de exclusión mutua y una forma de protegerlos es mediante un semáforo binario. Por otro lado cuando el buffer/cola está lleno se deben impedir intentos de colocación de items, para lo cual no es mala idea poner a dormir a los PRODUCTORES que soliciten colocar, hasta que se produzcan vacantes en el buffer/cola. Asimismo al vaciarse el buffer/cola, poner a dormir a los CONSUMIDORES que quieran extraer puede resultar una decisión muy útil. Dos semáforos de conteo pueden manejar esta última implementación.

semáforo s:,lleno:,vacío:

s:=1,lleno:=0,vacío:=N

/Se declaran e inicializan variables globales de tipo semáforo, s para la exclusión mutua de accesos al buffer/cola, lleno y vacío para limitar colocaciones y extracciones de items a la capacidad del buffer/cola/

```

Proceso P_i i=1,2,\ldots,j

/j procesos PRODUCTORES/

repetir

producir(item)

/se crea un nuevo item/

P(vacío)

P(s)

colocar(item)

/se coloca en el buffer/cola/

V(s)

V(lleno)

siempre

Proceso C_i i=1,2,...,k

/k procesos CONSUMIDORES/

repetir

P(lleno)

P(s)

/se extrae un item del buffer/cola/

extraer(item)

V(s)

V(vacío)

utilizar(item)

/se procesa el item/

siempre

```

Colocaciones y extracciones están protegidas por los pares (P,V) sobre el semáforo s y por fuera de esos bloques (brindando un nivel adicional de protección) hay pares (P,V) sobre los semáforos lleno y vacío pero cruzados. La resultante de este mecanismo es la siguiente: el primer proceso que intente colocar llevará al semáforo vacío de (N) a (N-1) ejecutando la primitiva P(vacío) y consiguiendo así alcanzar la línea P(s). Como s está en 1, la llevará a cero y pasará a ejecutar la rutina colocar(item). Ningún proceso podrá mientras tanto intentar extraer porque al estar lleno en 0 P(lleno) es imposible y aún en el caso de lleno>0 la extracción sólo podrá tener lugar luego de ejecutado V(s) del proceso que está colocando. Por otro lado cuando se intente extraer habrá que superar la barrera P(lleno); como lleno se inicializó en 0, P(lleno) solo podrá ejecutarse cuando hubiese sucedido antes un V(lleno) es decir cuando algún item hubiese sido colocado con anterioridad.

### 3.4. Monitores

Los monitores son programas de alto nivel encargados de administrar los recursos compartidos. Son propios de los ambientes donde la programación es estructurada y se componen de una colección de variables compartidas y procedimientos asociados bajo una única estructura que da acceso los procesos para que ejecuten los procedimientos cuando los necesiten. Un monitor típico se compone de tres partes:

- Definición de su nombre y declaración de todas sus variables locales.

- Colección de procedimientos que harán uso de las variables locales declaradas (y de las variables globales de los procesos bajo la forma de argumentos).

- Inicialización de las variables locales declaradas.

La idea es que las ZCs de los procesos sean removidas de los mismos e implementadas a través de los procedimientos del monitor. La exclusión mutua se garantiza en el hecho que sólo un proceso por vez puede acceder a dichos procedimientos. La sincronización queda en manos de determinadas primitivas de condición que permiten la comunicación entre procedimientos dentro del mismo monitor. Por ejemplo:

- wait(condición) pone al proceso que activó el monitor a dormir y así lo deja hasta que sea despertado por una señal (signal) que le indique que la condición ha sido satisfecha.

- signal(condición) despierta a un proceso que hubiese estado durmiendo en espera que se satisfaga la condición y no hace nada en caso de no haber proceso durmiendo a la espera de condición.

El monitor no resulta entonces un proceso en sí mismo sino un módulo estático de datos y declaraciones de procedimientos que sólo se activa a solicitud de los verdaderos procesos, los que deben ser programados por separado. Veamos el problema PRODUCTOR-CONSUMIDOR resuelto mediante un monitor. suponiendo que se producen y se ofrecen al consumidor, números enteros.

Monitor PRODUCTOR-CONSUMUDOR /Nombre del monitor/ Buffer[1:N]:entero No\_lleno, No\_vacío:bool In,Out:entero Cont: indice

/Declaración de variables. El Buffer es un array de enteros a ser recorrido en forma circular, No\_lleno y No\_vacío indican el estado del Buffer, In y Out son punteros para colocar o extraer del Buffer y Cont un indicador de la cantidad de items alojados en el Buffer/

```

Procedimiento Colocar(item)

comienzo

if Cont=N then Wait(No_lleno)

Buffer[In]:=item

In:=(In+1) \mod N

Signal(No_vacío)

fin

Procedimiento Extraer(item)

comienzo

if Cont=0 then Wait(No_vacío)

item:=Buffer[Out]

Out:=(Out+1) mod N

Signal(No lleno)

fin

comienzo

In:=0

Out:=0

Cont:0

fin

```

No se explicita el modo de operación de la variable Cont pero debería ser valorizada mediante algún cálculo que contemple las posiciones relativas de los punteros In y Out. Tampoco se muestra la valorización de las variables No\_lleno y No\_vacío pero es muy claro su significado. Aceptando que el pseudo-código utilizado tiene connotaciones del Pascal, vale la pena remarcar el hecho que el programa monitor "no hace nada por sí mismo", atendiendo a que en el segmento donde iría el código del programa principal, es decir entre **comienzo** y **fin** (**begin** y **end** en Pascal) no hay más que inicialización de variables locales.

Hasta aquí, el monitor propiamente dicho y por último los procesos,

```

Productor

item:entero

comienzo

Producir(item)

Colocar(item)

fin

Consumidor

item:entero

comienzo

Extraer(item)

Utilizar(item)

fin

```

¿Cómo sería la operación de este mecanismo?, supongamos que el proceso Productor crea un item mediante el procedimiento Producir (que no se muestra) y luego decide colocarlo en el Buffer para que quede a disposición del proceso Consumidor. En primer lugar deberá esperar a que el monitor esté desocupado, quedando así garantizada la colocación en forma atómica. Una vez que obtiene el acceso al monitor ejecuta el procedimiento Colocar. Si el Buffer está lleno (Cont=N) el proceso Productor es puesto a dormir hasta que lo despierte una señal que le indique que ya no lo está (No\_lleno) y el único lugar donde puede generarse esa señal (signal) es en el procedimiento Extraer luego de una extracción exitosa. Pero si Cont<N entonces el Buffer alojará el item en la posición señalada por el puntero In, luego de lo cual se desplazará ese puntero una unidad y finalmente enviará una señal de No\_vacío por si hubiese algún proceso Consumidor durmiendo a la espera de items.

## 4. Simulación de arquitecturas paralelas

### 4.1. Introducción

Las aplicaciones escritas para sistemas de procesamiento paralelo son programas que requieren, para su ejecución, equipos dotados de N procesadores, de modo que en cada uno de ellos pueda correr simultáneamente un proceso creado en tiempo de ejecución, compartiendo eventualmente entre todos alguna zona de la memoria, con la esperanza de que el tiempo total que le tome correr a la aplicación completa se reduzca una cantidad de veces comprendida entre 1 y N con relación al que le tomaría correr en un equipo secuencial monoprocesador. ¿Cómo podría una aplicación escrita para su procesamiento paralelo correr en una máquina con un solo procesador? Bueno, al decir "...el tiempo que le tomaría correr en un equipo secuencial monoprocesador..." no me refiero al programa paralelo textual sino a su versión equivalente escrita para un computador monoprocesador, no obstante lo cual también es posible correr directamente el programa paralelo en un equipo con un sólo procesador y el artificio que lo permite es precisamente el que instrumenta la simulación que vamos a presentar a continuación y en alguna medida el mecanismo en el que se basan los sistemas multitarea/multiusuario para crear la ilusión de que dos o más procesos pueden ejecutarse simultáneamente cuando la arquitectura secuencial monoprocesadora (Von Neumann) sobre las que operan, ¡no permite más que uno a la vez!.

Un programa redactado para ser procesado en máquina paralela incluirá sentencias especiales (las que le darán precisamente el carácter paralelo), desde las encargadas de la creación de procesos y el lanzamiento de los mismos en distintas unidades de procesamiento, hasta los pedidos de acceso a zonas comunes, los pedidos de bloqueo y liberación de las zonas comunes, etc., insertadas dentro de código de programación convencional (no paralelo). Al menos esa es la filosofía de muchas de las herramientas de programación en este paradigma.

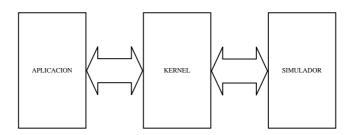

Vamos a introducir sistemas capaces de simular el comportamiento de computadoras de procesamiento paralelo en máquinas monoprocesadoras, de modo que resulte posible en estas correr programas diseñados para aquellas. Los vamos a presentar descompuestos en bloques uno de los cuales es precisamente la APLICACION.

Llamaremos por número, desde #0 hasta #N a cada una de las unidades de procesamiento de la computadora a simular y "procesador local" (host processor) al que reside física y realmente en nuestra máquina. En él va a comenzar a correr la aplicación, y a medida que la misma vaya arribando a puntos de interés global (primitivas de sincronización o referencias a memoria insertadas en el código) otro bloque llamado KERNEL, con el que la APLICACION estará intercambiando señales permanentemente, los detectará y ordenará las acciones a seguir. En definitiva la función del KERNEL no es otra que reordenar las tareas de modo de transformar un proceso paralelo en uno equivalente serie. Veámoslo desde el siguiente punto de vista: se inicia la ejecución de una APLICACION, lo cual en la máquina paralela sucedería en la unidad #0 y en la máquina real sucede en el procesador local (host processor). Hasta tanto no se arribe a una sentencia que ordene una acción de carácter global, no habrá diferencias.

Analicemos a partir de aquí dos situaciones posibles, (1) el programa ordena la creación y el lanzamiento de un proceso en otra unidad de procesamiento, el KERNEL lo detiene y lo deja en un estado de "listo para retomar su ejecución", como no tiene dónde lanzar el nuevo proceso, lo programa para ser lanzado en el mismo procesador local y para que una vez iniciada su ejecución corra hasta que se vea obligado a detenerlo, (2) en un instante determinado uno de los procesos ordena una referencia (lectura/escritura) a una zona compartida de la memoria, el KERNEL lo debe detener, tomando nota de qué tipo de operación ha sido solicitada así como del instante de tiempo en el que ha sucedido la solicitud, pudiendo así planificarla para un instante futuro. Esta planificación (*scheduling*) consiste en ir colocando en una cola todas las tareas que, producto de los eventos del tipo (1) y (2) vayan quedando pendientes, respetando el

orden cronológico cuando se trate de referencias a memoria y colocándolas al final cuando se trate de solicitudes de reinicio de ejecución de proceso. Una vez que comiencen a ejecutarse esas acciones programadas, cada vez que una referencia a memoria (tomada del tope de la cola) sea ejecutada, el proceso correspondiente pasará al estado de "listo para retomar su ejecución" y por ende planificado, por lo que llegará un momento en que la cola de planificación sólo va a contener solicitudes de reinicio, entonces el KERNEL comenzará a relanzar uno a uno todos los procesos hasta que comiencen nuevamente las detenciones producto de eventos de tipo (1) y/o (2).

Resumiendo: el KERNEL irá planificando (entendiendo por planificar colocar en la posición "adecuada" de una cola) referencias a memoria y solicitudes de reinicio de corrida de procesos; e irá ordenando las tareas a seguir tomándolas del tope de esa cola una vez que todos los procesos se hayan detenido. Como consecuencia, las operaciones que la APLICACION espera sean realizadas en forma simultánea, "una al lado de la otra" se transformarán en otras realizadas en forma secuencial "una a continuación de la otra", resultando una ejecución sincronizada de las referencias a memoria (tal como sucederían en la realidad), y corriendo uno tras otro los procesos en tanto sus corridas no se afecten mutuamente.

Por último existe un bloque que también intercambia señales con el KERNEL cuya misión es ejecutar las referencias a la memoria compartida. Este bloque, designado como SIMULADOR en el diagrama, se comporta de acuerdo a la arquitectura y al protocolo que para todo lo que tenga que ver con memoria se desee simular. O sea que para una misma APLICACION y un mismo KERNEL, un usuario podrá elegir las características principales de la máquina paralela en la que se desea "ver correr" la APLICACION modificando el bloque SIMULADOR o eventualmente creando uno nuevo.

El sistema completo ofrecerá al usuario dos tipos de resultado: por un lado la salida que produciría la APLICACION al correr sobre una máquina paralela real y por otro un paquete de información y estadísticas sobre cuestiones internas de la máquina simulada. El primer tipo de resultado es útil para aquellos interesados en ensayar algoritmos paralelos y cuestiones inherentes exclusivamente a software de ese tipo, programas, etc. El segundo lo es para quienes deseen ensayar variantes propias de la arquitectura paralela, como por ejemplo: el número de unidades de procesamiento, el tamaño de memoria cache, el tamaño de las líneas de memoria cache, el protocolo de coherencia, etc.

Este tipo de simulación es uno de los tantos que existen en su género y dado su modo de funcionamiento es conocido como "simulación conducida por ejecución" (execution-driven simulation) puesto que todos los eventos son generados precisamente ejecutando la aplicación en el procesador local, de manera que la ilusión creada es la de que el programa corre en una máquina paralela formada por "N máquinas locales". Otra alternativa es la simulación "conducida por trazas" (trace-driven simulation), aquí los eventos son generados a partir de trazas producidas por otras herramientas (ajenas al simulador) y eventualmente en otras máquinas, distintas del procesador local. El método no es del todo apropiado para nuestro caso dado que trazas paralelas producidas para un determinado sistema de memoria podrían nunca suceder en otro; el método resulta por tanto inexacto aunque rápido, pero a costa del enorme espacio que ocupan las buenas trazas.

Otra modalidad pasa por "interpretar " el código de máquina en lugar de "ejecutarlo", puede resultar una opción interesante cuando se pretende un nivel extremo de detalle pero muy lento dado lo inútil de interpretar instrucciones que no tengan efecto global.

### **4.2.** Limes

Linux memory simulator: Limes, es un simulador (conducido por ejecución) que a diferencia de casi la mayoría de sus equivalentes corre en PC i486 (o superior) bajo sistema operativo Linux, por supuesto, originalmente diseñado para correr programas de la colección SPLASH-2 (Stanford Parallel Applications for Shared Memory) que tienen carácter de benchmark. Se trata de programas escritos en "C" con el apoyo del juego de macros **ANL** (Argonne National Laboratory) para resolver las cuestiones de carácter global/paralelo.

Para correr Limes cualquier versión de kernel de Linux es adecuada pero es requisito que el compilador sea GNU CC 2.6.3, si se cuenta con uno superior (actualmente la versión es 2.95) basta con copiar sólo los archivos que conforman el entorno de desarrollo (*development environment*) a un directorio determinado y retocar ligeramente algunos archivos previo a la compilación.

El paquete incluye simuladores basados en cuatro protocolos (*snoopy*) de coherencia cache, Berkeley, Dragon, WIN (Word Invalidate, un protocolo basado en el método de invalidación parcial de palabra) y WTI (Write-Through Invalidate un protocolo elemental que exhibe la peor performance de todos). También permite implementar lo que llama Simulador Ideal y que no es otra cosa que la simulación de un sistema de memoria perfecta en el que todas las referencias se completan en un ciclo y además se admiten accesos simultáneos, es decir que se completan en un solo ciclo todos los accesos que pudieran coincidir para un instante determinado (ver Ensayos).

#### 4.2.1. Macros ANL

A modo de ilustrar la utilización de los macros veamos un breve ejemplo de su aplicación para resolver operaciones de carácter global en un programa que incrementa en cuatro el valor de una variable (incrementándola en uno cuatro veces), para lo cual lanza tres procesos paralelos, realizando un incremento cada proceso, y uno el Master (se conoce como Master al proceso principal desde el que se lanzan los restantes). Veamos previamente una breve descripción de los macros que serán necesarios,

**LOCKDEC**(x) Declara la variable de bloqueo x.

**LOCKINIT**(x) Inicializa la variable de bloqueo x en su valor *free* ó cero, que representa no-bloqueo. Utilizado por el Master antes de que comience el procesamiento paralelo.

**LOCK**(x) Lleva la variable de bloqueo x a su valor *busy* ó uno, que representa bloqueo. Utilizado al ingresar a Zonas Críticas. Es una operación de tipo spin lock en la que cada verificación se hace en forma atómica.

**UNLOCK**(x) Lleva la variable de bloqueo x a su valor *free* ó cero, que representa no-bloqueo. Utilizado al salir de Zonas Críticas.

**CREATE** (p) Crea un proceso p que comienza su ejecución en paralelo con el padre que lo creó. Cuando el proceso p alcanza su fin deja de existir.

**WAIT\_FOR\_END**(n) El programa se detiene al llegar a esta sentencia hasta que completen su ejecución los n procesos que éste hubiese creado. Al momento de ejecutarse es muy probable que se ignore cuantos procesos quedan por terminar, no obstante se deben mencionar todos los creados.

```

int cont;

LOCKDEC (bloqueo);

void(Proceso);

main() {

int i;

cont=0;

LOCKINIT(bloqueo);

/* 1 */

for(i=1;i<4;++i)

CREATE(Proceso);

/* 2 */

Proceso();

WAIT_FOR_END(3);

/* 3 */

/* 4 */

printf("cont=%d\n",cont);

}

void Proceso() {

LOCK(bloqueo);

++cont;

UNLOCK(bloqueo);

```

Teniendo en cuenta las explicaciones sobre cada macro utilizado, el programa resulta simple de entender. Sólo algunas líneas merecen comentario,

- /\* 1 \*/ La función Proceso es lanzada tres veces y comienza a correr, en el mejor de los casos, en tres procesadores distintos.

- /\* 2 \*/ Por cuarta vez es lanzada la función Proceso pero ahora queda corriendo en el mismo procesador en el que lo está haciendo main().

- /\* 3 \*/ main() puede estar seguro de que se completó la función Proceso que está corriendo en su mismo procesador (la de la línea /\* 2 \*/) pero como ignora si se han completado o no los otros tres, se detiene a la espera de ese evento.

- /\* 4 \*/ Se imprime el valor de cont que en este punto es 4.

#### 4.2.2. Limes-Guía de Usuario

Cada uno de los tres benchmarks cuenta con su propio juego de opciones para cada corrida (similares, salvo en los casos de parámetros específicos del problema resuelto por la aplicación). Se transcriben textualmente las partes del código fuente de cada uno en las que se comentan esas opciones.

```

Perform 1D fast Fourier transform using six-step FFT method

1) Performs staggered, blocked transposes for cache-line reuse

2) Roots of unity rearranged and distributed for only local

accesses during application of roots of unity

3) Small set of roots of unity elements replicated locally for % \left( 1\right) =\left( 1\right) \left( 1\right)

1D FFTs (less than root N elements replicated at each node)

4) Matrix data structures are padded to reduce cache mapping

conflicts

Command line options:

-mM : M = even integer; 2**M total complex data points transformed.

-pP : P = number of processors; Must be a power of 2.

-nN: N = number of cache lines.

-lL : L = Log base 2 of cache line length in bytes.

-s : Print individual processor timing statistics.

-t : Perform FFT and inverse FFT. Test output by comparing the

integral of the original data to the integral of the data

that results from performing the FFT and inverse FFT.

-o : Print out complex data points.

-h : Print out command line options.

Note: This version works under both the FORK and SPROC models

/*****************************

/*

Parallel dense blocked LU factorization (no pivoting)

This version contains one dimensional arrays in which the matrix

/*

to be factored is stored.

Command line options:

/*

-nN : Decompose NxN matrix.

-pP : P = number of processors.

-bB : Use a block size of B. BxB elements should fit in cache for

good performance. Small block sizes (B=8, B=16) work well.

-s : Print individual processor timing statistics.

-t : Test output.

: Print out matrix values.

-h : Print out command line options.

Note: This version works under both the FORK and SPROC models

/*

SPLASH Ocean Code

This application studies the role of eddy and boundary currents in

influencing large-scale ocean movements. This implementation uses

dynamically allocated four-dimensional arrays for grid data storage.

Command line options:

-nN : Simulate NxN ocean. N must be (power of 2)+2.

-pP: P = number of processors. P must be power of 2.

-eE : E = error tolerance for iterative relaxation.

-rR : R = distance between grid points in meters.

-tT: T = timestep in seconds.

-s : Print timing statistics.

-o : Print out relaxation residual values.

-h : Print out command line options.

Default: OCEAN -n130 -p1 -e1e-7 -r20000.0 -t28800.0

NOTE: This code works under both the FORK and SPROC models.

```

Una simulación completa involucra a los tres conjuntos de programas: APLICACION+KERNEL+SIMULADOR, linkeados sobre un único ejecutable. Ese proceso de compilación se maneja íntegramente desde los archivos makefile de cada aplicación. La única tarea del usuario es ejecutar "make" en el directorio en el que se encuentra el benchmark que va a constituir la aplicación, revisando previamente su makefile y adecuándolo a los propios intereses, comentando, descomentando o valorizando las variables que se detallan a continuación.

**APPCS**: define la lista de módulos de la forma "nombre.c" que conforman la aplicación.

**APPCCFLAGS**: define banderas a ser pasadas al compilador. Casi invariablemente se utilizará **-O2**. Otras opciones cono por ejemplo **-g** podrían resultar de interés para indicar al compilador que se requiere información para debugging, fundamentalmente si se trabaja con aplicaciones creadas por el usuario.

**APPLDFLAGS**: especifica banderas a ser pasadas al linker (como por ejemplo **-lm** para que se incluya la librería matemática).

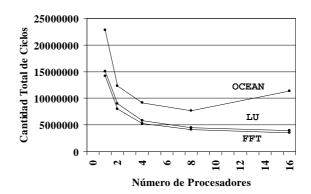

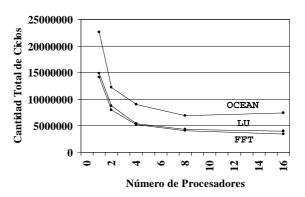

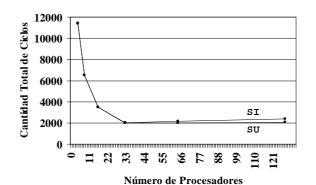

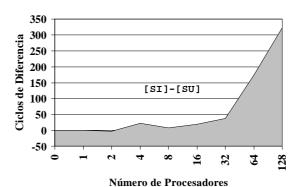

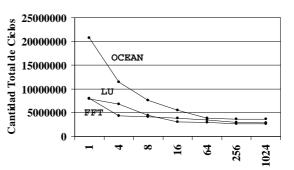

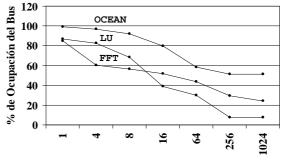

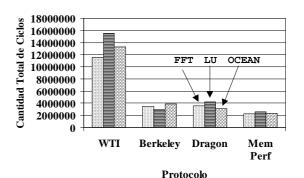

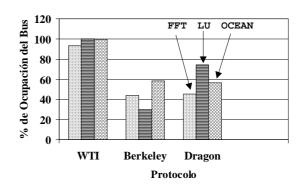

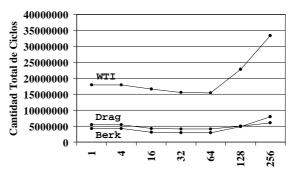

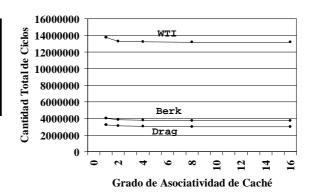

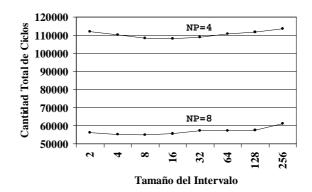

**AUGFLAG**: por medio de esta variable es posible decidir que tipos de evento, de los generados por un proceso, deben ser instrumentados por Limes. Existen tres posibles niveles: **-0** indica que sólo se atenderán instrucciones de sincronización e instrucciones de máquina definidas por el usuario; es particularmente útil si sólo se pretende ensayar algoritmos con uso de locks para proteger secciones críticas. **-1** ordena implementar lo mismo que -0 más lecturas y escrituras "compartidas", es el nivel por default y **-2** ordena instrumentar todo, incluidas referencias a la pila, accesos a datos locales, etc., es la opción adecuada si se quiere simular el sistema con buen nivel de detalle (caches, etc.).