## Estimation and Control Techniques in Power Converters

by

### Gabriel Eirea

Ingen. (Universidad de la República, Uruguay) 1997 M.Sc. (Northeastern Universisty) 2001

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Science

in the

GRADUATE DIVISION  $\qquad \qquad \text{of the} \\ \text{UNIVERSITY OF CALIFORNIA, BERKELEY}$

Committee in charge:

Professor Seth R. Sanders, Chair

Professor Robert G. Meyer

Professor Roberto Horowitz

Fall 2006

## Estimation and Control Techniques in Power Converters

Copyright 2006

by

Gabriel Eirea

#### Abstract

Estimation and Control Techniques in Power Converters

by

### Gabriel Eirea

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Science

University of California, Berkeley

Professor Seth R. Sanders, Chair

This thesis develops estimation and control techniques in power converters. The target applications are voltage regulators for modern microprocessors (VRM) and distributed DC power systems (DPS).

A method for the on-line calibration of a circuit board trace resistance at the output of a buck converter is described. This method is applied to obtain an accurate and high-bandwidth measurement of the load current in the VRM applications, thus enabling an accurate DC load-line regulation as well as a fast transient response. Experimental results show an accuracy well within the tolerance band of this application, and exceeding all other popular methods.

A method for estimating the phase current unbalance in a multi-phase buck converter is presented. The method uses the information contained in the voltage drop at the input capacitor's ESR to estimate the average current in each phase. The method

can be implemented with a low-rate down-sampling A/D converter and is not com-

putationally intensive. Experimental results are presented, showing good agreement

between the estimates and the measured values.

An online adaptation method of the gain of an output current feedforward path

in VRM applications is developed. The feedforward path can improve substantially

the converter's response to load transients but it depends on parameters of the power

train that are not known with precision. By analyzing the error voltage and finding its

correlation with the parameter error, a gradient algorithm is derived that makes the

latter vanish. Experimental results show a substantial improvement of the transient

response to a load current step in a prototype VRM.

Impedance interactions between interconnected power subsystems are analyzed.

Typical examples of these interconnections are a power converter with a dynamic load,

a power converter with an input line filter, power converters connected in parallel or

cascade, and combinations of the above. A survey of the most relevant results in this

area is presented together with detailed examples. Fundamental limits on the perfor-

mance of the interconnected systems are exposed and a system-level design approach

is proposed and corroborated with simulations.

Professor Seth R. Sanders Dissertation Committee Chair To Sônia, todo o amor que houver nesta vida.

To my parents, with love and gratitude.

# Contents

| Li       | st of | Figures                                        | V  |

|----------|-------|------------------------------------------------|----|

| Li       | st of | Tables                                         | ix |

| Ι        | Es    | timation Techniques in VRM Applications        | 1  |

| 1        | Inti  | roduction                                      | 2  |

|          | 1.1   | VRM and DPS applications                       | 2  |

|          | 1.2   | Thesis overview                                | 11 |

| <b>2</b> | Out   | put Current Estimation                         | 14 |

|          | 2.1   | Introduction                                   | 15 |

|          | 2.2   | Method description                             | 19 |

|          | 2.3   | Method analysis                                | 23 |

|          |       | 2.3.1 Errors due to simplified switching model | 23 |

|          |       | 2.3.2 Errors due to lumped resistance model    | 27 |

|          | 2.4   | Experimental results                           | 30 |

|          | 2.5   | Conclusions                                    | 35 |

| 3        | Pha   | ase Current Unbalance Estimation               | 37 |

|          | 3.1   | Introduction                                   | 38 |

|          | 3.2   | Method description                             | 40 |

|          | 3.3   | Method implementation                          | 50 |

|          |       | 3.3.1 Sampling the input voltage waveform      | 51 |

|          |       | 3.3.2 Computation                              | 53 |

|          | 3.4   | Experimental results                           | 55 |

|          | 3.5   | Conclusions                                    | 50 |

| 4            | $\operatorname{Ada}$ | aptive Output Current Feedforward                  | 61      |

|--------------|----------------------|----------------------------------------------------|---------|

|              | 4.1                  | Introduction                                       | 62      |

|              | 4.2                  | Feedforward gain adaptation                        | 64      |

|              |                      | 4.2.1 Ideal feedforward                            | 64      |

|              |                      | 4.2.2 Adaptation algorithm                         | 68      |

|              | 4.3                  | Digital implementation                             | 73      |

|              | 4.4                  | Experimental results                               | 76      |

|              | 4.5                  | Conclusions                                        | 85      |

| II<br>te     | Iı<br>ems            | mpedance Interactions in DC Distributed Power Sys- | -<br>86 |

| 5            | Imp                  | pedance Interactions: An Overview                  | 87      |

|              | 5.1                  | Introduction                                       | 87      |

|              | 5.2                  | Literature review                                  | 90      |

|              | 5.3                  | Problem description                                | 91      |

|              | 5.4                  | Middlebrook criterion                              | 97      |

|              | 5.5                  | Modeling                                           | 104     |

|              | 5.6                  | Conclusions                                        | 112     |

| 6            | Mit                  | 0 1                                                | 113     |

|              | 6.1                  | Limits of performance                              | 113     |

|              | 6.2                  | Robust design of controllers                       | 115     |

|              |                      | 6.2.1 The plant                                    | 116     |

|              |                      | 6.2.2 Preliminary analysis                         | 120     |

|              |                      | 6.2.3 PID feedback design                          | 120     |

|              |                      | 6.2.4 Input voltage feedforward                    | 124     |

|              |                      | 6.2.5 $\mu$ -synthesis design                      | 124     |

|              |                      | 6.2.6 Conclusions                                  | 132     |

|              | 6.3                  | Virtual damping of input filter                    | 136     |

|              | 6.4                  | Conclusions                                        | 139     |

| 7            | Cor                  | ntributions and Future Work                        | 142     |

|              | 7.1                  | Contributions of this Thesis                       | 142     |

|              | 7.2                  | Suggestions for future research                    | 145     |

| B            | ibliog               | graphy                                             | 149     |

| $\mathbf{A}$ | Unl                  | palance estimation Matlab code                     | 158     |

| 1V |  |

|----|--|

|    |  |

|    |  |

| В            | Adaptive feedforward Verilog code | 161 |

|--------------|-----------------------------------|-----|

| $\mathbf{C}$ | Robust design Matlab code         | 165 |

# List of Figures

| 1.1 | Trends in VRM applications. (Extracted from [1].)                                                                                                                                                          | 5  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Multiphase buck converter with synchronous rectification. Three-phase                                                                                                                                      |    |

|     | example                                                                                                                                                                                                    | 6  |

| 1.3 | Adaptive Voltage Positioning                                                                                                                                                                               | 7  |

| 1.4 | Illustration of the evolution of VRM specifications: faster and larger load transients with tighter regulation of the output voltage                                                                       | 8  |

| 1.5 | Motherboard Abit IS7 with VRM controller Intersil HIP6301CB. (Ex-                                                                                                                                          |    |

|     | tracted from http://www.lostcircuits.com)                                                                                                                                                                  | 9  |

| 2.1 | Inductor sensing                                                                                                                                                                                           | 17 |

| 2.2 | Buck converter                                                                                                                                                                                             | 19 |

| 2.3 | In steady-state and CCM, $\langle uI_L \rangle = \langle uI_o \rangle$ because the areas of the                                                                                                            |    |

|     | shaded triangles are equal                                                                                                                                                                                 | 21 |

| 2.4 | Current sense amplifier with gain estimation loop                                                                                                                                                          | 22 |

| 2.5 | Current sense amplifier with gain estimation loop, modified to contem-                                                                                                                                     |    |

|     | plate non-ideal effects                                                                                                                                                                                    | 27 |

| 2.6 | Kelvin sensing technique with resistor averaging in a 3-phase VRM                                                                                                                                          | 30 |

| 2.7 | Estimation breadboard schematic (simplified)                                                                                                                                                               | 31 |

| 2.8 | Prototype breadboard connected to the VRM evaluation board                                                                                                                                                 | 33 |

| 2.9 | Experimental measurements of the current estimation method. Left: measured values. Right: absolute (top) and relative (bottom) errors. (Dashed line: correct value; Dotted line: measurement without trim- |    |

|     | ming; Solid line: measurement after trimming.)                                                                                                                                                             | 34 |

| 3.1 | Two-phase buck converter. The input capacitor's ESR is shown explicitly.                                                                                                                                   | 41 |

| 3.2 | Voltage and current waveforms in a two-phase buck converter with                                                                                                                                           |    |

|     | unbalanced currents                                                                                                                                                                                        | 42 |

| 3.3 | Canacitor current sensing                                                                                                                                                                                  | 44 |

| 3.4<br>3.5<br>3.6 | Pulse train                                                                                                          | 45<br>46 |

|-------------------|----------------------------------------------------------------------------------------------------------------------|----------|

| 3.7<br>3.8        | ample with three phases                                                                                              | 52<br>56 |

| 3.9               | of phase one. The circles indicate the samples                                                                       | 58<br>60 |

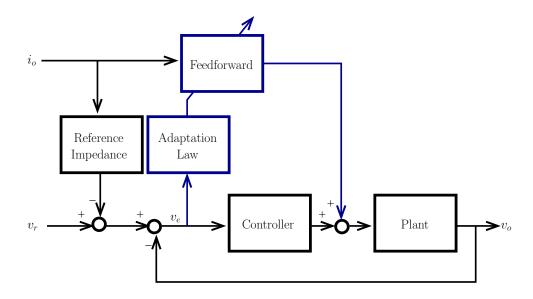

| 4.1               | Model Reference Adaptive Control                                                                                     | 64       |

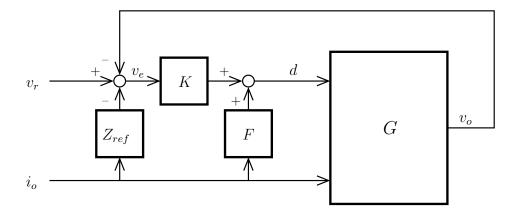

| 4.2               | MRAC in a VRM application.                                                                                           | 65       |

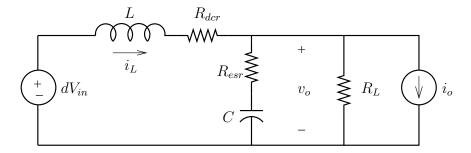

| 4.3               | DC/DC converter model using voltage mode control and output cur-                                                     |          |

| 4.4               | rent feedforward                                                                                                     | 66       |

|                   | tive load.                                                                                                           | 67       |

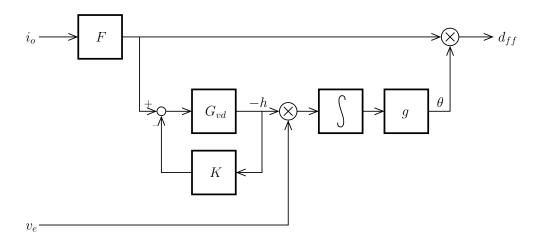

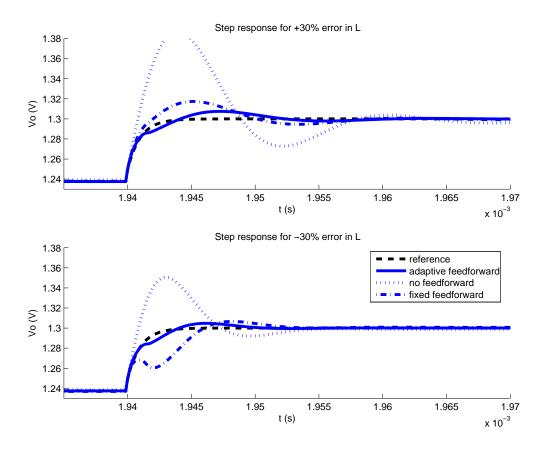

| 4.5<br>4.6        | Feedforward path with gain adaptation algorithm                                                                      | 71<br>72 |

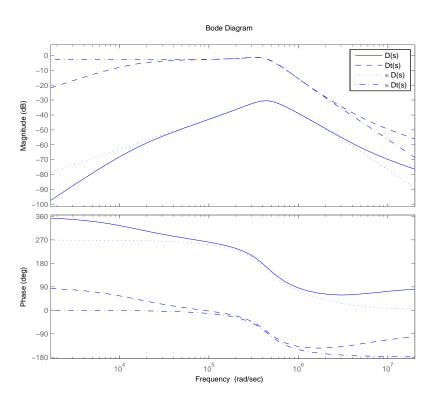

| 4.7               | Bode plot of $D(s)$ (solid), $\tilde{D}(s)$ (dashed), and their approximations (dotted and dash-dotted respectively) | 74       |

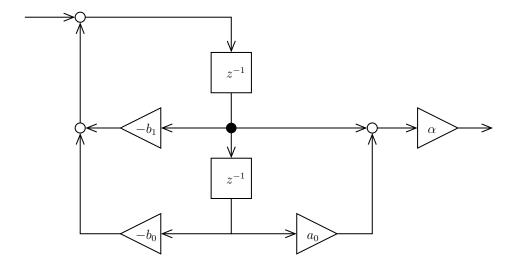

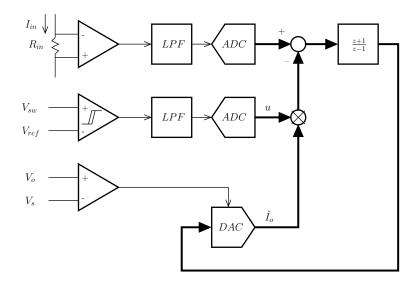

| 4.8               | Implementation of digital filter $\tilde{D}(z)$                                                                      | 75       |

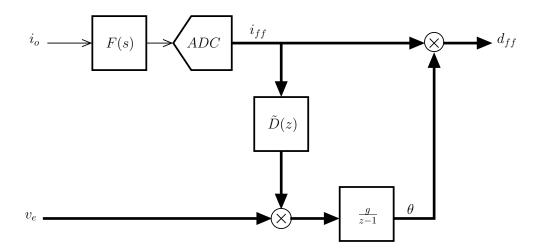

| 4.9               | Adaptive feedforward implementation. Digital signals are shown with                                                  |          |

|                   | bold lines                                                                                                           | 76       |

| 4.10              | Experimental setup: power train board                                                                                | 78       |

| 4.11              | Experimental setup: FPGA board                                                                                       | 79       |

| 4.12              | Experimental setup: boards interconnected                                                                            | 79       |

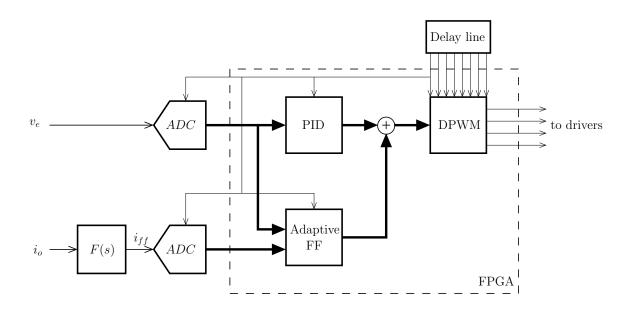

|                   | FPGA implementation block diagram                                                                                    | 80       |

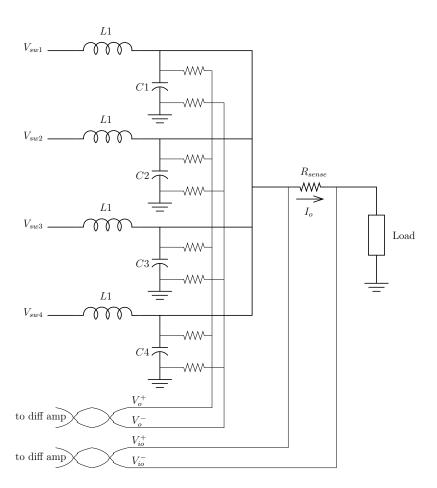

|                   | Sensing circuits                                                                                                     | 81       |

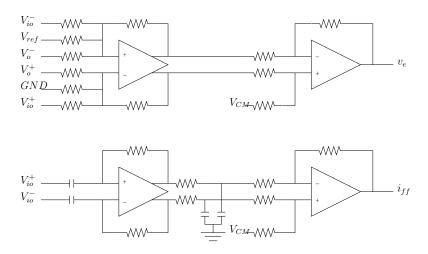

|                   | Signal conditioning circuits                                                                                         | 82       |

| 4.16              | Step response with feedback only. Top: $v_o$ , middle: $i_{ff}$ , and bottom:                                        |          |

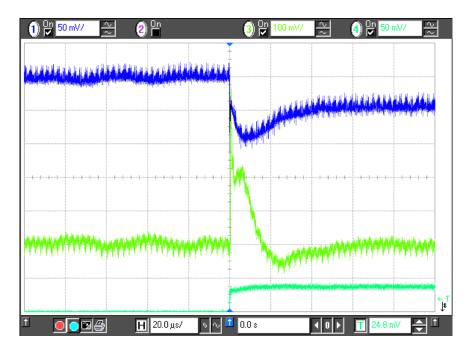

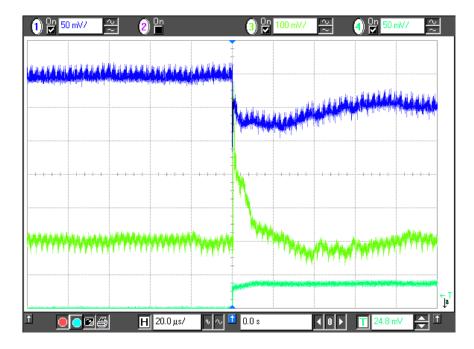

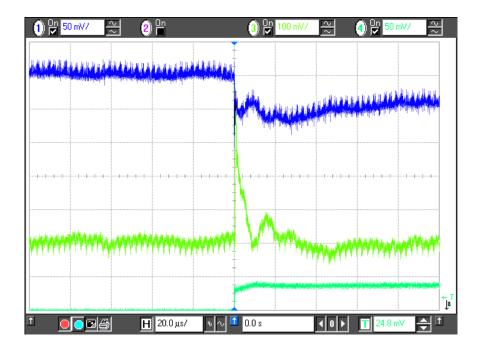

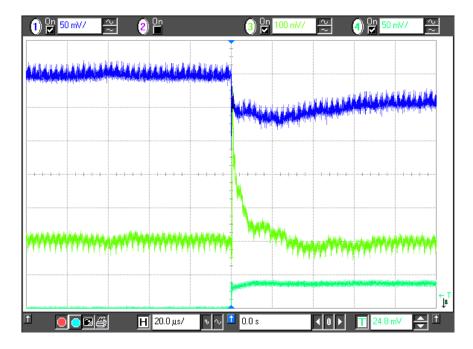

|                   | $i_0$                                                                                                                | 83       |

| 4.17              | Step response with fixed-gain feedforward (small value). Top: $v_o$ , middle: $i_{ff}$ , and bottom: $i_o$                                                                                            | 83                |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 4.18              | Step response with fixed-gain feedforward (large value). Top: $v_o$ , middle: $i_{ff}$ , and bottom: $i_o$                                                                                            | 84                |

| 4.19              | Step response with adaptive feedforward. Top: $v_o$ , middle: $i_{ff}$ , and bottom: $i_o$                                                                                                            | 84                |

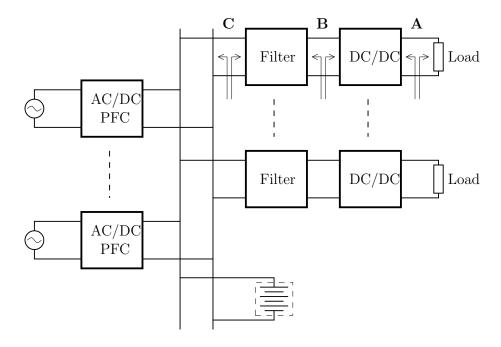

| 5.1<br>5.2<br>5.3 | Typical DPS diagram                                                                                                                                                                                   | 89<br>92<br>92    |

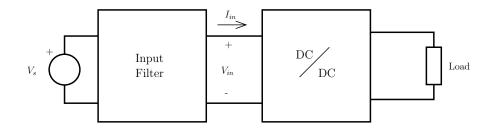

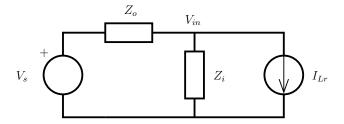

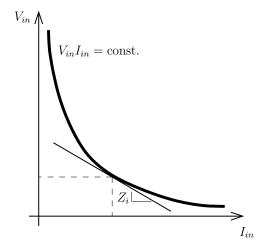

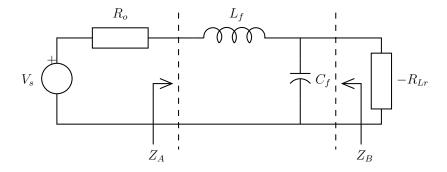

| 5.4<br>5.5        | Equivalent circuit of a power converter connected to an input filter Negative input impedance of a constant-power converter                                                                           | 93<br>95          |

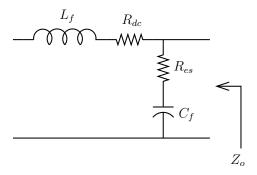

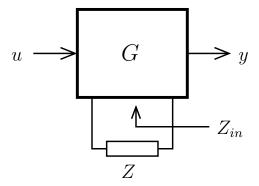

| 5.6<br>5.7<br>5.8 | Input filter                                                                                                                                                                                          | 96<br>98<br>100   |

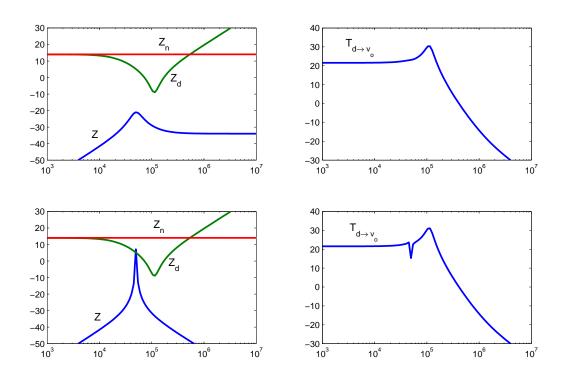

| 5.9               | Effect of input filter in buck converter dynamics. Top: Damped input filter. Bottom: Undamped input filter                                                                                            | 103               |

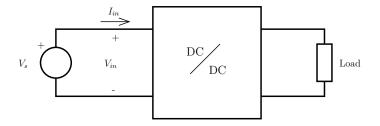

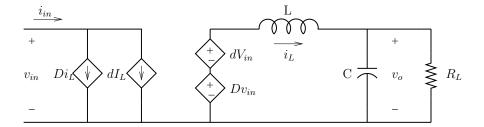

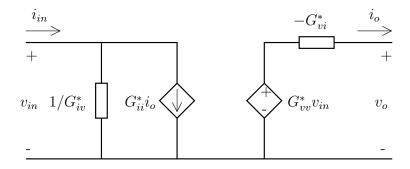

| 5.11              | DC/DC converter model                                                                                                                                                                                 | 106               |

| 5.13              | Two-port model of a closed-loop DC/DC converter DC/DC converter with input filter. Multivariable model case DC/DC converter with input filter. Two-port model case                                    | 106<br>107<br>108 |

| $5.15 \\ 5.16$    | Small-signal model of buck converter with parasitic resistances Implementation of the G-parameter two-port model. Open-loop case. Implementation of the G-parameter two-port model. Closed-loop case. | 109<br>110<br>111 |

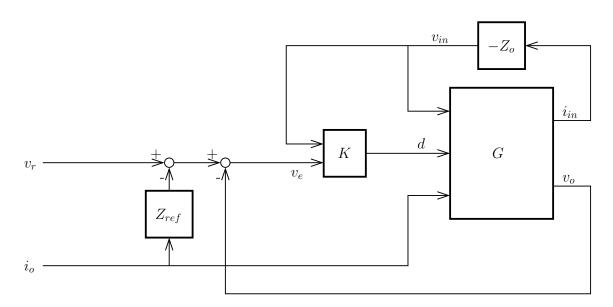

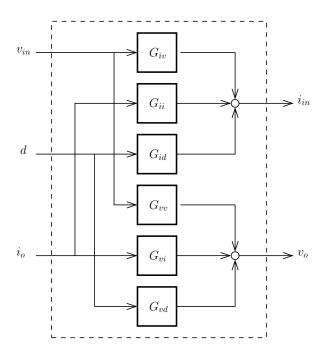

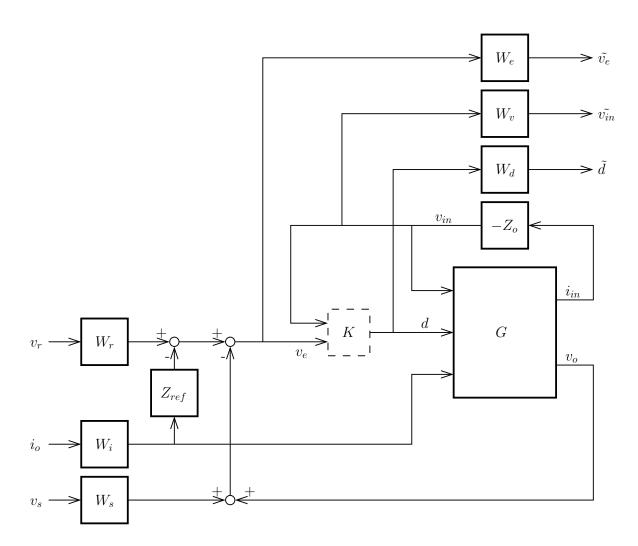

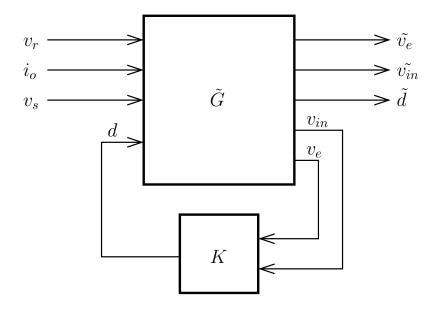

| 6.1               | Voltage mode control of a DC/DC converter with load-line and input voltage feedforward, in the presence of an input filter                                                                            | 117               |

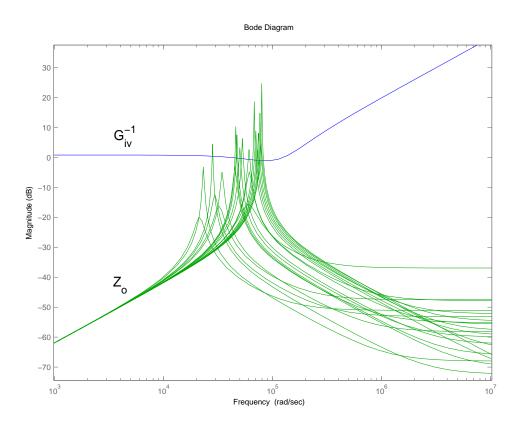

| 6.2<br>6.3        | Internal structure of block $G$                                                                                                                                                                       | 118               |

| 6.4               | of different parameter values                                                                                                                                                                         | 121               |

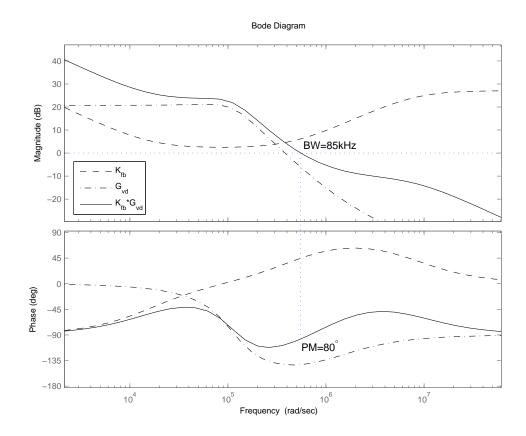

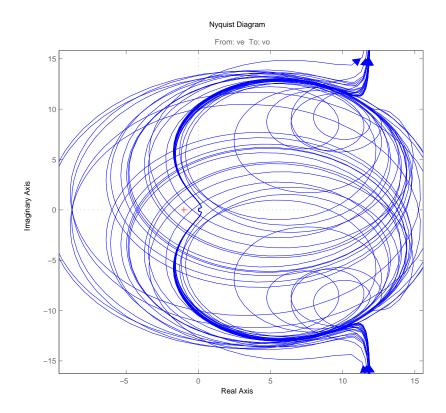

| 6.5               | plant (dash-dotted line), and the resulting loop gain (solid line) Set of Nyquist plots of the feedback PID design for different input filter parameters                                              | 122<br>123        |

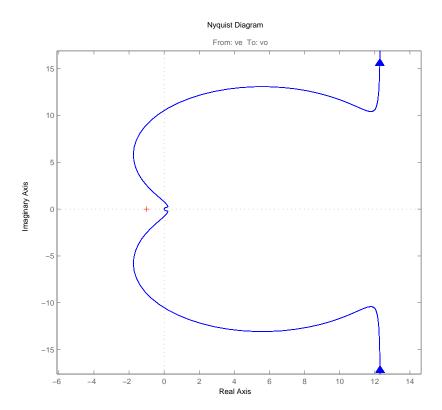

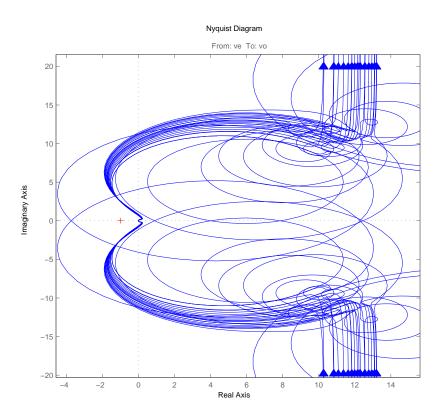

| 6.6<br>6.7        | Nyquist plot of the feedforward design under ideal conditions Nyquist plot of the feedforward design with variations in the input                                                                     | 125               |

| 6.8<br>6.9        | voltage                                                                                                                                                                                               | 126<br>128<br>129 |

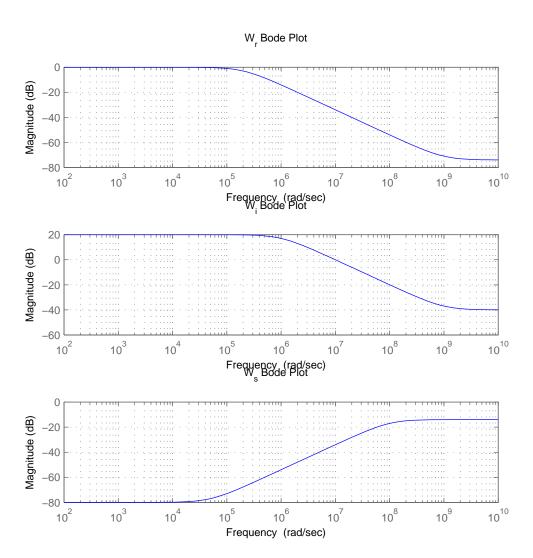

| 6.10 | Weighting functions for the inputs                                            | 130 |

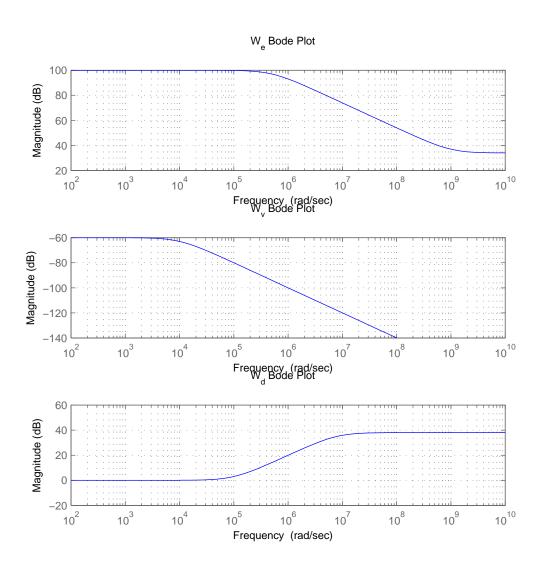

|------|-------------------------------------------------------------------------------|-----|

| 6.11 | Weighting functions for the outputs                                           | 131 |

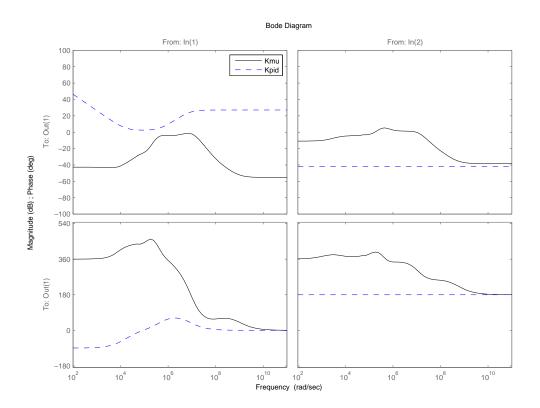

| 6.12 | Bode plot of the $\mu$ controller (solid) compared with the PID controller    |     |

|      | (dashed). Left: error voltage to duty-cycle transfer function. Right:         |     |

|      | input voltage to duty-cycle transfer function. Top: magnitude. Bot-           |     |

|      | tom: phase                                                                    | 133 |

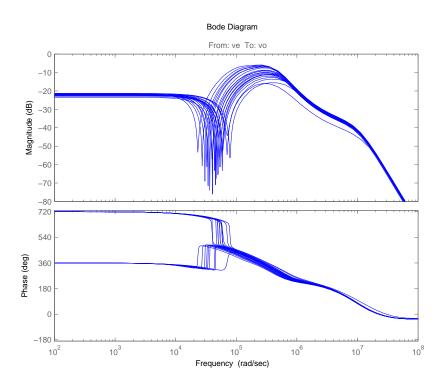

| 6.13 | Set of Bode plots of the loop with the $\mu$ controller for different input   |     |

|      | filter parameter values                                                       | 134 |

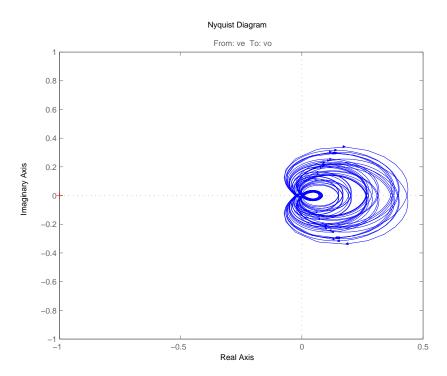

| 6.14 | Nyquist plot of the loop with the $\mu$ controller for different input filter |     |

|      | parameter values                                                              | 135 |

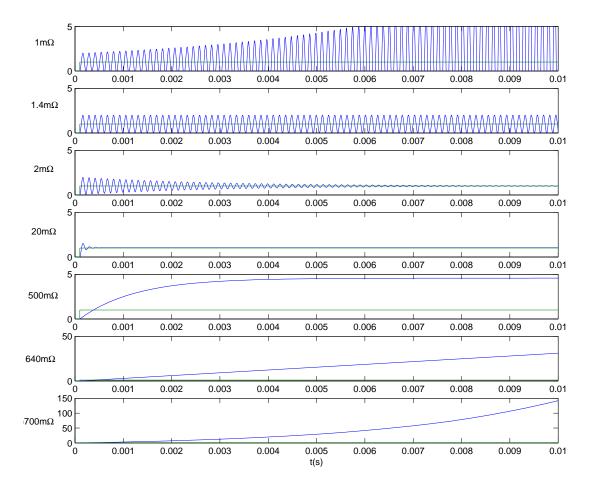

| 6.15 | Simple DPS architecture.                                                      | 136 |

| 6.16 | Equivalent circuit of simple DPS architecture                                 | 137 |

| 6.17 | Simulation of the virtual damping example with different values of $R_o$ .    |     |

|      | Response to an input voltage step                                             | 140 |

| 7.1  | Mixed-signal implementation of the output current sensing method.             |     |

|      | Digital signals are shown with a bold line                                    | 146 |

# List of Tables

| 1.1 | Summary of VRM state of the art                 |

|-----|-------------------------------------------------|

| 2.1 | Popular current sensing methods                 |

| 2.2 | Breadboard components                           |

| 2.3 | Power train components and parameters           |

| 3.1 | Number of operations for two estimation methods |

| 3.2 | VRM evaluation board characteristics            |

| 4.1 | FPGA board characteristics                      |

| 4.2 | Power train board characteristics               |

| 6.1 | Representative VRM application values           |

| 6.2 | Input filter values                             |

### Acknowledgments

I thank my advisor Professor Seth Sanders for his support and guidance during these five years. From him I learned how to approach a research problem with a rigurous theoretical foundation as well as a clear understanding of its technological and economic context. His constant pursuit of excellence in research and his attitude towards the academic world taught me a strong lesson in professional integrity.

Along with Professor Sanders, I want to thank Professors Robert Meyer, Bernhard Boser, and Roberto Horowitz for serving on my qualifying exam committee, and for their insightful comments. I also thank Professors Sanders, Meyer, and Horowitz for reading this thesis.

I am indebted to my home institution, Universidad de la República, for encouraging my academic development, and the Fulbright Comission for giving me the opportunity to pursue graduate studies in the United States. I am also indebted to Professor Aleksandar Stanković of Northeastern University for his advice.

I thank my colleagues at the Power Electronics Group for all the good moments spent together: Kenny Zhang, Artin Der Minassians, Angel Peterchev, Matt Senesky, Perry Tsao, Jinwen Xiao, Jason Stauth, Mike Seeman, Evan Reutzel, and Zachary Norwood. Special thanks to Kenny for sharing many hours in the lab working on the hardware, and to Artin for helping me get through the final stages of the thesis submission process.

During my internship at Fairchild Semiconductor I learned a lot about engineering

in the semiconductor industry. I thank Francesco Carobolante for his support, Rendon

Holloway for his mentorship, Steve Cartier for his assistance in the lab, and also Shey

Haniyur, Ron Berthiaume, and Jason Guo, from whom I learned very valuable lessons.

I thank Tien Han and Tim Ng for their help in building the hardware of some of my

experiments.

This work was supported by the UC Micro program, Fairchild Semiconductor,

Linear Technology, and National Semiconductor.

Finally, I want to express my love to my wife Sônia whose constant support and

encouragement helped me move ahead in difficult times, and my son Fabio for teaching

me the many things I had already forgotten.

Gabriel Eirea

Berkeley, August 2006

# Part I

# Estimation Techniques in VRM Applications

# Chapter 1

## Introduction

## 1.1 VRM and DPS applications

For over 40 years the semiconductor industry has been evolving steadily following Moore's Law, which states that the number of transistors on a chip roughly doubles every two years [2]. The trend was first observed in 1965 and it is predicted to continue at least until 2020 [3]. The implications of this trend are striking. As the size of transistors decreases, their speed increases and more functionality can be incorporated on a single chip at a reduced cost. As a consequence, digital integrated circuits (ICs) became ubiquitous in our society and have improved dramatically our standard of living. Semiconductors have become a \$200 billion industry and the foundation for the trillion-dollar electronics industry [2].

At the forefront of this revolution are the highly integrated digital processing ICs, especially general-purpose microprocessors. These devices offer a tremendous computing power at a low cost. Communication systems, data servers, desktop computers at home and the office, and portable devices are some of the applications powered by microprocessors that define the landscape of modern life.

The increasing number of transistors and speed of operation creates an increase in the power consumption of the devices. As size is also reduced, the ability to dissipate the heat generated in the IC is diminished. Consequently, temperatures inside the chip can get close to the thermal limit of silicon. This is one of the reasons why power consumption needs to be reduced. Another important reason is the growing concern on the efficient use of energy resources in the planet, with initiatives like "Energy Star" in the United States [4].

The power consumed by a digital IC can be estimated as

$$P = knCV^2 f (1.1)$$

where k is an utilization factor, n is the number of transistors, C is the capacitance of a transistor, V is the supply voltage, and f is the frequency of operation. The values of n and f are continuously increasing in order to offer more computing power. At the present, modern microprocessors have hundreds of millions of transistors and clock frequencies of several Gigahertz, and the trend is to increase these parameters [1]. Since C is mostly constant for a given technology, the two variables that can be

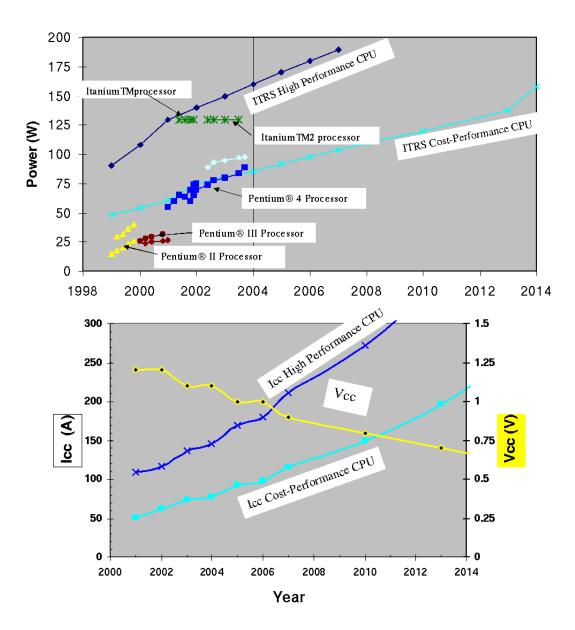

used to reduce the power consumption are k and V. Effectively, the voltage V has been gradually decreasing from 5V to below 1V over the years. Probably the biggest improvement in power reduction for microprocessors comes from power management techniques that allow turning off parts of the circuit that are not being used, therefore reducing the factor k. However, this power reduction technique creates large and fast current transients when the microprocessor sends to sleep or awakes large logic blocks. Some of these trends are shown in Fig. 1.1 [1].

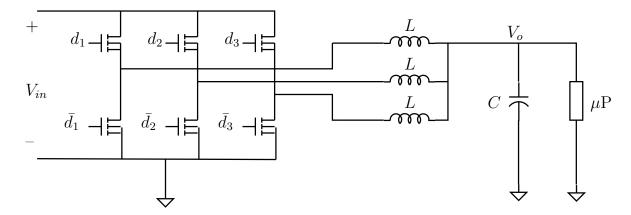

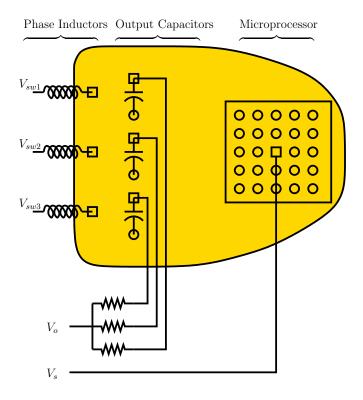

The circuit that delivers the power to the microprocessor is usually called a Voltage Regulator Module (VRM). The preferred architecture for this power converter is the multiphase buck converter with synchronous rectification (Fig. 1.2). This architecture reduces the ripple both of the output voltage and the input current, allowing for smaller filter components. Since the load is shared by the different phases, the maximum rating of the semiconductors and inductors is decreased, becoming a cost-efficient solution for high-current applications such as VRM [5].

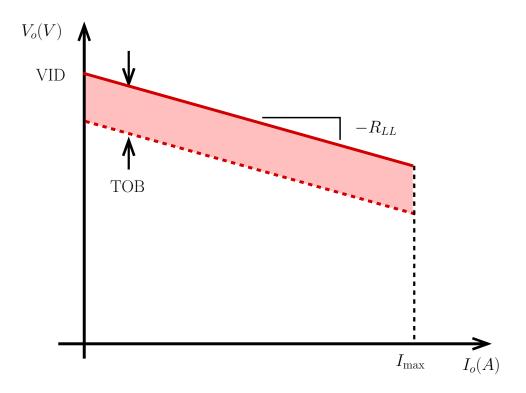

A technique called Adaptive Voltage Positioning (AVP) was adopted in order to reduce the number of output capacitors by allowing the output impedance of the converter to be different from zero [6]. This technique requires that the output voltage follow a "load-line" that depends on the output current; the slope of the load-line is typically around  $1m\Omega$ . The output voltage specification is completed with the definition of a tolerance band (TOB) that includes the tolerance both for

Figure 1.1: Trends in VRM applications. (Extracted from [1].)

Figure 1.2: Multiphase buck converter with synchronous rectification. Three-phase example.

steady-state variations of the voltage (due to ripple or offset voltages) and dynamic variations during load current transients. This is illustrated in Fig. 1.3.

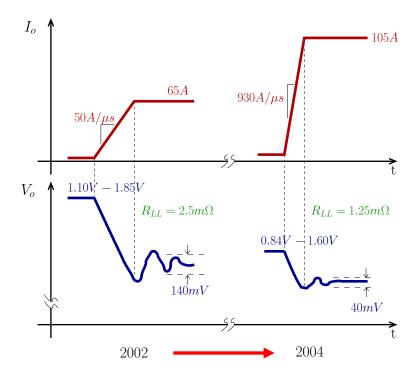

The state of the art specifications for VRM systems is summarized in Table 1.1 [7]. The trend in VRM specifications is to have larger load currents, faster and larger load transients, lower output voltage, and tighter tolerances (Fig. 1.4). The challenge is to comply with these specifications, while at the same time meeting the market requirements in terms of cost, efficiency, high power density, and low profile.

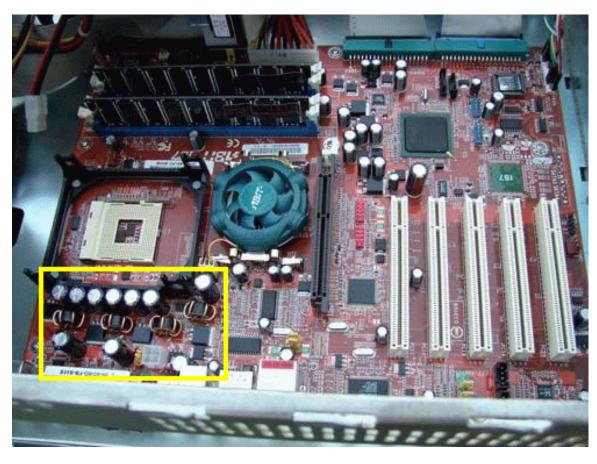

A typical motherboard is shown in Fig. 1.5 with the VRM area outlined. While most of the components in a motherboard are reduced in size and integrated, the VRM has not been able to reduce its size and uses a larger proportion of the real estate. It is estimated that up to 30% of the motherboard area is used by power delivery circuits, mostly by the VRM [8]. The same source cites the trend towards more compact form factors, making the size problem a very important one.

Figure 1.3: Adaptive Voltage Positioning.

Table 1.1: Summary of VRM state of the art.

| Multiphase buck converter with synchronous rectification |                    |  |

|----------------------------------------------------------|--------------------|--|

| Automatic Voltage Positioning (load-line)                |                    |  |

| Input voltage                                            | 12V                |  |

| Dynamic output voltage reference                         | 0.8 - 1.6V         |  |

| Tolerance band                                           | 40mV               |  |

| Output current                                           | 1 - 120A           |  |

| Output current slew-rate                                 | up to $900A/\mu s$ |  |

| Load-line impedance                                      | $1.25m\Omega$      |  |

Figure 1.4: Illustration of the evolution of VRM specifications: faster and larger load transients with tighter regulation of the output voltage.

Figure 1.5: Motherboard Abit IS7 with VRM controller Intersil HIP6301CB. (Extracted from http://www.lostcircuits.com)

The output capacitors account for a large part of the cost and size of the VRM. Most of the research efforts and commercial developments target the reduction of the output capacitance. This is one of the reasons why AVP and the multiphase buck architecture were introduced, besides having other benefits. Control strategies can also help reduce the output capacitance, such as the case of output current feedforward [9] that motivates most of the work in this thesis.

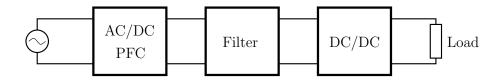

Delivering power to big and complex digital ICs is becoming a challenge not only for microprocessors, but also graphic processors, memories, and others. In data centers and communication systems, power has to be delivered to racks and boards in a room. This creates the need to a careful design of the whole power delivery architecture. DC Distributed Power Systems (DPS) are increasingly common and pose new challenges in terms of stability and performance of the interconnected sources, filters, power converters, and loads [10]. The most used DPS architecture is the Intermediate Bus Architecture (IBA), in which nonisolated Point Of Load (POL) converters provide local voltage regulation from a mildly regulated intermediate voltage.

Analysts see increasing price pressures in the DC/DC market, slowing down the growth rates. Commoditization of some market segments, most notably PCs and related products, lead to this phenomenon. Although the volume of sales is expected to continue to grow steadily, the DC/DC converter market annual growth is estimated at 5.7% [11]. The power management IC segment was a \$5 billion market in 2002

and is estimated to be around \$8 billion today [12].

The subject of this thesis is the improvement of control strategies for power delivery circuits in VRM and DPS applications, which lie at the base of the Information Technology revolution.

## 1.2 Thesis overview

This thesis is organized in two parts. In Part I, three contributions in the area of control of DC/DC converters, in particular VRM applications, are presented.

The subject of Chapter 2 is an output current sensing method based on the on-line calibration of parasitic resistance elements on the power train. This method allows for an accurate, efficient, and low cost sensing of the output current in high-current buck converters. In VRM applications, this enables not only load-line tracking but also output current feedforward for improved transient response.

In Chapter 3, a current unbalance estimation algorithm for multiphase buck converters is presented. The algorithm requires sensing a single voltage and processing the information digitally. The processing cost is low, since it involves operations that can be scheduled over a relatively long time interval.

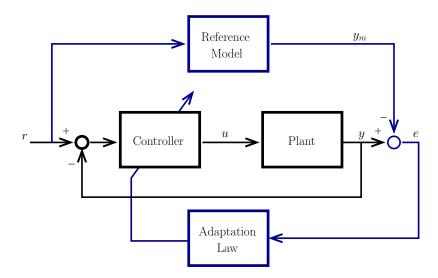

Chapter 4 presents an adaptation method to tune the output current feedforward path in a VRM application. Transient response to fast and large current variations can be improved with output current feedforward, as long as the parameters match

those of the plant. This adaptive control method tunes the critical parameter in the feedforward path so that the voltage error during transients is minimized.

These three contributions are tightly related and together can be applied to a VRM system for improved performance. However, each technique could be applied independently on this or other applications. The methods described in Chapters 2 and 3 comprise a total current sensing solution for VRM applications, or other low voltage, high-current applications. The method described in Chapter 4 assumes that the output current information is available by some method, for example using the method described in Chapter 2, but other methods could be used.

In Part II, theoretical aspects of the interconnection of power converters are analyzed. Chapter 5 presents an overview of the problem of impedance interactions between a power converter and an input filter, or between any interconnection between power converters. This problem is relevant due to the prevailing use of DC Distributed Power Systems for power distribution at all levels: at a room level in data centers or communication systems, at a motherboard level in computing applications, and even at a chip level in complex integrated circuits. With a comprehensive literature review and numerous examples, this chapter is intended as a survey of the most relevant results in this area.

In Chapter 6 the fundamental limits of performance in interconnected power systems are explored, and an alternative solution for the specific case of a power converter

with an undamped input filter is proposed. This solution is intended to serve as an example of a design approach that is based on a system-level view of the problem. By designing properly the impedances of the various interconnected subsystems, the fundamental limits of performance can be avoided without resorting to the prevailing design method of adding capacitors and damping the filters, which adds cost, size, and weight to the system.

Finally, the main contributions of this thesis are outlined in Chapter 7, together with suggestions for future research topics.

# Chapter 2

# **Output Current Estimation**

In this chapter, a method for the on-line calibration of a circuit board trace resistance at the output of a buck converter is described. The input current is measured with a precision resistor and processed to obtain a DC reference for the output current. The voltage drop across a trace resistance at the output is amplified with a gain that is adaptively adjusted to match the DC reference. This method is applied to obtain an accurate and high-bandwidth measurement of the load current in the modern microprocessor voltage regulator application (VRM), thus enabling an accurate DC load-line regulation as well as a fast transient response. Experimental results show an accuracy well within the tolerance band of this application, and exceeding all other popular methods.

Method Accuracy Efficiency Cost Comments Hall effect high high very high not used Sense resistor at the output high very low medium not used Sense resistor at the input medium medium medium not used  $R_{DS}$ low high low used for balancing Inductor sensing preferred solution medium high low SENSEFET medium special MOSFETs high high

Table 2.1: Popular current sensing methods.

## 2.1 Introduction

Voltage regulators for modern microprocessors (VRMs) pose unprecedented demands on DC-DC power converters, in terms of regulation, bandwidth, and cost [7]. Adaptive Voltage Positioning (AVP), also known as load-line regulation, was adopted as an effective technique to reduce the amount of capacitance at the output [6]. This technique requires the output voltage to change with the load current, as if the output impedance of the power converter were a resistor of small value (around  $1m\Omega$ ). The controller can be designed to make the effective closed-loop output impedance resistive, or to meet another desired specification, over a wide frequency range, by processing the output current information [6].

For this reason, and due to the tight regulation window required by the application, a precise and high-bandwidth measure of the output current is needed. Existing current-sensing techniques are shown and compared in Table 2.1 [13, 14].

Other methods have been proposed but are not used commercially. An on-line

calibration method for MOSFET  $R_{DS}$  sensing that requires additional power train components, was described in [15]. An observer-based approach requiring intensive numerical processing was reported in [16].

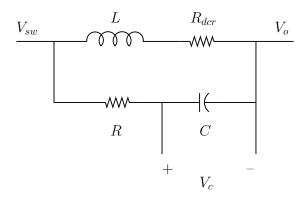

For efficiency, cost, and relative accuracy, inductor sensing is the preferred method at the present time [7]. The method is illustrated in Fig. 2.1. The relationship between the capacitor voltage and the inductor current in the frequency domain is:

$$I_L = \frac{V_{sw} - V_o}{Ls + R_{dcr}} = \frac{1}{R_{dcr}} \cdot \frac{V_{sw} - V_o}{\frac{L}{R_{dcr}}s + 1}$$

(2.1)

$$V_c = \frac{V_{sw} - V_o}{RCs + 1}. (2.2)$$

If  $RC = \frac{L}{R_{dcr}}$ , then

$$V_c = R_{dcr} I_L \tag{2.3}$$

It can be appreciated that this method has the disadvantage that both the effective series resistance  $R_{dcr}$  and the L/R time constant of the inductor need to be known and tracked as they change with temperature.

Most of the methods described above sense the inductor current, which has the same DC value as the output current, and tracks it well up to the closed-loop bandwidth of the converter. In designs with electrolytic capacitors, the output capacitor's ESR is chosen to be equal to the desired output impedance, as given by the load-line specification. This allows the converter to follow the load-line ideally at an arbitrary high bandwidth [6]. However, if ceramic capacitors are used the ESR is substantially

Figure 2.1: Inductor sensing.

lower than the load-line impedance rendering the previous design method impractical. The concept of generalized load-line was introduced in [9] as a practical design objective for VRM systems with ceramic capacitors. The bandwidth in such a system is given by the time constant  $\tau = R_{LL}C_o$  where  $R_{LL}$  is the desired load-line and  $C_o$ is the output capacitor value. In some cases it could be very difficult to follow the load-line over this frequency range, especially as  $C_o$  is decreased to reduce costs. In order to enhance load-line tracking without pushing the feedback bandwidth close to instability, output current feedforward was proposed [9]. In this case, the inductor current information is not useful and the load current must be sensed. In [9] the authors used inductor sensing together with an analogous technique to sense the output capacitor current, and combined both to obtain the output current. Thus, the method used poses the same practical challenges as inductor sensing.

The objectives of this research is to develop a current sensing method with the

following characteristics:

- 1. Output current sensing. By sensing the output current, a high bandwidth signal is obtained that can be used in an output current feedforward scheme to improve the transient response of the system.

- 2. Accuracy of 1%. It is estimated that inductor sensing accuracy is about 8%. This means that at 100A in a 1mΩ load-line the voltage error is ±8mV. As a consequence, the designer has to assign an inductor sensing error budget of 16mV out of a 40mV tolerance band (TOB). With a more accurate sensing method the error budget could be reduced to 2mV, thus relaxing the constraints for other circuit components.

- 3. **Efficient.** In high-current applications such as in the VRM, the designer cannot afford to put additional components in the power train.

- 4. Low cost. This is always a desired objective, especially in a commoditized applications such as the VRM. In practice this means, among other things: reduced bill of materials (BOM), low pin-count, little extra IC complexity.

In this chapter, a method that approaches these ideal conditions is presented. The method senses the output current by using the output trace resistance (or any parasitic resistance at the output of the converter) as a sensing element. The value of the trace resistance is calibrated on-line by a slow estimation loop. The estimation

Figure 2.2: Buck converter

algorithm is based on the DC correspondence between the output current and the input current. The latter is accurately measured with a sense resistor and used as a reference. This method can achieve high-accuracy and high-bandwidth measurement of the output current with a small efficiency penalty due to the input-side resistor. Further, the measured input current may be useful for control purposes.

## 2.2 Method description

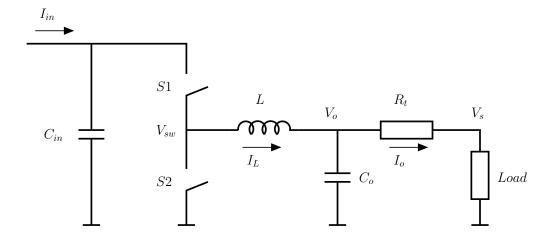

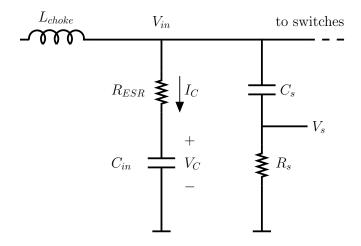

Fig. 2.2 shows a buck converter. The output trace resistance is shown explicitly as element  $R_t$ . The input current  $I_{in}$  is measured by placing a sense resistor before the input capacitor. Usually an inductor is located at this place as a choke, so this current is mostly DC and free of high frequency noise. In steady-state, the average current through the input capacitor is zero, so the average current through the high-

side switch is being effectively measured. This current can be ideally expressed as  $uI_L$ , where  $I_L(t)$  is the inductor current, and

$$u(t) = \begin{cases} 1, & \text{if S1 is ON} \\ 0, & \text{if S1 is OFF.} \end{cases}$$

(2.4)

It can also be argued that the average current through the output capacitor is zero, so the average inductor current is equal to the average output current. Then,

$$\langle I_{in} \rangle = \langle uI_L \rangle \tag{2.5}$$

$$\langle I_L \rangle = \langle I_o \rangle$$

(2.6)

where  $\langle \bullet \rangle$  indicates the DC or average component of the signal. In steady-state and in continuous conduction mode (CCM), it holds that

$$\langle uI_L \rangle = \langle uI_o \rangle$$

(2.7)

as illustrated in Fig. 2.3. Therefore, it can be concluded that

$$\langle I_{in} \rangle = \langle uI_o \rangle.$$

(2.8)

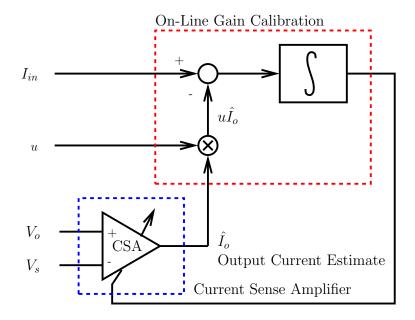

This relationship establishes the basis of the on-line calibration algorithm. In Fig. 2.4 a block diagram of the estimation loop is shown. The current sense amplifier (CSA) measures the voltage drop on the trace resistance  $(V_o - V_s)$ . Its output is the estimated current  $\hat{I}_o$ . This value is multiplied by the function u(t), simulating the operation of the top switch. The difference between this signal and the input

Figure 2.3: In steady-state and CCM,  $\langle uI_L \rangle = \langle uI_o \rangle$  because the areas of the shaded triangles are equal.

current  $I_{in}$  is sent to the input of an integrator, whose output sets the gain of the CSA, therefore closing the loop and forcing the integrator to converge to the correct gain. If the gain is too low, the input of the integrator will be positive and the gain will increase, and vice versa. The loop will converge to set the gain such that the condition expressed in (2.8) is met, therefore achieving the desired result  $\hat{I}_o = I_o$ . The bandwidth of this adaptive tuning loop should be slow enough as to average-out the effect of switching and load transients, but fast enough to allow for tracking temperature changes. This gives a practical criteria to set the gain of the loop. A low bandwidth is also needed to guarantee the stability of the adaptive loop.

Notice that, although the adaptation loop is slow, the actual measurement of the

Figure 2.4: Current sense amplifier with gain estimation loop.

output current is high-bandwidth, because it is given by the voltage drop  $V_o - V_s$  across the passive trace resistance amplified with a variable gain amplifier.

The magnitude of the differential voltage  $V_o - V_s$  has to be such that the signal can be resolved. This means that there is a trade-off between the signal amplitude and the power loss due to the trace resistance. This trade-off results in the selection of a specific PCB layout and impacts the characteristics of the CSA.

As an example, consider a representative example of a VRM with a maximum load current equal to 100A, an output voltage equal to 1V, and a trace resistance of  $0.2m\Omega$ . At the maximum current, the voltage drop  $V_o - V_s$  would be equal to 20mV. This represents a power loss of 2W over the 100W delivered to the load.

Since the typical efficiency for this application at full load is in the range of 75-85%, the impact of the power loss due to the trace resistance is acceptable. For a 1% sensing accuracy, it is necessary to resolve  $200\mu V$  out of the 20mV voltage drop. The bandwidth desired for this measurement is on the order of a few megahertz. A CSA with these characteristics is possible with current technology.

# 2.3 Method analysis

Some of the assumptions made in the previous section are valid only in ideal circuits. First, there are many factors that make (2.8) only an approximate equation. Second, the PCB trace that goes from the output capacitors to the load behaves as a two-terminal resistor only over a certain bandwidth due to parasitic elements. These issues are addressed in the following subsections.

## 2.3.1 Errors due to simplified switching model

In a practical implementation, (2.8) is only approximate. The sources of error are described below.

#### Reverse recovery

Not all the current that goes through the high-side switch flows to the inductor.

A correction has to be made to the input current information in order to reflect

more accurately the inductor current. Some of the charge that flows through the high-side MOSFET ends up charging/discharging parasitic capacitances and, most importantly, are recombined in the low-side MOSFET's antiparallel diode (reverse recovery). This effect can be modeled by rewriting (2.5) as [17, pp. 244-247]

$$\langle I_{in} \rangle = \langle uI_L \rangle + Q_{rr}f_s + t_{rr}f_s \langle I_L \rangle$$

(2.9)

where  $Q_{rr}$  is the reverse recovery charge,  $t_{rr}$  is the reverse recovery time, and  $f_s$  is the switching frequency. This equation includes both the effect of the charge flowing to the diode and the delay in the switching node voltage due to the reverse recovery time. Rearranging terms, and introducing (2.7), it is concluded that

$$\langle I_{in}\rangle \left(1 - \frac{t_{rr}f_s}{D}\right) - Q_{rr}f_s = \langle uI_o\rangle.$$

(2.10)

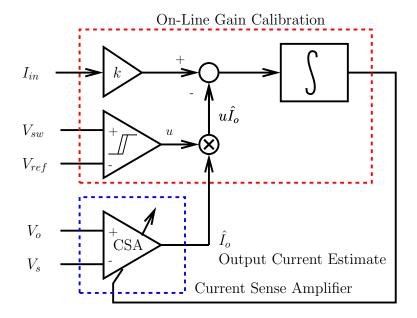

This expression is more accurate than (2.8), and can be easily contemplated in the estimation circuit of Fig. 2.4 by introducing a gain factor slightly less than unity. In practice, the constant term  $Q_{rr}f_s$  is very small (comparable to the voltage offset of the amplifiers), so it can be neglected. The gain factor is represented in Fig. 2.5 by the block with gain  $k = 1 - \frac{t_{rr}f_s}{D}$ .

#### Switching command delay

The function u(t) is an idealization of the switching action. In practice, there is a delay between the gate-drive command and the effective switching. This error can be

reduced by extracting u directly from the switching node, and not from the gate-drive command. This implementation is illustrated in Fig. 2.5 by introducing a hysteretic comparator to sense the switching node voltage.

#### **Transients**

It is clear that (2.8) was derived under the assumption of steady-state operation, since it is based on the fact that the average current on the input and output capacitors is zero. Besides, the output voltage changes with the load due to Adaptive Voltage Positioning (AVP), so some of the current through the inductor goes into charging/discharging the output capacitor during load transients. However, the effect of transients on the adaptation algorithm is negligible provided that the adaptation is slow enough. The following analysis illustrates how to set bounds on the adaptation loop bandwidth.

Assume there is an output current step  $\Delta I_o$ , then the average inductor current will converge exponentially to the new output current value with time constant equal to  $\tau = R_{LL}C_o$ , where  $R_{LL}$  is the load-line value and  $C_o$  is the output capacitor value [9]. During the transient, (2.6) is not valid, since the difference between  $\langle I_o \rangle$  and  $\langle I_L \rangle$  is equal to  $\Delta I_o \exp^{-t/\tau}$ . The integral of that difference is  $A_0 \Delta I_o \tau$ , where  $A_0$  is the gain of the integrator (i.e., the transfer function of the integrator is  $\frac{A_0}{s}$ ). If the relative

error due to this transient is bounded, then

$$\frac{A_0 \Delta I_o \tau}{1/R_t} < \epsilon \tag{2.11}$$

where  $1/R_t$  is the ideal gain of the CSA and  $\epsilon$  is the desired relative error. This equation gives the following upper bound in the integrator gain

$$A_0 < \frac{\epsilon}{\Delta I_o \tau R_t}.\tag{2.12}$$

For a representative VRM [7],  $\Delta I_o^{\rm max} = 100A$ ,  $\tau = 1\mu s$ , and  $R_t = 0.3m\Omega$ . With  $\epsilon = 0.5\%$ , then  $A_0 = 165 \times 10^3$ . The quantity of interest for this calculation is the loop bandwidth, that can be extracted from the circuit of Fig. 2.5 by linearization. The loop gain can be expressed as

$$H(s) = \frac{A_0}{s} I_o R_t D \tag{2.13}$$

therefore the loop bandwidth is

$$\omega_{BW} = A_0 I_o R_t D. \tag{2.14}$$

Notice that the bandwidth depends on the output current. The limitation in the integrator gain gives a bound in the loop bandwidth. For a typical current of 30A, this bandwidth is

$$\omega_{BW}^{\rm max} = 148 rad/s \tag{2.15}$$

or equivalently, a time constant of 42ms. This is fast enough to track any thermal transient.

Figure 2.5: Current sense amplifier with gain estimation loop, modified to contemplate non-ideal effects.

### Discontinuous Conduction Mode

The relationship (2.8) is valid only in CCM. The converter enters Discontinuous Conduction Mode (DCM) at light loads for some architectures. It is shown in Section 2.4 that the signal is so low at light loads, that the integrator needs to be stopped to prevent a drift in the estimate, so the adaptation loop should never operate in DCM.

# 2.3.2 Errors due to lumped resistance model

The output trace behaves resistively over a certain frequency range, but at high frequencies the parasitics of the PCB trace make the resistive model unrealistic. This imposes a practical limit in the bandwidth of the sensing method.

A first-order estimation of the frequency response of two parallel copper plates in a PCB is derived next. Consider a stripline consisting of a pair of rectangular copper plates of length  $\mathcal{L}$  and width  $\mathcal{W}$ , separated by a dielectric material of thickness  $h \ll \mathcal{L}, \mathcal{W}$  and relative permeability  $\mu_r \approx 1$ . When a current I flows lengthwise through one of them and returns in the opposite direction through the other, a magnetic field  $H = \frac{\mathcal{I}}{\mathcal{W}}$  is formed in the dielectric. The magnetic flux is then

$$\Phi = \mu_0 H \mathcal{L} h = \frac{\mu_0 \mathcal{L} h}{\mathcal{W}} \times I, \qquad (2.16)$$

so the inductance is

$$L = \frac{\mu_0 \mathcal{L}h}{\mathcal{W}}. (2.17)$$

The capacitance, on the other hand, can be computed using the well-known equation for a parallel plate capacitor

$$C = \frac{\varepsilon_r \varepsilon_0 \mathcal{L} \mathcal{W}}{h}.$$

(2.18)

If the cutoff frequency is estimated as  $f_c = \frac{1}{2\pi\sqrt{LC}}$  then the following result is obtained:

$$f_c = \frac{1}{2\pi\sqrt{\varepsilon_r\varepsilon_0\mu_0}\mathcal{L}}. (2.19)$$

Notice that the dependence on the width of the plate and the thickness of the dielectric cancel out, and the final result depends only on the length and the dielectric

constant. Actually, the product of the angular cutoff frequency and the stripline length  $2\pi f_c \mathcal{L} = \frac{1}{\sqrt{\varepsilon_r \varepsilon_0 \mu_0}}$  is the propagation speed of light in this medium.

Therefore, the trace can be approximated by an LC low-pass filter with a cutoff frequency given by (2.19). For a representative PCB (FR4)  $\varepsilon_r = 4.7$ , then the cutoff frequency can be expressed in international units as

$$f_c = \frac{22 \times 10^6}{\mathcal{L}}. (2.20)$$

For example, a 2cm trace would have a cutoff frequency of 1.1GHz. It is safe to state that the trace will behave resistively at least up to one decade below the cutoff frequency, in our example 110MHz. It is concluded that, for all practical purposes, the parasitic dynamic components of the PCB trace will not affect the measurement of the output current.

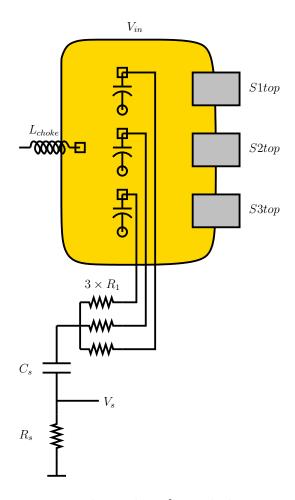

Another potential source of error is the fact that in a practical layout the  $V_o$  node is spread since there are many output capacitors in parallel. This is especially the case in multi-phase buck converters, where the phases are kept apart for thermal considerations. The actual output trace is a wide plate of copper. The lumped resistor model might not be adequate due to the difference in the current density in different portions of the plate, which varies during transients. This can be mitigated by measuring the voltage at  $V_o$  using the Kelvin sensing technique with a passive resistor network, so as to average out the voltage at different points in the plate. The technique is illustrated in Fig. 2.6 for a three-phase VRM.

Figure 2.6: Kelvin sensing technique with resistor averaging in a 3-phase VRM.

Finally, in a multi-phase buck converter, and under the assumption that the phase currents are balanced and the adaptation is slow enough to ignore transients, the signal u(t) can be obtained from the switching node of any phase.

# 2.4 Experimental results

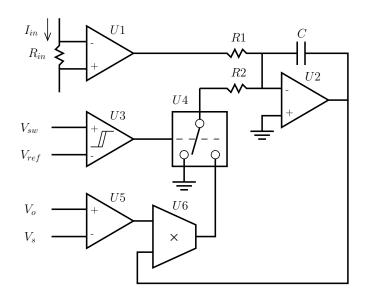

A prototype breadboard implementing the circuit in Fig. 2.5 was built using standard off-the-shelf parts. A simplified schematic of the board is shown in Fig. 2.7, and the main component values are shown in Table 2.2.

Figure 2.7: Estimation breadboard schematic (simplified).

${\bf Table~2.2:~Breadboard~components}$

| Component | Value       |  |

|-----------|-------------|--|

| U1        | AD623       |  |

| U2        | TL082       |  |

| U3        | AD8611      |  |

| U4        | ADG820      |  |

| U5        | AD620       |  |

| U6        | AD835       |  |

| $R_{in}$  | $10m\Omega$ |  |

| R1        | $33K\Omega$ |  |

| R2        | $33K\Omega$ |  |

| C         | $10\mu F$   |  |

Table 2.3: Power train components and parameters  $\,$

| Component/Parameter | Value                |  |

|---------------------|----------------------|--|

| VRM controller      | FAN5019              |  |

| # phases            | 3                    |  |

| $f_{sw}$            | 257kHz               |  |

| $V_{in}$            | 12V                  |  |

| $V_{out}$           | 1.2V                 |  |

| L (per phase)       | 680nH                |  |

| $\mathbf{C}$        | $8 \times 820 \mu F$ |  |

| top switch          | FDD6296              |  |

| bottom switch       | 2×FDD8896            |  |

| $t_{rr}$            | 27ns                 |  |

| $Q_{rr}$            | 12nC                 |  |

Figure 2.8: Prototype breadboard connected to the VRM evaluation board.

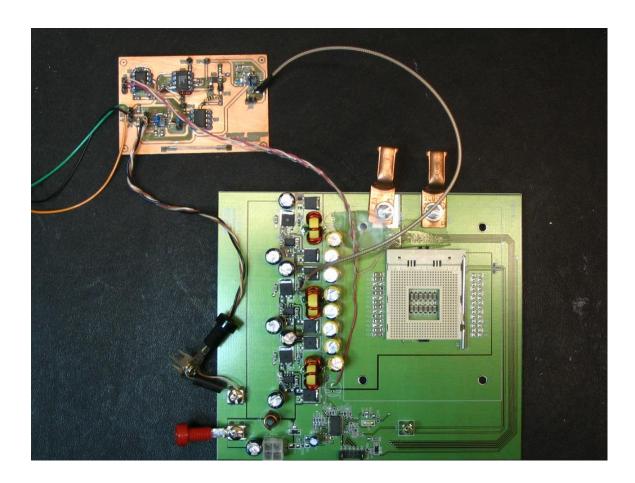

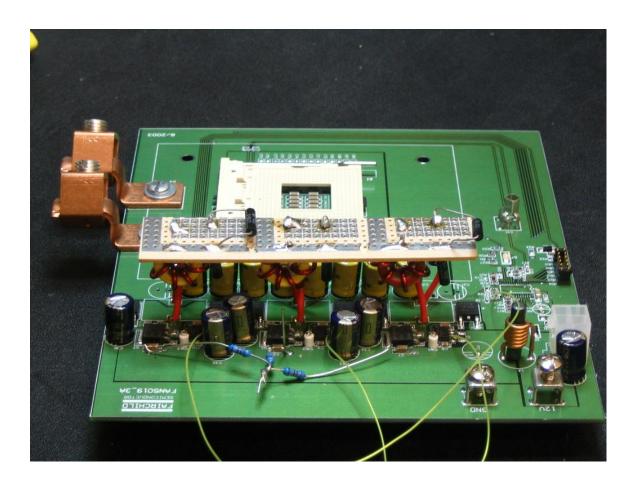

Notice that the factor k is implemented by changing the ratio of resistors R1 and R2. The board was connected to the 3-phase VRM evaluation board FAN5019\_3A of Fairchild Semiconductor, whose main characteristics are listed in Table 2.3. The current estimation error was assessed at DC while the VRM board was running at different loads. A picture of the breadboard connected to the evaluation board is shown in Fig. 2.8.

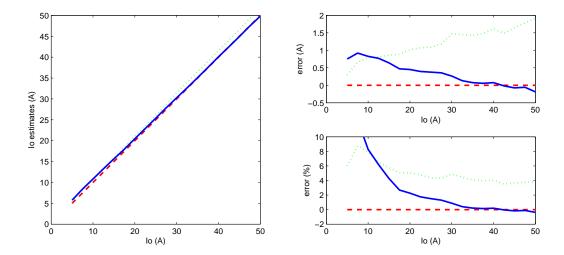

The results are shown in Fig. 2.9. The dotted line represents the measurements

Figure 2.9: Experimental measurements of the current estimation method. Left: measured values. Right: absolute (top) and relative (bottom) errors. (Dashed line: correct value; Dotted line: measurement without trimming; Solid line: measurement after trimming.)

performed without adjusting the input current reference  $(k = \frac{R2}{R1} = 1)$ . The solid line represents the measurements after trimming the gain in the input current path, accounting for the current loss due to reverse recovery. The trimming was done based on empirical observations; however the gain introduced agrees very well with the gain computed using (2.10) based on the MOSFET datasheet. The gain was modified by changing R1 to  $34K\Omega$  and R2 to  $32K\Omega$ , giving  $k = \frac{R2}{R1} = 0.94$ . The computed value from the datasheet was k = 0.93.

The absolute error remains low for the whole range of load currents, but the relative error is high at light load. At load values below 5A, the integrator in the estimation circuit starts to drift and reaches saturation. This is reasonable because

the signal level is too low to provide enough information, and the offset voltage of the amplifiers start to dominate the signal. The same situation arises if the converter enters DCM at light load. Although the absolute error in the current estimate is small, it is desirable to avoid this drift so that the integrator value is correct when the load steps up. For these reasons, the integration should be stopped at light load. From the results shown in Fig. 2.9, a threshold of 20A would guarantee an estimation error below 2%. To achieve this,  $R_t$  should be calibrated during operation at load currents above the threshold, and the calibration should be frozen at load currents below the threshold. Notice that, while the adaptive loop is frozen, the CSA still senses the output current with a constant gain, so the current measurement at light load is still accurate.

The architecture of the estimation circuit allows for an efficient mixed-signal implementation, in which the integration can be performed digitally, with the ability to stop the integration without drift, while the signal conditioning is performed in the analog domain.

## 2.5 Conclusions

This chapter describes a method that allows for an efficient, accurate, and highbandwidth measurement of the output current in a buck converter. This enables a VRM application to follow the load-line with precision, and to use output current feedforward for a fast transient response.

The method uses the PCB trace resistance at the output of the converter as a sensing element. A slow adaptive loop estimates the gain of the sensing amplifier based on the DC relationship between the output current and the input current, which is measured with a precision sense resistor. The effect of transients and switching non-idealities are quantified and included in the method derivation.

A breadboard was constructed and experiments show a precision better than 2% for currents above 20% of the rated maximum. The adaptation loop should never operate at low currents to avoid drifts in the estimate because of the the low signal level compared to the voltage offset of the amplifiers. The estimated current however is accurate for the whole operating range.

Although the method presented makes emphasis on tuning the resistance of the PCB trace, it could be equally used to tune any other sense resistance located in series with the output current or the inductor current, including inductor sensing.

# Chapter 3

# Phase Current Unbalance

# Estimation

In this chapter, a method for estimating the phase current unbalance in a multiphase buck converter is presented. The method uses the information contained in the voltage drop at the input capacitor's ESR to estimate the average current in each phase. Although the absolute estimation of the currents depends on the value of the ESR and is therefore not accurate, the relative estimates of the currents with respect to one other are shown to be very accurate. The method can be implemented with a low-rate down-sampling A/D converter and is not computationally intensive. Experimental results are presented, showing good agreement between the estimates and the measured values.

### 3.1 Introduction

The multi-phase synchronous buck converter is the topology of choice for low-voltage high-current DC/DC converter applications [5, 18–23]. The advantages of this topology are numerous. In a converter with N phases the ripple frequency is  $Nf_s$ , where  $f_s$  is the switching frequency of each phase, therefore both the ripple is reduced and the requirements of the input and output filters are relaxed. Each switch and inductor conducts N times less current than in an equivalent conventional buck converter. Finally, there are more opportunities of control in one clock cycle, meaning that the delay in the control loop gets reduced and a higher bandwidth can be achieved. However, the topology requires more components and a more complex controller.

Furthermore, there is a potential problem with current unbalance. The thermal constraints as well as the dimensioning of the semiconductors and inductors of each phase depend on the maximum current they deliver. If all phases are balanced, the maximum phase current is equal to the maximum load current divided by N. However, small variations in the characteristics of each phase could generate a significant current unbalance, leading to the need to over design the components. Besides that, if the currents are not balanced properly frequency components below  $Nf_s$  are present in the input current. In conclusion, most of the advantages of the multi-phase topology are lost if the currents are not balanced.

For this reason, all commercial designs have an active phase balancing circuitry. The most common methods in high-current applications use phase current measurements obtained by inductor sensing [18–20] or  $R_{DS}$  sensing [21–23]. Both methods require a priori knowledge of a parasitic series resistance (inductor DCR in the former and MOSFET  $R_{DS}$  in the latter) for each phase and need to track its variation with temperature.

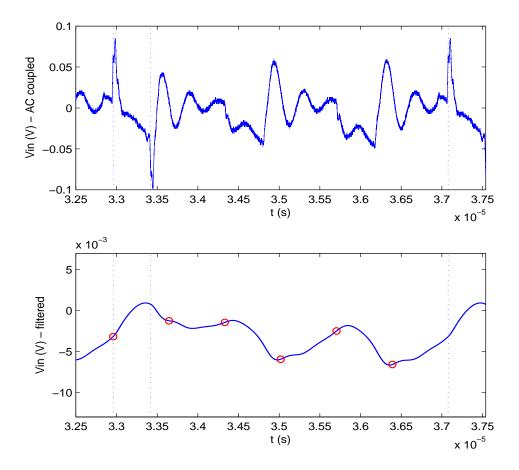

In [24] and in this work a method for estimating the current unbalance based on samples of the input voltage is described. The merit of this approach is that the same sensing element (the input capacitor ESR) is used for all phases, therefore eliminating the uncertainty when comparing measurements for different phases. In [24] the input voltage is sampled directly during the conduction time of each phase, and the samples are compared to obtain the unbalance information. However, the input voltage carries a lot of undesired high-frequency content due to the switching of large currents, reducing dramatically the signal-to-noise ratio (SNR) of the sampled values, rendering the method not practical. Furthermore, if the on-times of the different phases superpose (duty-cycle greater than 1/N), the samples are not useful.

In this chapter, a different approach for sampling the voltage input waveform is presented. Instead of relying on the instantaneous values of the waveform, a frequency analysis is performed on a filtered version of the waveform. This approach results in a much better SNR. A linear relationship between the sampled waveform and the

amplitude of the phase currents is derived. The numerical processing required is equivalent to a low-order matrix-vector multiplication or a low-order FFT, and needs to be updated at a slow rate. With the increasing popularity of digital capabilities in DC/DC controllers, this functionality is not difficult nor costly to implement.

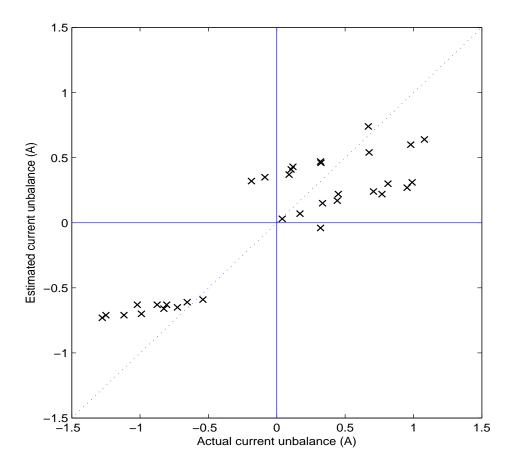

As described above, this method uses the input capacitor ESR as a unique sensing element for all phases. Therefore, the relative relationship of the phase currents' estimates with respect to each other is accurate, although the absolute value still carries the uncertainty in the value of the sensing element. The unbalance information can be used in an active current sharing method to achieve good current sharing among all phases.

This chapter is organized as follows. The current unbalance estimation method is described in Section 3.2. Some practical considerations are addressed in Section 3.3. Finally, experimental results are reported in Section 3.4.

# 3.2 Method description

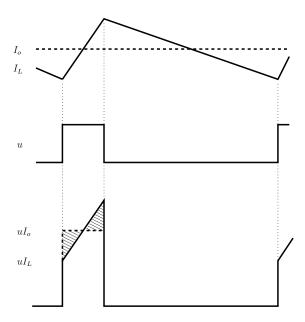

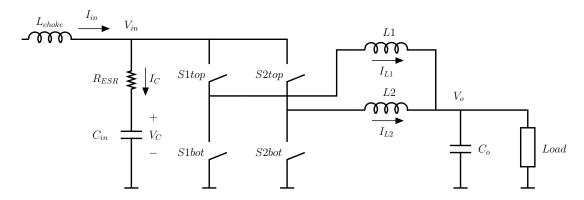

The main idea behind the method comes from the understanding of the waveform at the input voltage of a multi-phase buck converter. In Fig. 3.1 a buck converter with two phases is shown to illustrate the derivation of the method.

Usually the input current  $I_{in}$  has a very small AC component due to the presence of an inductor (choke). Therefore, the AC component of the current through the

Figure 3.1: Two-phase buck converter. The input capacitor's ESR is shown explicitly.

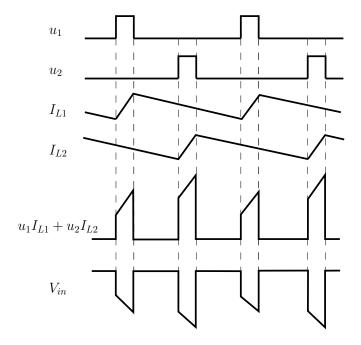

top switch (e.g., S1top) is provided by the input capacitor  $C_{in}$ , creating a voltage drop on its ESR that is proportional to the inductor current during the conduction time of the corresponding phase. This creates a perturbation on the input voltage  $V_{in}$ . Since the conduction time of the phases is multiplexed in time, the resulting waveform in  $V_{in}$  contains the information of the DC amplitude of all phase currents. This is illustrated in Fig. 3.2. In this particular example, the average current in phase 2 is larger than in phase 1. Given that the difference in the phase currents can be appreciated directly from the waveform, it could be argued that sampling the input voltage during the conduction time of each phase could provide the unbalance information. Unfortunately, the samples taken of this waveform are noisy, so this approach becomes impractical. Additionally, in some cases the conduction times of different phases could overlap (for example with a duty-cycle larger than 50% in a two-phase system). For these reasons, it is more practical to analyze the harmonic content of the waveform, as will be described next.

Figure 3.2: Voltage and current waveforms in a two-phase buck converter with unbalanced currents.

In general, for a buck converter with N phases

$$V_{in} = V_C + R_{ESR}I_C (3.1)$$

$$I_C = I_{in} - \sum_{i=1}^{N} u_i I_{Li} (3.2)$$

and then, combining (3.1) and (3.2)

$$V_{in} = V_C + R_{ESR}I_{in} - R_{ESR}\sum_{i=1}^{N} u_i I_{Li}$$

(3.3)

where

$$u_i(t) = \begin{cases} 1, & \text{if } Sitop \text{ is ON} \\ 0, & \text{if } Sitop \text{ is OFF} \end{cases}$$

for  $i = 1 \dots N$ .

As mentioned above, in steady-state operation the input current  $I_{in}$  can be considered constant. The capacitor voltage  $V_C$ , on the other hand, can be considered

constant as long as the time constant  $R_{ESR}C_{in}$  is such that the capacitor impedance behaves resistively at the switching frequency. If that is not the case, as could happen with ceramic capacitors, then an extra circuit as depicted in Fig. 3.3 can be used to eliminate the variations due to the charging/discharging of the capacitor. If the RCtime constant of the two branches is equal (i.e.,  $R_{ESR}C_{in} = R_sC_s$ ), then

$$V_s(t) = R_{ESR}I_C(t). (3.4)$$

Substituting  $I_C$  from (3.2), it is concluded that

$$V_s = R_{ESR}I_{in} - R_{ESR}\sum_{i=1}^{N} u_i I_{Li}.$$

(3.5)

Notice that this waveform is the same as the input voltage, but without the capacitor voltage. This means that not only are the variations in the capacitor charge excluded, but also that the DC component is eliminated, making the waveform voltage levels more suitable for sampling. In the following derivations, it will be assumed that the waveform to be processed is  $V_s(t)$  and not  $V_{in}(t)$ .

The relative amplitude of the phase currents will be reflected in the harmonic content of the waveform  $V_s(t)$ , in particular in frequencies  $kf_s$  for k = 1...N - 1, where  $f_s$  is the switching frequency. For perfectly balanced operation, the  $V_s$  waveform would have zero content at these frequencies. In the case illustrated in Fig. 3.2,  $V_{in}(t)$  (or equivalently,  $V_s$ ) has a harmonic component at frequency  $f_s$  due to the difference in the average current in the two phases; it is easy to see that the lowest

Figure 3.3: Capacitor current sensing.

harmonic frequency present in a two-phase balanced circuit would be  $2f_s$ . It will be shown below that frequencies above  $(N-1)f_s$  can be eliminated without losing the unbalance information, allowing for the sampling of a "clean" waveform, without all the high-frequency content usually present at the input voltage node.

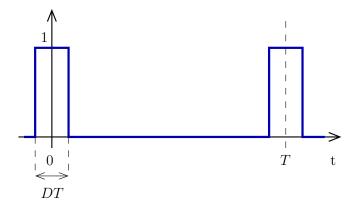

The harmonic content of  $V_s$  can be computed by using the Fourier series expansion of a pulse train, and applying the time-shift and superposition properties. A pulse train of amplitude one and duty cycle D (Fig. 3.4) has the following Fourier coefficients:

$$c_0^{PT} = D (3.6)$$

$$c_k^{PT} = c_{-k}^{PT} = D \cdot \frac{\sin k\pi D}{k\pi D}.$$

(3.7)

The time origin is located at the middle of the pulse. Notice that it is sufficient to do the computation with a rectangular pulse, and not a trapezoidal one as in Fig. 3.2,

Figure 3.4: Pulse train.

because the higher frequency components are of no interest since the method relies on lower frequency harmonics.

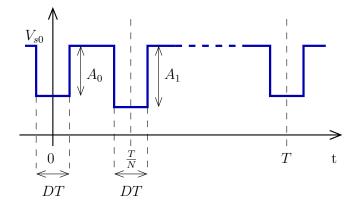

The waveform  $V_s(t)$  can be expressed as a constant term  $V_{s0} = R_{ESR}I_{in}$ , minus the sum of N pulse trains of amplitude  $A_m$  time-shifted by mT/N, m = 0...N - 1(Fig. 3.5). The results are general and valid even if the pulses overlap (i.e., D > 1/N). Then, the Fourier series expansion of  $V_{in}(t)$  is

$$V_s(t) = \sum_{k=-\infty}^{+\infty} c_k e^{jk\omega t}$$

(3.8)

where the Fourier coefficients can be obtained from (3.6) and (3.7), applying the time-shift and superposition properties

$$c_0 = V_{s0} - c_0^{PT} \cdot \sum_{m=0}^{N-1} A_m$$

$$= V_{s0} - D \cdot \sum_{m=0}^{N-1} A_m$$

(3.9)

Figure 3.5: The waveform  $V_s(t)$  as a superposition of pulse trains.

$$c_{k} = -c_{k}^{PT} \cdot \sum_{m=0}^{N-1} A_{m} e^{-j\frac{2\pi km}{N}}$$

$$= -D \cdot \frac{\sin k\pi D}{k\pi D} \cdot \sum_{m=0}^{N-1} A_{m} e^{-j\frac{2\pi km}{N}}.$$

(3.10)

The first N Fourier coefficients from (3.9) and (3.10) can be written in a more compact form as

$$\mathbf{c} = V_{s0}\mathbf{e_1} - \mathbf{P_DS_Na} \tag{3.11}$$

where

$$\mathbf{c} = \begin{bmatrix} c_0 & c_1 & \cdots & c_{N-1} \end{bmatrix}^\mathsf{T}$$

$$\mathbf{e_1} = \begin{bmatrix} 1 & 0 & \cdots & 0 \end{bmatrix}^\mathsf{T}$$

$$\mathbf{P_D} = D \cdot \operatorname{diag} \begin{bmatrix} 1 & \frac{\sin \pi D}{\pi D} & \cdots & \frac{\sin(N-1)\pi D}{(N-1)\pi D} \end{bmatrix}$$

$$\mathbf{S_{N}} \ = \ \begin{bmatrix} W_{N}^{0} & W_{N}^{0} & \cdots & W_{N}^{0} \\ W_{N}^{0} & W_{N}^{1} & \cdots & W_{N}^{N-1} \\ W_{N}^{0} & W_{N}^{2} & \cdots & W_{N}^{2(N-1)} \\ \vdots & \vdots & & \vdots \\ W_{N}^{0} & W_{N}^{N-1} & \cdots & W_{N}^{(N-1)(N-1)} \end{bmatrix}$$

$$W_{N} \ = \ e^{-j\frac{2\pi}{N}}$$

$$\mathbf{a} \ = \ \begin{bmatrix} A_{0} & A_{1} & \cdots & A_{N-1} \end{bmatrix}^{\mathsf{T}}.$$

Notice that  $\mathbf{S_N}$  is the Discrete Fourier Transform matrix which is invertible, with inverse  $\frac{1}{N}\mathbf{S_N}^*$  [25].

Now the problem of computing the Fourier coefficients from a sampled version of the waveform  $V_s(t)$  is addressed. Let  $x_k = V_s(kT_{\text{samp}})$ , where  $T_{\text{samp}} = 1/(2Nf_s)$ , i.e., the waveform is sampled at 2N times the switching frequency. The waveform should be filtered with a low-pass anti-aliasing filter with a cut-off frequency equal to  $Nf_s$  for full recovery of the low frequency harmonics.

Then, the relationship between the Fourier coefficients of the continuous-time signal and the sampled values is given by the Discrete Fourier Transform [25]

$$\mathbf{c'} = \frac{1}{2N} \mathbf{S_{2N}} (1:N, 1:2N) \mathbf{x}$$

$$= \tilde{\mathbf{S}_{2N}} \mathbf{x}$$

(3.12)

where  $\mathbf{x} = \begin{bmatrix} x_0 & x_1 & \cdots & x_{2N-1} \end{bmatrix}^\mathsf{T}$ , and the 2N-point DFT matrix is truncated to

ignore the negative-frequency components, generating  $\tilde{\mathbf{S}}_{2N}$ . The prime notation is used to emphasize that these are the Fourier coefficients of the voltage waveform that is actually sampled. This waveform is different from the input voltage waveform used to derive (3.11) in two aspects: first, there is a distortion introduced by the anti-aliasing filter, and second, there is a phase shift introduced if the sampling is not performed synchronized with the time origin used to derive (3.11). These two effects are deterministic and easy to characterize as follows.

The presence of a low-pass filter before the sampling process may introduce an amplitude and phase distortion in the waveform, that can be taken into account by introducing a correction matrix **C** that includes the transfer function of the filter evaluated at the frequencies of interest

$$\mathbf{C} = \operatorname{diag} \left[ H(0) \ H(2\pi f_s) \ \cdots \ H((N-1)2\pi f_s) \right]$$

(3.13)

where  $H(\omega)$  is the frequency response of the low-pass filter.

In order to be consistent with the derivation of the Fourier coefficients in (3.7), the origin t = 0 has to be positioned at the middle of the conduction time of the phase associated with amplitude  $A_0$ . It is usually more convenient for the sampling synchronization to position the origin at the beginning of the conduction period. This would, according to the time-shift property, introduce a phase-shift of  $k\pi D$  for each Fourier coefficient  $c_k$ , that can be summarized in a correction matrix **R** defined as

$$\mathbf{R} = \operatorname{diag} \left[ \begin{array}{cccc} 1 & e^{-j\pi D} & \dots & e^{-j(N-1)\pi D} \end{array} \right]. \tag{3.14}$$

Then, combining both effects, the relationship between the Fourier coefficients of the sampled waveform and the ideal one is

$$\mathbf{c}' = \mathbf{RCc}.\tag{3.15}$$

Combining (3.11), (3.12), and (3.15)

$$\tilde{\mathbf{S}}_{2N}\mathbf{x} = \mathbf{RC} \left( V_{s0}\mathbf{e}_1 - \mathbf{P}_{D}\mathbf{S}_{N}\mathbf{a} \right) \tag{3.16}$$

yielding the vector of phase current amplitudes

$$\mathbf{a} = \mathbf{S_N}^{-1} \mathbf{P_D}^{-1} \left( V_{s0} \mathbf{e_1} - \mathbf{C}^{-1} \mathbf{R}^{-1} \tilde{\mathbf{S}}_{2N} \mathbf{x} \right). \tag{3.17}$$

Since the objective is to estimate the current unbalance, the difference of each amplitude with respect to the average is derived as

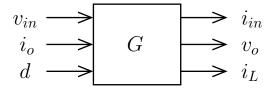

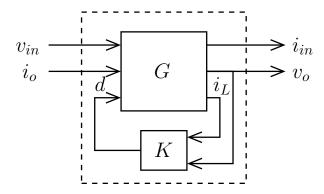

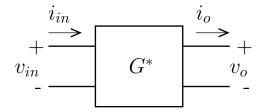

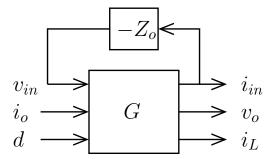

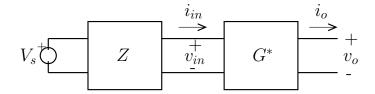

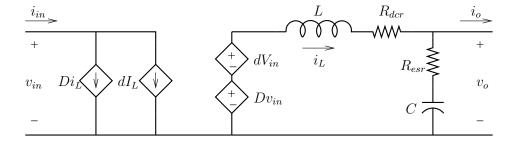

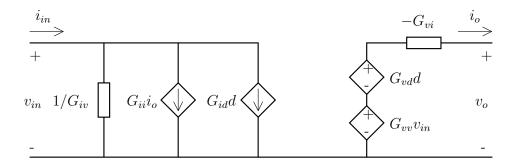

$$\mathbf{a_{diff}} = \mathbf{a} - \frac{1}{N} \mathbf{1} \mathbf{1}^{\mathsf{T}} \mathbf{a} \tag{3.18}$$