# Low Power CMOS RF Amplifiers for Short Range Wireless Links:

## A Design Tool and its Application.

#### By

#### Leonardo Barboni

Tesis Presentada Ante el Instituto de Ingeniería Eléctrica Para Cumplir con Parte de los Requisitos del Grado de MAGISTER EN INGENIERIA ELECTRICA

Tutor:

Dr. Fernando Silveira

Tribunal:

Dr. Alfredo Arnaud, UCU, Uruguay Ing Juan Mártoni, UDELAR, Uruguay Dr. Wilhelmus Van Noije, USP, Brazil

> Instituto de Ingeniería Eléctrica Facultad de Ingeniería Universidad de la República Montevideo, Uruguay December 2005

ISSN: xxxx-xxxxx

Created with PDFCREATOR - GNU GENERAL PUBLIC LICENSE Version 2, June 1991

Copyright (C) 1989, 1991 Free Software Foundation, Inc.

59 Temple Place - Suite 330, Boston, MA 02111-1307, USA

### Abstract

This thesis is mainly focused on the implementation of low-power integrated power amplifier. The main keywords are; tool for CMOS design, wireless short range devices and low current consumption.

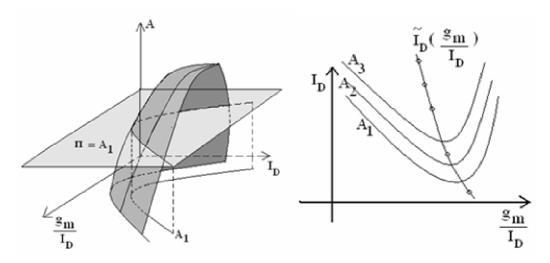

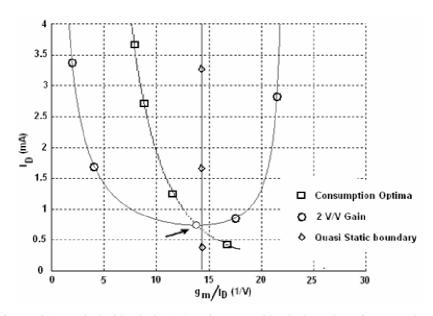

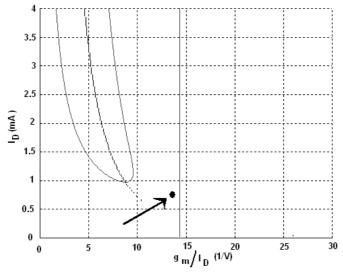

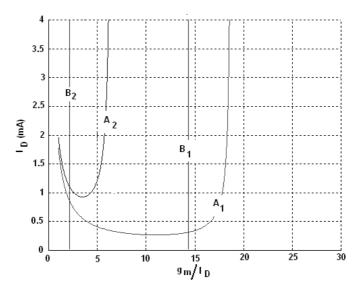

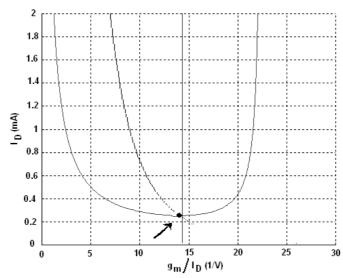

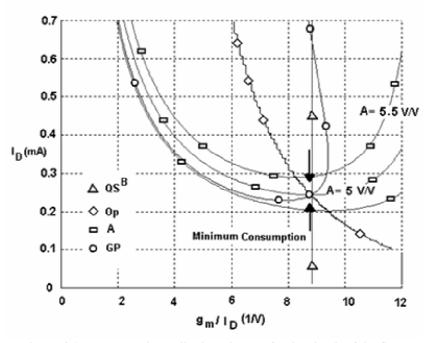

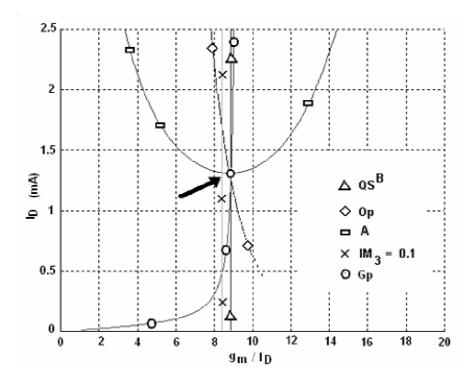

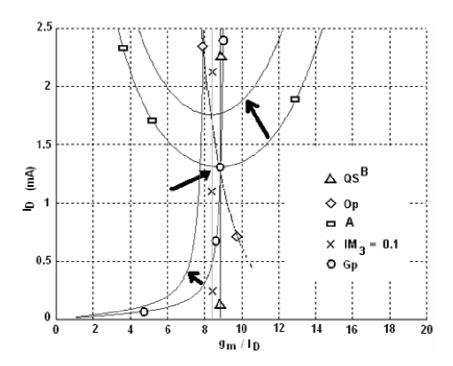

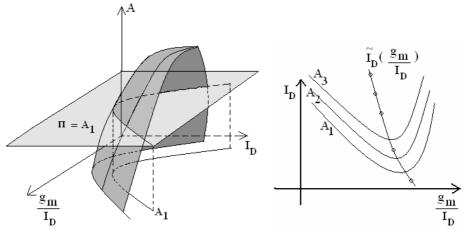

A tool that explores the design space of basic RF circuit blocks is presented. The tool takes advantage of the application of a MOS transistor model continuous (ACM model) in all inversion levels (weak to strong inversion). The performance of the circuit is analyzed in the  $I_D$ - $g_m/I_D$  plane and our tool shows the existence of an inversion level that provides an optimum in the power consumption for a given voltage gain and frequency.

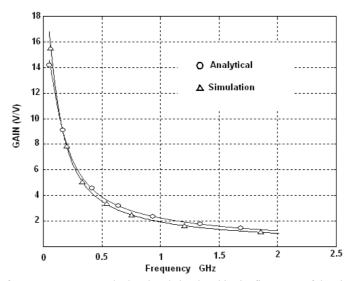

Examples are presented showing comparison of the performance of different technologies and circuits' architectures as well as we will show that the evaluation of the effect of parasitic elements can be easily done. The tools estimations are checked against simulations using the foundry provided BSIM3v3 model showing very good agreement.

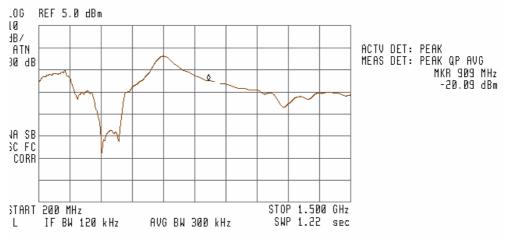

Finally, the tool is tested in the design of two power amplifiers at 910 MHz in  $0.35\mu m$  CMOS technology where one of them was designed for wireless short distance devices. Additionally, characterization and experimental results for these amplifiers are presented.

## Resumen

Esta tesis esta orientada hacia la implementación de amplificadores de potencia de bajo consumo. Las palabras claves son: herramienta para diseño de circuitos CMOS, dispositivos para enlaces inalámbricos de corto alcance y bajo consumo de corriente.

Se presentará la herramienta que explora el espacio de diseño de circuitos de RF aplicando un modelo continuo de transistor MOS (modelo ACM) válido en todas las regiones de inversión (inversión débil a fuerte). El desempeño del circuito es analizado en el plano  $I_D$ - $g_m/I_D$  y este método junto con la herramienta muestra la existencia de un nivel de inversión óptimo que garantiza un óptimo de consumo de potencia para una ganancia de voltaje y a una frecuencia de operación dada.

Son presentados ejemplos que comparan el desempeño de diferentes tecnologías y arquitecturas de circuitos así como también se mostrará que la evaluación de los efectos parásitos es fácilmente realizable.

El desempeño de la herramienta fue probado con simulaciones usando el modelo de transistor MOS BSIM3v3 suministrado por el fabricante, con el cual se ha verificado una buena correlación

Finalmente, la herramienta es probada en el diseño de dos amplificadores de potencia funcionando a 910MHz en tecnología CMOS 0.35µm, el cual uno de ellos es diseñado para formar parte de dispositivos para enlaces inalámbricos de corta distancia.

Adicionalmente, la caracterización y resultados experimentales obtenidos de estos amplificadores son presentados.

# Table of Contents

| Abstract                                                      | 3      |

|---------------------------------------------------------------|--------|

| Table of Contents                                             |        |

| Acknowledgements                                              |        |

| CHAPTER 1                                                     | 8      |

| Introduction                                                  | •••••• |

| Introduction                                                  |        |

| 1.1 Motivation and Research Goals.                            | 8      |

| 1.2 Thesis Organization.                                      |        |

| 1.3 References.                                               |        |

|                                                               |        |

| CHAPTER 2                                                     | 11     |

| The Wireless Link & Power Transmission Issues                 |        |

| 2.1- Radio Design Considerations.                             | 11     |

| 2.1.1 Frequency Bands and Data Rates.                         |        |

| 2.1.2 Channel Model and Range.                                |        |

| 2.1.3 Radio System Parameters (Sensitivity and Dynamic Range) |        |

| 2.2- Key Topic of CMOS RF Power Amplifier                     |        |

| 2.2.1 Linearity.                                              |        |

| 2.2.2 Efficiency.                                             |        |

| 2.2.3 Filtering and Matching                                  | 22     |

| 2.3- References.                                              | 25     |

| CHAPTER 3 MOS Transistor Model for RF IC Design               | 27     |

| 3.1 Background                                                | 27     |

| 3.1.1 The ACM Model.                                          |        |

| 3.1.2 The $g_m/I_D$ ratio.                                    |        |

| 3.1.3 Non Quasi-Static Boundary.                              |        |

| 3.2 Tool Modelling Approach                                   |        |

| 3.3 Two Port Network Models                                   |        |

| 3.3.1 Transformations to study others architectures           |        |

| 3.4 References.                                               | 41     |

| CHAPTER 4                                                     | 43     |

| Tool for RF CMOS Design                                       |        |

|                                                               |        |

| 4.1 Design Exploration Process                                |        |

| 4.2 Matlab Exploration Tool                                   |        |

| 4.2.1 Formalism                                               |        |

| 4.2.2 Example 1                                               |        |

| 4.2.3 Example 2                                               |        |

| 4.2.4 Example 3                                               |        |

| 4.3 Tool User Interface                                       |        |

| 4.4 Design Examples                                           | 55     |

| 1.1.1 Opinium / impinior ouise                                |        |

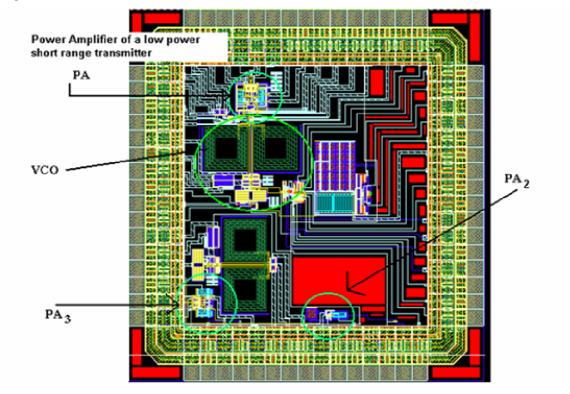

| 4.          | 4.2 Power Amplifier of a low power short range transmitter. |

|-------------|-------------------------------------------------------------|

| 4.5 Re      | 4.4.2.1- Calculus.                                          |

|             |                                                             |

|             | PTER 5                                                      |

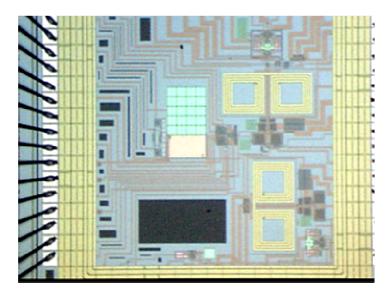

| Layo        | ut and Experimental Results                                 |

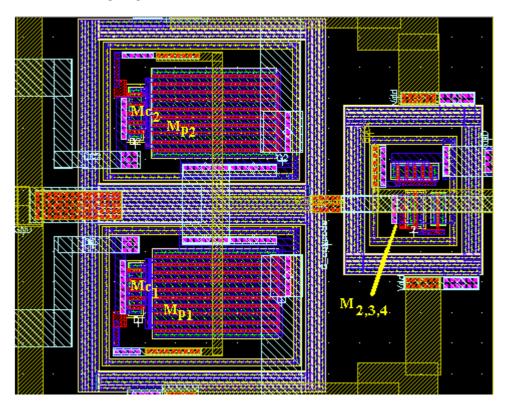

| 5.1 La      | yout                                                        |

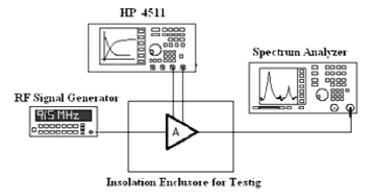

|             | st Setup                                                    |

|             | otimum Amplifier Stage                                      |

| 5.          | 3.1 Measurement and Simulation Conditions                   |

| 5.4 Po      | ower amplifier of a low power short range transmitter       |

|             | 4.1 Measurement and Simulation Conditions.                  |

| 3.0 K       | eferences                                                   |

| <b>CH</b> A | PTER 6                                                      |

| Conc        | clusion                                                     |

| 61 Co       | onclusions                                                  |

|             | 1 Performance                                               |

| 6.1 Fu      | ture Work                                                   |

| 1nn         | endix A                                                     |

|             |                                                             |

| Intro       | duction to Volterra Series & Effects of Nonlinearity        |

|             |                                                             |

|             | olterra Series Representation.                              |

|             | tput from Volterra Kernels.                                 |

|             | plicability of Volterra Series.                             |

| A 4 G       | in Compression.                                             |

|             | ferences                                                    |

| 1nn         | endix B                                                     |

| 4.4         | er Series Expansion of The Drain Current                    |

|             |                                                             |

| B.1 No      | nlinearity coefficients                                     |

| Appe        | ndix C                                                      |

|             | ytic Solution of the Optima                                 |

| C 1 Fo      | rmalism                                                     |

|             | gorithm                                                     |

|             | rdana's solution.                                           |

|             | riations due to the load impedance.                         |

| Anna        | endix D                                                     |

|             |                                                             |

| Done        | l wires and Bond Pads                                       |

|             | nd Pads                                                     |

| D.2 Bo      | nd Wires.                                                   |

| D.3 Guard Ring.                                                                | 97        |

|--------------------------------------------------------------------------------|-----------|

| Appendix E Non Quasi-static Frequency Boundary                                 | 99        |

| E.1 Relationships Between $f_{NQS}$ and $f_T$ E.2 Effect of the slope factor n | 99<br>100 |

# Acknowledgements

First and foremost, I would like to thank God for all his numerous blessings bestowed upon me.

This journey will never be fulfilled without the support of many people.

First I am especially grateful for investing considerable time, effort, invaluable suggestions and ideas to my research projects and resources in my postgraduate education, my advisor, Fernando Silveira.

Next I would like to thank all my colleagues. All IIE members have had enormous influence on the quality of my postgraduate education, specifically, the Microelectronic Team (Fernando Silveira, Conrado Rossi, Pablo Mazzara, Pablo Aguirre, Rafaela Fiorelli and Linder Reyes). Individually and collectively, they represent one of the great treasures of the IIE.

Among this group, a few individuals need specific recognition: Rafaela Fiorelli for technical conversations that lent perspective to this work and I would also like to thank Conrado Rossi and Pablo Aguirre for their assiduous assistance in solving CAD problems.

Going to the affective fields, I would like to thank my girlfriend Lidia Esteves for loving me enough to sacrifice, support, and encourage the pursuit this work.

Finally, I am grateful to my friends, and to the CAP and SCAPA committees without their continuous support, this Msc. work will have been much more difficult.

# Chapter 1

### Introduction

**Chapter Overview -** In this chapter, an introduction with motivations and objectives of this thesis are presented. In addition with this, design goals for the project are discussed to provide a context for this research.

#### 1.1- Motivations and Research Goals

Nowadays, the development of low-cost, low-power radiofrequency (RF) devices grows up rapidly, and those systems are characterized by short range links (usually below 100m) and reduced power consumption (since the devices are powered with batteries). However, these applications have a few systems challenges to resolve from current consumption point of view.

In this way, the Microelectronic Team has started a development task toward the issue Wireless Sensor Network and having strong experience to develop low power devices, this thesis has focus on reuse these ideas and past experience to explore their possible applicability in the RF field.

It is known that optimum power consumption of analog circuits can be reached in the moderate inversion region [1], where is obtained a good trade-off between a high  $g_m/I_D$  and a non-excessive transistor size (translated to medium parasitic capacitances values). Traditionally the operation at this optimum was restricted to low frequency applications, since the transconductance values required for operation at RF implied currents that, in order to operate in moderate inversion, lead to enormous transistor sizes.

These big transistors would imply high parasitic capacitances that would jeopardize the advantage of an increased  $g_m/I_D$  ratio in moderate inversion. However, what is "low" frequency and "high" frequency is technology dependent. Particularly, in current deep sub micron technologies, the reduction of parasitic capacitances and the increase of the current drive by the increase of the gate oxide capacitance per unit area, make that RF frequencies are, in fact, "low" frequency. This idea, that this work exploits, has been also advanced in works such as [2,3,4].

The design of RF devices involves a tradeoff of several performance parameters such as linearity, distortion, gain power, gain voltage and current consumption. In this work we present a design tool oriented toward CMOS RF devices. It is a tool which can be used either to design amplifiers, obtaining an optimum design and showing the trade off between amplifier's gain and power consumption, or to evaluate the performance of a particular technology at a desired frequency.

The core of the tool estimator of RF analog CMOS circuits' behaviour is based in the MOS transistor model ACM [4] and the tool engine is based on MATLAB

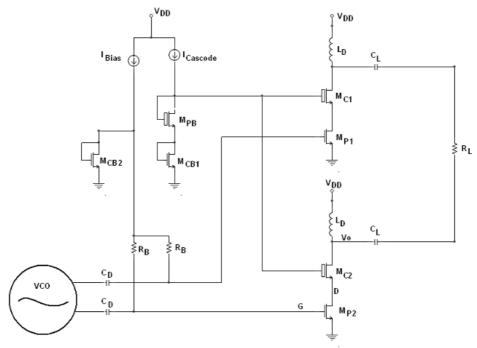

With this tool it has been checked the good performance of a  $0.35\mu m$  technology at 910MHz and it has been designed two power amplifier prototypes, showing optimum behaviour from current consumption point of view One of these amplifiers was made in order to boost up power from a VCO used as core device which conform a node of a wireless sensor network.

Finally, it is important to underline that some results presented in this work have been also reported in the following arbitrates conferences:

- L.Barboni , R.Fiorelli, F.Silveira *"A Tool for Design Exploration and Power Optimization of CMOS RF Circuits Blocks"* Paper presented to ISCAS 2006 –Island of Kos -Greece

- L.Barboni , R.Fiorelli, F.Silveira "Design and power optimization of CMOS RF Blocks operating in the moderate inversion region" 18th SBCCI. September 2005 Florianopolis, Brazil.

- L.Barboni ,R.Fiorelli, F.Silveira "Diseño de Bloques de RF de Bajo Consumo en Inversión Débil y Moderada" XI IBERCHIP Workshop Marzo 2005

#### 1.2-THESIS ORGANIZATION

This thesis consists of six chapters as follows:

#### Chapter 1 – Introduction

**Chapter Overview -** In this chapter, an introduction with motivations and objectives of this thesis are presented. In addition with this, design goals for the project are discussed to provide a context for this research

#### Chapter 2 – The Wireless Link & Power Transmission Issues

**Chapter Overview** - In order to understand the wireless link behaviour and what will influence link performance; this chapter covers some fundamentals issues related to the wireless system design.

A challenge for wireless sensor network is energy. Designing systems with long lifetimes will be necessary due to the energy resources available will be limited and replacing batteries is not a practical option. Therefore, to reduce energy consumption, we should investigate some fundamentals of the transmission path and the trade off between environmental factor, output power and maximum useful range.

Finally, this chapter ends by including a review of RF power amplifier class A,B and C because when we consider battery-operated devices, the power efficiency of the amplifier is definitely a main concern.

#### Chapter 3 - MOS Transistor Model for RF IC Design

**Chapter Overview** — Modeling of devices is a key step into design processes because without good models, it becomes difficult to analyze and predict circuit behaviour. The purpose of this chapter is to study a compact high-frequency MOSFET model and how it could be implemented in our tool. The model used for the MOS transistor is the ACM model which was presented by Galup-Montoro et al. [4] and as we will see throughout this chapter, this model has desirable characteristics from the designer point of view.

#### Chapter 4 - Tool for CMOS RF Design

**Chapter Overview** – This chapter begins with an overview of the tool developed as main goal of this work, which can be used to design amplifiers obtaining an optimum from current consumption point of view and showing the trade off between amplifier's gain and power consumption as well as to evaluate the performance of a particular technology at a desired frequency.

At the end, two different circuits are presented as design examples implemented in order to validate the results of against simulations and measurements

#### Chapter 5 - Layout and Experimental Results

**Chapter Overview** - This chapter describes the layout of the circuits and presents the results obtained from measuring prototypes. Performance of each power amplifiers is characterized as well as simulations of the synthesized circuits are presented.

#### Chapter 6 - Conclusions

Chapter Overview - Conclusions and ideas for future research are presented.

Furthermore, we present five appendices as follow:

Appendix A - Introduction to Volterra Series & Effects of Nonlinearity

Appendix B - Power Series Expansion of the Drain Current

Appendix C - Analytic Solution of the Optima

Appendix D - Bond Wires, Bond Pads & Guard Rings

Appendix E- Non Quasi-static Frequency Boundary

#### 1.3- REFERENCES

- [1] F.Silveira, D. Flandre, P.G.A. Jespers, "A gm/ID Based Methodology for the Design of CMOS Analog Circuits and its Application to the Synthesis of a Silicon-on-Insulator Micropower OTA", *IEEE Journal of Solid State Circuits*, Vol. 31, No. 9, Sept. 1996, pp. 1314 1319

- [2] A.S.Porret, T Melly, D.Python, C.C.Enz, E.A.Vittoz. "An Ultralow Power UHF Transceiver Integrated in a Standard Digital CMOS Process: Architecture and Receiver". *IEEE Journal of Solid-Sate Circuit VOL 36*, NO 3, March 2001, pp. 452-466.

- [3] V. Varotto, O. Gouveira-Filho, "Design of RF CMOS Low Noise Amplifiers Using a Current Based MOSFET Model", Proceedings of 17th Symposium on Integrated Circuits and Systems Design. Porto de Galinhas, v. 1, p. 82-87, September 2004.

- [4] A.A.Cunha, M.C.Schneider, C.Galup-Montoro "An MOS Transistor Model for Analog Circuit Design". IEEE Journal of Solid-Sate Circuit VOL 33,NO 10,October 1998, pp.1510-1519...

# The Wireless Link & Power Transmission Issues

**Chapter Overview** – In order to understand the wireless link behaviour and what will influence link performance, this chapter covers some fundamentals issues related to the wireless system design.

A challenge for wireless sensor network is energy. Designing systems with long lifetime will be necessary due to the energy resources available will be limited and replacing batteries is not a practical option. Therefore, to reduce energy consumption, we should investigate some fundamentals of the transmission path and the trade off between environmental factor, output power and maximum useful range.

Finally, this chapter ends by including a review of RF power amplifier class A,B and C because when we consider battery-operated devices, the power efficiency of the amplifier is definitely a main concern.

#### 2.1- RADIO DESIGN CONSIDERATIONS

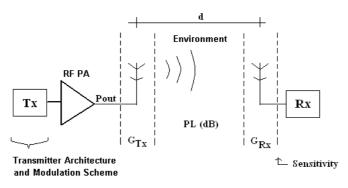

A model of a wireless link is shown in Figure 2.1. It includes a transmitter with antenna (whose antenna's gain is  $G_{Tx}$ ), a transmission path with multipath phenomenon caused by reflection, diffraction and scattering, (path loss PL(dB)) and finally, the receiver with antenna (whose antenna's gain is  $G_{Rx}$ ).

The antenna transforms the power delivered from the power amplifier into electromagnetic energy which radiates to the receiver. Therefore, to reduce energy consumption, we should investigate some fundamentals of the transmission path and the tradeoff between environmental factor, output power and maximum useful range of communication.

Figure 2.1: Description of a basic radio link model

In the traditional wireless link, the transmission distance is large (>100 m), so that the transmission energy is dominant in the total consumption energy. However, in many recently proposed wireless sensor network [1][2] the average distance between nodes is usually below 10m and it is characterized by low-power transmission (less than 10dBm)

In this situation many scenarios have been proposed for distributed wireless sensor network such as tracking, medical devices (patient monitoring), location sensing, machine-mounted sensing, climate control and much more. As a result, the growing demand in wireless sensor devices has created the necessity to research into energy-efficient protocols and architectures, which have been emerging and improving since years ago.

As an example, the IEEE Std. 802.15.4 [4][5] has a focus in wireless sensors and actuators for the industry in general in order to provide extremely low-power, low-rate and low-cost wireless connectivity. These features enable applications in the fields of industrial, agricultural, vehicular, residential and medical sensors.

In the next Table 2.1, we show a brief overview of the characteristics of the standard 802.15.4 compared with the standards Bluetooth and 802.11b.

|                     | 802.11b     | Bluetooth <sup>TM</sup>        | <b>Low Rate - 802.15.4</b>                                                                                                 |

|---------------------|-------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Useful Range        | ~100 m      | ~10 - 100 m                    | < 10 m                                                                                                                     |

| Data Rate           | ~2 - 11Mb/s | 1Mb/s                          | < 0.25Mb/s                                                                                                                 |

| Power Consumption   | Medium      | Low                            | Ultra Low: The majority of IEEE Std. 802.15.4 devices are expected to operate with transmits power between -3dBm and 10dBm |

| Neighbours Distance | Larger      | Smaller (<100m) <sup>(1)</sup> | Smallest $(<20 \text{ m})^{(1)}$                                                                                           |

Table 2.1: The 802.15.4 allocation compared with others standards from wireless parameters point of view

In the next section we present an overview of the features that characterize the standard 802.15.4.

#### 2.1.1-Frequency Bands and Data Rates

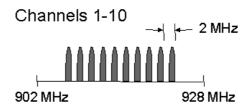

The IEEE Std. 802.15.4 PHY (Physical Layer) are specified for operation in 27 channels. Channel 0 through 10 span frequencies from 868 MHz through 928MHz and upper band reside in frequencies from 2405MHz to 2480 MHz. More specifically:

- -channel 0: 868-868.6 MHz

- -channel 1-10: 902-928 MHz (central frequency Fc = 906 + 2 (k-1) in MHz, for k = 1, 2, ..., 10)

- -channel 11-26: 2.4 -2.4835GHz

Figure 2.2: 915 MHz PHY Operating Frequency Bands

Due to the physical characteristics of each band and the regulations where they are used, the IEEE Std. 802.15.4 specifies different data rates and modulation. [4]

A detailed explanation of these parameters is shown in the next table.

<sup>(1)</sup> This range is strongly dependent on the environment (proximity of concrete wall, outdoor or indoor, etc.)

|                    |                            | Spreading                             | Parameters | Data                                    |      |                      |  |

|--------------------|----------------------------|---------------------------------------|------------|-----------------------------------------|------|----------------------|--|

| Frequency<br>(MHz) | Frequency<br>Band<br>(MHz) | Chip rate <sup>(1)</sup><br>(kchip/s) | Modulation | Bit Rate (kb/s) Symbol rate (ksymbol/s) |      | Symbols              |  |

| 868/915            | 868-868.6                  | 300                                   | BPSK       | 20                                      | 20   | Binary               |  |

| 000/913            | 902-928                    | 600                                   | BPSK       | 40                                      | 40   | Binary               |  |

| 2450               | 2400-2483.5                | 2000                                  | O-QPSK     | 250                                     | 62.5 | 16-ary<br>Orthogonal |  |

Table 2.2: Frequency bands and data rates

Others 868MHz/ 915 MHz Band Specifications

- Spreading code is conformed by a 15-chip M-sequence. Chip modulation is based on BPSK at 0.6/0.3 Mchips/s (M-sequence is a technique like codes of Walsh for creating orthogonal sequences. It is often used due to it can be created using a shift register with M feedback –taps)

- Transmit Power: Capable of at least -3dBm. Typical 0 dBm

- Transmit Center Frequency Tolerance: ± 40 ppm

- Receiver Sensitivity: -92 dBm or better (1% Packet Error Rate)

As we can see, only a boundary of levels of delivered power from the antenna to the environment has been specified. Thus, each system designer has to have some fundamentals knowledge of the radio related parameters which influence overall system performance and how much output power should be specified for each application and range.

#### 2.1.2-Channel Model and Range

The ratio of the power at a receiving antenna to the power at a transmitting antenna is given, in free space, by the Friis radio link model [5][6]:

$$\frac{P_R}{P_T} = G_T G_R \left(\frac{c}{4\pi f d}\right)^2 \tag{2.1}$$

Where:

$P_R$ : power at the receiving antenna

**P**<sub>T</sub>: power at the transmitting antenna

$G_{R}$ ,  $G_{T}$  are the power gains of receiving and transmitting antennas respectively

**c**: is the speed of light

d: distance between antennas

f: frequency

This same equation can be expressed as a basic path loss PL(dB) in decibel form:

$$P_R - P_T = G_T + G_R - PL(dB)$$

(2.2)

Where:

$$PL(dB) = 32.44 + 20\log(d_{Km}) + 20\log(f_{MHz})$$

(2.3)

<sup>(1)</sup> In direct sequence spread spectrum technologies such as CDMA and DSSS, it is the number of bits per second (chip per second) used in the spreading signal. The chip rate is usually several times the information bit rate.

Where the subindex indicates units. This notation will be applied in the rest of the chapter.

The antenna is included as the parameter antenna gain. This could be interpreted as the antenna's ability to transform output power into radiated energy. According with the bibliography [1], the antenna gain is generally proportional to physical size. The fundamental relation in antenna theory is:

$$G = \frac{4.\pi \cdot A_f}{\lambda^2} \tag{2.4}$$

Where:

$A_f$  is the effective area  $\lambda$ : is the wavelength

For low power radio devices, the loop antenna etched on the PCB has a typical effective gain of approximated 20dB to -25dB [1]

To put things into perspective the effective area to achieve an antenna gain of 0dB is  $A_f = 0.0086 \text{ m}^2$  (approximated 0.093m X 0.093m) for the 915MHz band ( $\lambda = 0.328\text{m}$ ).

Most useful applications would be unpractical with such a large antenna and they are usually implemented with a much smaller antenna which has a gain below 0dB. Thus, it is important to underscore that the antenna actually introduces loss in the transmission budget and it depends on its size.

Although the designer must take care of the antenna selected because of its loss, it is mandatory to study first the useful range characterized by the path loss PL(dB) in order to take care how much energy should be employed to make a good transmission link.

IEEE Std. 802.15.4 specifies that lower frequency bands must be capable of correctly decoding a signal with an input power of -92 dBm (better sensitivity is not prohibited). As an example, for a transmitter rated at -3 dBm, the maximum free space range in approximately:

$$-92dBm - (-3dBm) = -89dB = -32.44 - 20\log(d_{Km}) - 20\log(915) \Rightarrow d = 735m$$

(2.5)

The value given by Friis radio link formula must be interpreted as the maximum possible received power where this range is for free space, isotropic antennas and perfect power match without interference. There are a number of factors that reduce this received power. These include impedance mismatch at either antenna, propagation effects leading to attenuation and in addition, multipath effect may cause partial cancellation of the received field, as well as the antenna gain would be a factor of attenuation.

A non ideal radio path cause signal attenuation at the receiver if the transmitted signal travels multiple path to the receive antenna. Different paths have different lengths and it may produce receiver signal out of phase, resulting signal attenuation. Moreover, fading appears due to moving object in the proximity of the radio device (people and machinery as example). For example, the wavelength at 915MHz is 0.328m, for this reason actually some short distance-movement in the environment could make fluctuations in the attenuation of the signal at the receiver in the time domain while the environment is moving around. It is better known as fast fading effect.

Multipath phenomenon is caused by reflection, diffraction and scattering that is characterized by a random behaviour. It is important to remark that another factor to take into account is the loss caused by environmental obstacles such as floor, walls, building and windows. The amount of loss depends heavily on the physical characteristic of the object. For ranges between 433MHz to 868MHz, according with the bibliography [1], the most typical losses are summarized in the next table:

| Object causing path loss | Typical loss (dB) |

|--------------------------|-------------------|

| Wall (indoor)            | 10-15             |

| Wall (outdoor)           | 2-38              |

| Floor                    | 12-27             |

| Windows                  | 2-30              |

Table 2.3—Typical losses caused by transmission obstacles

Because of multiple factors cause attenuation, a better model than Friis general radio channel model must be introduced [7][8]. For a wide variety of channels, experimental measurements of the received power suggest a functional dependence for path loss given by:

$$P_{\text{Re ceived}}(dBm) = P_{\text{Transmit}}(dBm) - PL(dB) - P_{\text{Shadowing}}(dB)$$

(2.6)

Where the path loss component is given by:

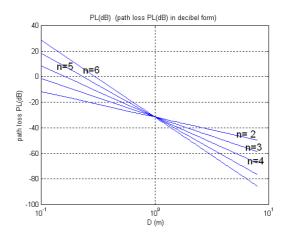

$$PL(d) = 10 \log \left( \left( \frac{4\pi f}{c} \right)^2 d^n \right)$$

(2.7)

**n:** range from 1.2 to 6 and it depends on the propagation environment, i.e., rural, urban and the type of construction material, type of interior and location within building. For example:

n=2: implies free space propagation (Friis model)

n=1.2: contrary to our intuition may suggest, values of n below than free space propagation (n=2) could be possible due to waveguide effects. It is a kind of waveguide created by concrete walls and flats in a build environment.

$P_{Shadowing}$ : is a zero mean log-normally distributed random variable with a standard deviation that depends on the environment between transmitter and receiver. This parameter must be estimated by taking measurements at the desired frequency and it is an empirical way to take into account all phenomena that can not be modeled by the equation (2.7)

In the figure 2.3 we compare the effects of the parameter n in the expression (2.7)

Figure 2.3: Path loss behaviour in decibel form at 915 MHz as function of the parameter n

Another expression of the family (2.6) and (2.7) to express the link loss suitable for Link Budget Analysis could be written as:

$$PL(d) = PL(do) + 10 n \log\left(\frac{d}{do}\right) + X_{\sigma}$$

(2.8)

Where:

PL (d): is the path loss in dB at distance d

PL (do): is the know path loss at the reference distance do (it is measured at the frequency of interest)

**n**: is an exponent depending on the propagation environment. This parameter is very sensitive and range from 1.2 to 6 could be expected as we discussed previously.

$X_{\sigma}$ : is the variable representing uncertainty of the model or variance obtained due to the effect of shadowing, diffraction and scattering. A model that has often been used to explain variations of the signal amplitude in a multipath fading environments is the Lognormal Distribution.

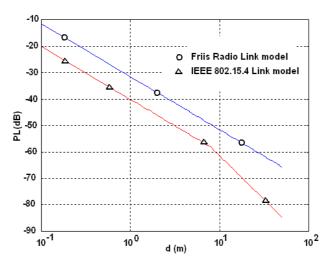

Coming back to the IEEE Std. 802.15.4, the channel path loss is assumed as a class of the family model explained in (2.8), where the standard assume that 868/915MHz bands exhibit similar behaviour to 2.4GHz band. So that, according to the IEEE Std. 802.15.4, the losses can be expressed as follows:

$$PL(dB) = 40.2 + 20\log(d_m)$$

for  $d_m < 8m$  (2.9)

$$PL(dB) = 58.5 + 33 \log \left(\frac{d_m}{8m}\right)$$

for  $d_m > 8m$  (2.10)

In the figure 2.4 we compare the difference between the free space path loss model (from equation 2.3) and the IEEE Std. 802.15.4 channel path loss model (represented by equations 2.9 and 2.10).

Figure 2.4: Path loss in decibels at 915 MHz

In the Table 2.4 we compare the PL(dB) estimated using different models @ 915MHz

| D (m) | Free Space Path Loss | PL (dB) expression (2.7) |      |       | IEEE Std. 802.15. 4 Channel |  |  |

|-------|----------------------|--------------------------|------|-------|-----------------------------|--|--|

|       | (dB)                 | n=3                      | n=4  | n=5   | Path Loss (dB)              |  |  |

| 1     | 31.7                 | 31.7                     | 31.7 | 31.7  | 40.2                        |  |  |

| 10    | 51.7                 | 61.7                     | 71.7 | 81.7  | 61.7                        |  |  |

| 50    | 65.6                 | 82.6                     | 99.6 | 116.6 | 84.8                        |  |  |

Table 2.4—PL(dB) estimated with different models.( @ 915MHz )

These models are simple and suitable for computer implementations because the environmental database is unnecessary, but, due to the model simplicity, great accuracy could not be expected. We can see the enormous dependency of the path loss with the environment. For this reason, it is important that we study some parameters that the systems must be capable to satisfy in order to maintain a good link budget in a worst case.

#### 2.1.3-Radio System Parameters (Sensitivity and Dynamic Range)

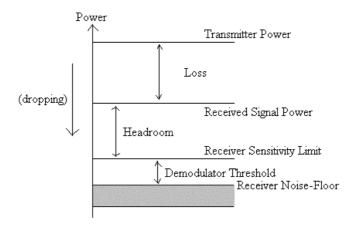

We can see the power levels of the systems in the figure 2.5 (figure 4 in [1]), where the noise floor is the total average noise available at the input of the system.

Sensitivity is the minimum received power that results in a satisfactory BER (bit error rate, usually  $1x10^{-3}$ ) that imply a satisfactory SNR  $_{min}$  in the receiver. The difference between received signal power and sensitivity is a margin also known as headroom. The headroom varies with time due to a number of factors such as path loss and antenna efficiency, as we discussed previously.

Figure 2.5: Transmission link budget

Another important parameter is the dynamic range which is defined as the maximum received power variation at the receiver input which results in a correct demodulated signal. In others words, this means that the signal of interest may vary between the sensitivity and the sensitivity limit plus the dynamic range.

Thus, the dynamic range requirements for the receiver are calculated by the maximum and minimum received signal levels experienced at the receiver.

To calculate the maximum signal, assume a minimum transmit-receive separation distance and no shadowing losses. The maximum received power is then given by:

$$P_{R,MAX}(dBm) = P_T(dBm) - PL(dB)\Big|_{d \text{ min}}$$

(2.11)

Where  $P_T(dBm)$  represents the power transmitted.

Conversely, to calculate the minimum received signal, we assume a maximum transmit-receive distance and a maximum of shadowing loss. The minimum received power is thus given by:

$$P_{R,MIN}(dBm) = P_T(dBm) - PL(dB)_{d \max} - P_{Shadowing}(dB)$$

(2.12)

The worst-case shadowing loss  $P_{Shadowing}(dB)$  ( $X_{\sigma}$  in equation 2.8) must be assumed according with [9], in a typical situation 10dB. It should be taken account in our link analysis.

The difference between these two values determines the dynamic range requirements for the receiver. This is:

$$DR = P_{RMAX} - P_{RMIN} \tag{2.13}$$

In the next Table 2.5 we compare the distance where the value of sensitivity specify in the IEEE Std. 802.15.4 (-92dBm) is achieved with different output power from -30dBm to 3dBm, at 915MHz and for two cases:

case A: without shadowing

case B: assuming 10dB of shadowing

For this estimation, we use the IEEE Std. 802.15. 4 Channel Path Loss.

| Output Power (dBm) | -30  | -20  | -10  | -1   | 0    | 1    | 2    | 3     |

|--------------------|------|------|------|------|------|------|------|-------|

| Case A: D (m)      | 10.2 | 20.5 | 41.2 | 77.3 | 82.8 | 88.8 | 95.2 | 102.2 |

| Case B: D (m)      | 3.9  | 10.2 | 20.5 | 38.5 | 41.2 | 44.2 | 47.4 | 50.8  |

Table 2.5—Distance (m) at 915MHz where the value of sensitivity -92dBm takes place as function of output power

#### 2.2- KEY TOPICS of CMOS RF POWER AMPLIFIER

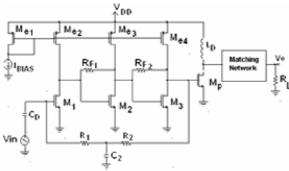

A power amplifier is a circuit for converting DC input power into a significant output power which is driven by an input low-level signal. Each application has its own requirements for frequency, bandwidth, load, power, efficiency and linearity, for this reason no single technique for power amplification or any single transmitter architecture is best for all applications. For instance, it is usual to employ architectures that concatenate progressively amplifiers to boost a low-level signal to the desired output power [10], as we can see in the next figure 2.6.

Figure 2.6: A four stage power amplifier (three preamplifiers and power amplifier Mp)

Before describing the tradeoff available to design efficient power amplifiers as we are going to discuss in the followings chapters we will first introduce a review of the architectures. Power amplifiers have different efficiencies depending on their operating conditions

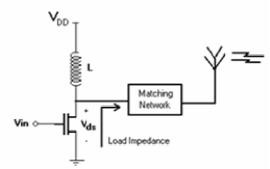

With reference to Figure 2.7, the three most well known classes of power amplifier will be discussed briefly. These amplifiers are distinguished principally by bias conditions and in this general model, the power amplifier is loaded with a matching network which adapt the antenna impedance and into which the PA deliver the output power [13]

Figure 2.7: Simplified output stage of a power amplifier

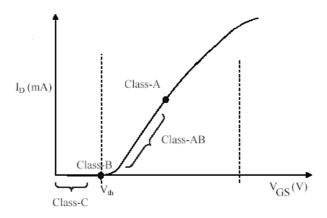

Class A: The transistor of the amplifier is biased in order to be always current source so that the amplifier operates quasi-linearly. Consequently, the distortion will be small at the cost of large current consumption reducing the efficiency of the amplifier. This is because the amplifier consumes power when there is not output signal. For resistive load, the maximum efficiency theoretically obtainable is 50%. It is important to underscore that this value of efficiency represent an upper limit and there are additional losses. We can see the drain voltage and current waveform in the figure 2.9

Class B: The transistor is active only half of every cycle so that the amplifier increase the efficiency because but gross departure from linear operation results and a high Q resonator is mandatory in order to filter out the harmonic of the drain current, leaving a sinusoidal drain voltage as class A has. In addition with the Q resonator, in order to obtain an acceptable approximation to a sinusoidal output voltage, it should be mentioned that differential or push-pull configuration is often used. For resistive load, the maximum efficiency theoretically obtainable is 78.5%. We can see the drain voltage and current waveform in the figure 2.9

**Class C:** The transistor of the amplifier is biased to cause the transistor to conduct less than half the time. The conduction angle of the transistor is smaller than 180 degree. Consequently, the drain current consists of a periodic train of pulses and the amplifier behaves non linearly and the distortion levels are high. As the conduction angle shrinks toward zero, the efficiency approaches 100% but the output power also tends toward zero at the same time.

Mainly, the efficiency can be large, but at the cost of reduced power-handling capability, gain and linearity. We can see the drain voltage and current waveform in the figure 2.9

To summarize, we present the following table 2.6:

| Class | Modes   | Conduction Angle (%) | Output<br>Power | Maximum<br>Efficiency (%) | Voltage Gain | Linearity |

|-------|---------|----------------------|-----------------|---------------------------|--------------|-----------|

| A     | Current | 100                  | Moderate        | 50                        | Large        | Good      |

| В     | Source  | 50                   | Moderate        | 78.5                      | Moderate     | Moderate  |

| C     |         | < 50                 | Small           | 100                       | Small        | Poor      |

**Table 2.6**: Summary of characteristics of power amplifier classes A,B and C [11]

And the following figures 2.8 and as well as 2.9 show operation point and current wave forms:

Figure 2.8: Operation point (bias), form figure 2.7, of Class-A, AB, B and C amplifiers [11]

Figure 2.9: Conduction angle relations [11]

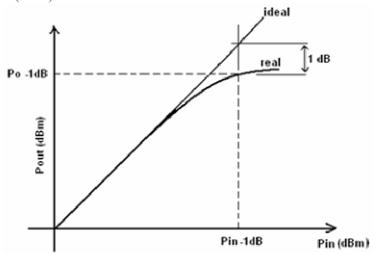

#### 2.2.1 Linearity

The need for linear power amplifiers arises in many RF applications. Many systems use frequency or phase modulation techniques for which non linear amplification is allowed.

For example, PSK do not require linear amplification from the modulation technique point of view but classic PSK use abrupt phase transitions or equivalently rectangular data pulses that require linear PAs to minimize spectral regrowth. The resultant sinc-function spectrum spreads signal energy over a fairly wide band-width and it is unsatisfactory for relatively low rates and low power devices.

On the other hand, techniques based on amplitude modulation require linear amplifiers to prevent systems performance degradation from excessive intermodulation distortion.

Nonlinearities cause imperfect reproduction of the amplified signal, resulting in distortion and splatter into adjacent channels and errors in detection.

Moreover and unfortunately the linearity requirement restricts amplifiers to operate below the maximum output power capacity thereby reducing the operation efficiency.

For this reasons, the importance of quantifying linearity and efficiency of power amplifier has provoked a review of different method to simulate and measure distortion. In this way, we can say that linearity is characterized and measured by various techniques depending on the specific signal and application.

A summary of traditional method is presented.

- C/I (carrier-to-intermodulation-ratio)

- ACPR (Adjacent Channel Power Ratio)

- NPR (Noise Power Ratio)

- EVN (Error Vector Magnitude)

#### C/I (carrier-to-intermodulation-ratio)

The traditional measure of linearity is the carrier-to-intermodulation ratio (C/I). The PA is driven with two tones carriers of equal amplitudes and nonlinearities cause the generation of intermodulation products at frequencies corresponding to sums and differences of multiples of the carrier frequencies.

The amplitude of the third-order or maximum intermodulation distortion (IMD) is compared so that of the carriers to obtain the  $\mathrm{C/I}$

#### ACPR (Adjacent Channel Power Ratio)

Adjacent Channel Power Ratio (ACPR) characterizes how nonlinearity affects adjacent channels and it is widely used with modern shaped-pulse digital signals.

Basically, ACPR is the ratio of the power in a specified band outside the signal bandwidth to the power in the signal. In other words, this parameter defines the amount of power transmitted at a certain offset frequency, compared to the power transmitted in the channel of interest [14].

$$ACPR = \frac{P}{P(\Delta f)} \tag{2.14}$$

Where:

$P(\Delta f)$ : Power transmitted at a certain offset frequency (normally the adjacent channel)

P: Power transmitted at the frequency of interest (channel)

#### NPR (Noise-Power Ratio)

It is a traditional method of measuring the linearity of PAs. The PA is driven with Gaussian noise with a notch in one segment of its spectrum. Nonlinearities cause power to appear in the notch and NPR is defined as the ratio of the notch power to the total signal.

#### EVM (Error Vector Magnitude)

Error Vector Magnitud (EVM) is a convenient measure of how nonlinearity interferes with the detection process in modern digital signals such as QPSK or QAM that are typically generated by modulating both I and Q sub carriers. In this way, EVM is defined as the distance between the desired and actual signal vectors.

#### 2.2.2 Efficiency

#### **Drain Efficiency**

Efficiency is a critical factor for PA design. Three definitions of efficiency are commonly used. Drain efficiency is the most common parameter to quantify efficiency and it is defined as the ratio of output power to DC input power

$$\eta_D = \frac{Pout}{P_{DC}} \tag{2.15}$$

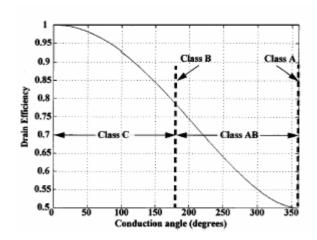

In figure 2.10, we can see the behaviour of the drain efficiency that is realized for a particular conduction angle for which the output voltage swing is maximum.

Figure 2.10: Drain efficiency versus conduction angle (load varied for maximum output voltage swing) [11]

The increased efficiency at a reduced conduction angle is achieved at the expense of decreased maximum power output. In the limit a class C PA would be achieved a drain efficiency approaching 100%, but the corresponding output power approaches zero.

#### Power Added Efficiency

Another measure of efficiency is the *Power Added Efficiency (PAE)*, that incorporates the amount of power that is delivered to the input.

$$PAE = \frac{Pout - Pin}{P_{DC}} = \eta_D \left( 1 - \frac{1}{G_P} \right) \tag{2.16}$$

#### Average Efficiency

Signal with time-varying (amplitude modulation) produce time-varying efficiencies. A useful measure of the performance is the average efficiency, which is defined as the ratio of the average output power to the average DC input power.

$$\eta_{AVG} = \frac{Pout_{AVG}}{Pin_{AVG}} = \frac{\int_{0}^{\infty} p(P_{out})P_{out}.dP_{out}}{\int_{0}^{\infty} p(P_{out})P_{DC}(P_{out}).dP_{out}}$$

(2.19)

The average input and output power are found by integrating the product of their variation with amplitude and the probability-density function.

#### 2.2.3 Filtering and Matching

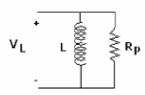

Power amplifier usually employs a matching network between the output transistor and the load. In class A stage if the transistor behaves as an ideal current source, the matching network transform the impedance load in another desired value that usually has no reactive components.

In contrast with the assumption that the drain current and voltage could be assumed sinusoidal, in practice, the large signal operation in class A introduces some harmonics as class B and AB do.

For this reason, for each amplifier, the matching circuits have to include some filtering properties (high Q output tank) in addition with the impedance transformation properties in order to suppress harmonics.

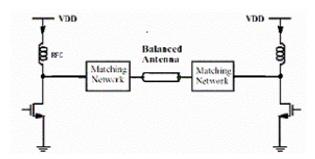

Furthermore, we have studied class AB and B power amplifier with single ended load but another important technique that reduces higher harmonic is the differential output. The single ended to differential conversion as we show in the figure 2.11, reduce the distortion by cancelling even harmonics.

Figure 2.11: Balanced output

Another important topic to underline is related to the maximum power transmission. It does not correspond with the maximum efficiency because if we match according with the maximum power transmission theorem, the power delivered to the load has the same value that is dissipated in the output impedance of the system, reducing the efficiency to 50% from the maximum.

The maximum power transmission theorem show that the power delivered by a voltage source to the load impedance takes maximum value when  $Z_o = Z_{load}^*$ , where  $Z_o$  is the source voltage output impedance and

$Z_{\it load}$  is the load impedance.

This theorem is used when the efficiency is not an important parameter or is not constrained, in comparison with the fact that usually a power amplifier is designed to deliver a specified amount of power into a load with the highest possible efficiency [13].

For example, in a class B stage amplifier, matching network has to be designed in order to get the maximum output voltage swing because it makes the maximum efficiency could be achievable and we do not design in function of the maximum power transmission theorem. For instance, we present the procedure to design a class B amplifier output stage given by the bibliography [13].

Following the notation and the explanation that uses the reference [13], we reproduce the next example:

In a class B amplifier, we assume that the drain current is sinusoidal for one half cycle.

$$i_D = i_o \sin(\omega t)$$

for  $i_D > 0$  (2.16)

We find the fundamental component of the drain current:

$$i_{fund} = \frac{2}{T} \int_{0}^{T/2} i_o \sin(\omega t) \sin(\omega t) dt = \frac{i_o}{2}$$

(2.17)

Then, multiply the fundamental current by the load resistance we have the fundamental output voltage:

$$V_o = \frac{i_o}{2} R \sin(\omega t) \tag{2.18}$$

And the output power:

$$P_o = \frac{V_o^2}{2R} \tag{2.19}$$

And the DC power consumed by the DC voltage source is:

$$P_{DC} = 2\frac{V_{DD}^2}{\pi R} \tag{2.20}$$

If the maximum value of the output amplitude is  $V_{\rm DD}$  , then the maximum output power delivered to the load resistance is:

$$P_{o MAX} = \frac{V_{DD}^2}{2R} {2.21}$$

To conclude:

$$\eta_{MAX} = \frac{P_{o\ MAX}}{P_{DC}} = \frac{\pi}{4} \approx 0.785$$

(2.22)

If the output power delivered to the load resistance  $R_L$  is given or specified value  $P_L$ , then, the value of the resistance load that maximize the efficiency is given from (2.21)

$$R_{optima} = \frac{V_{DD}^2}{2P_I} \tag{2.23}$$

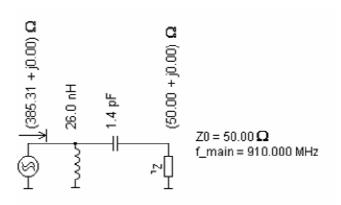

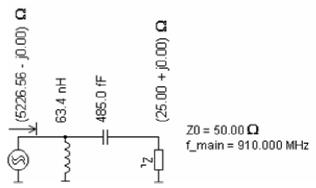

Finally, we need to develop a network that transforms the resistance from  $R_L$  to  $R_{optima}$ . After that, we present a numerical example. Let us assume:

- $R_L$ = 50  $\Omega$

- $-V_{\rm DD} = 3V$

- frequency = 910MHz

- $P_o=11.69 \text{ mW}$   $\rightarrow \text{from (2.23)} \text{ R}_{optima}=385 \Omega$

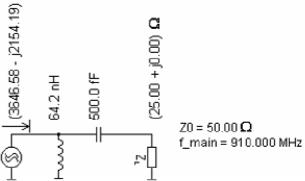

Thus, the network must transform  $R_L$  to  $R_{optima}$  as it is shown in the following figure 2.12: (The software used to create the matching network is SMITH V.191 [15])

Figure 2.12: Adaptation network of the example

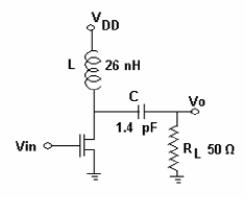

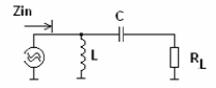

Finally, our amplifier would be schematized in the following figure 2.13:

Figure 2.13: Final amplifier of the example

#### 2.3- REFERENCES

- [1] Frank Karlsen "Guidelines to low cost wireless system design" Wireless Communications, Nordic VLSI ASA

- [2] Asad A.Abidi "RF CMOS Comes of Age" IEEE Journal of Solid Sate Circuits VOL. 39 No 4, April 2004 ISBN 0018-9200/04\$20.00 pp. 549-561

- [3] Shuguang Chui, et.al. "Energy Constrained Modulation Optimization" To appear at IEEE Transactions on Wireless Communications-Manuscript received July 27,2003 and presented at ICC03 and Globecom 03

- [4] IEEE-802.15.4TM-2003 Standard for Information technology—Telecommunications and information exchange between systems—Local and metropolitan area networks—Specific requirements Part 15.4:Wireless Medium Access Control (MAC) and Physical Layer (PHY) Specifications for Low-Rate Wireless Personal Area Networks (LR-WPANs). Published by The Institute of Electrical and Electronics Engineers, Inc. 3 Park Avenue, New York, NY 10016-5997, USA 1 October 2003

- [5] Jose A.Guitierrez et.al. "Low-Rate Wireless Personal Area Network" IEEE Published by Standards Information Network IEEE Press –ISBN 0-7381-3557-7

- [6] Behzad Razavi "RF Microelectronics" pp. 298-311 ,Prentice Hall PTR -1998, ISBN 0-13-887571-5

- [7] P.Harley "Short Distance Attenuation Measurements at 900MHz and 1.8GHz Using Low Antenna Heights for Microcells " IEEE JSAC, vol.7, No 1, Jan 1989

- [8] A. F. Molisch et al., "Ieee 802.15.4a channel model final report," Tech. Rep. Document IEEE 802.15-04-0662-02-004a, 2005.

- [9] Craig Michael Teuscher "Design and Implementation of an Adaptive Multiuser Detector for an Indoor, Wideband CDMA Application" University of California, Berkeley-1998

- [10] A.S.Porret, T Melly, D.Python, C.C.Enz, E.A.Vittoz. "An Ultralow Power UHF Transceiver Integrated in a Standard Digital CMOS Process: Architecture and Receiver". *IEEE Journal of Solid-Sate Circuit VOL 36*, NO 3, March 2001 pp. 452-466.

- [11] Sajay Jose "Design of RF CMOS Power Amplifier for UWB Applications" Thesis submitted to the faculty of Virginia

Polytechnic Institute and State University -December 2004 Blacksburg, Virginia

- [12] Ravi Gupta, Brian M. Ballweber, and David J. Allstot, "Design and Optimization of CMOS RF Power Amplifiers" IEEE Journal of Solid-State Circuits VOL. 36, No. 2, February 2001 pp.166-175

- [13] Thomas H.Lee "The Design of CMOS Radio Frequency Integrated Circuits" ,Cambridge University Press 1998,ISBN 0-52163061-4

- [14] Domine Leenaerts et.al, "Circuits Design for RF Transceiver" pp. 145-166, Kluwer-2001 ISBN 0-7923-7551-3

- [15] Software *SMIT V1.91* University of Applied Sciences Berne Berne Institute of Engineering and Architecture F. Dellsperger Professor Morgartenstrasse 2c CH-3014 Bern Switzerland Fax. ++41 31 33 30 625 e-mail fritz.dellsperger@hta-be.bfh.ch

## MOS Transistor Model for RF IC Design

**Chapter Overview** — Modelling of devices is a key step into design processes because without good models, it becomes difficult to analyze and predict circuit behaviour. The purpose of this chapter is to study a compact high-frequency MOSFET model and how it could be implemented in our tool. The model used for the MOS transistor is the ACM model which was presented by Galup-Montoro et al. [3] and as we will see throughout this chapter, this model has desirable characteristics from the designer point of view.

#### 3.1 BACKGROUND

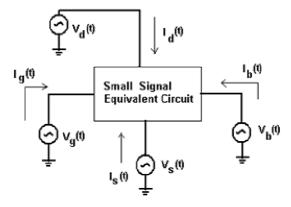

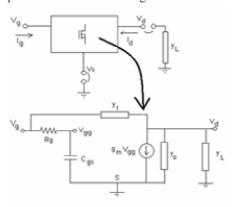

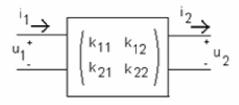

Design of very-high-frequency circuits is often done by using the so-called "y-parameters" [1][2]. In this section we will first show the general form of this model in order to apply it to the MOS transistor in our tool. First we consider a device that is driven by bias and small—signal voltages at each terminal as shown in Figure 3.1.The effect of each voltage terminal on each current terminal, in the sinusoidal state and using phasor representation are summarized in the followings equations [1]:

$$i_d = y_{dd} v_d + y_{dg} v_g + y_{db} v_b + y_{ds} v_s (3.1)$$

$$i_g = y_{gd}v_d + y_{gg}v_g + y_{gb}v_b + y_{gs}v_s$$

(3.2)

$$i_b = y_{bd}v_d + y_{bg}v_g + y_{bb}v_b + y_{bs}v_s (3.3)$$

$$i_s = y_{sd} v_d + y_{sg} v_g + y_{sb} v_b + y_{ss} v_s (3.4)$$

**Figure 3.1** The small signal equivalent model terminals (admittance matrix representation) (Figure adapted from [1], figure 9.13)

Where:

$v_g$  and  $i_g$ : gate voltage and gate current  $v_d$  and  $i_d$ : drain voltage and gate current  $v_s$  and  $i_s$ : source voltage and gate current  $v_b$  and  $i_b$ : bulk voltage and gate current

This definition of admittance parameters is standard in circuit theory and it is known as an admittance matrix representation. Assuming the bulk terminal as a potential reference, a fact verifiable directly by writing Kirchoff's law is that this model would be represented as another three ports, three current y-parameter. It could be rewritten in the same form that the bibliography [1] has done, as follows:

$$i_d = -y_{gd}v_{dg} - y_{sd}v_{ds} - y_{bd}v_{db} + y_m v_{gs} + y_{mb}v_{bs}$$

(3.5)

$$i_g = -y_{gd}v_{gd} - y_{gb}v_{gb} - y_{gs}v_{gs}$$

(3.6)

$$i_b = -y_{bd}v_{bd} - y_{gb}v_{bg} + y_{mx}v_{gb} - y_{bs}v_{bs}$$

(3.7)

(From [1], this correspond with equations 9.39a, 9.3.9b, 9.3.9c)

Where the following parameter were defined as:

$$y_m = y_{dg} - y_{gd} \tag{3.8}$$

$$y_{mb} = y_{db} - y_{bd} \tag{3.9}$$

$$y_{mx} = y_{bg} - y_{gb} ag{3.10}$$

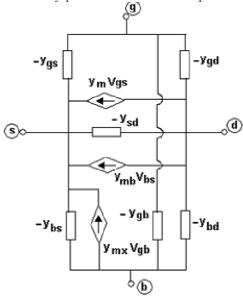

The above set of equations can be represented by the circuit of Figure 3.2. Each  $y_{gs}$ ,  $y_{gd}$ ,  $y_{sd}$ ,  $y_{bs}$ ,  $y_{bd}$ ,  $y_m$ ,  $y_{mb}$ ,  $y_{mx}$  and  $y_{gb}$  are represented only symbolically for the moment. We will derive actual parameters and represent them in circuit form, in the following sections. At the moment, a four port fictitious device have been studied and figure 3.2 shows the configurations of y-parameter networks to represent equations (3.5) to (3.10).

**Figure 3.2** A general model for four terminal MOS transistor device according with equation (3.5 to 3.10) (Figure adapted from [1], figure 9.17)

Remember that the y<sub>-</sub> parameters for the moment have been represented only symbolically.

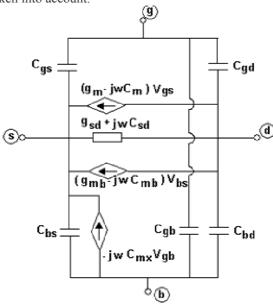

As a special case of this model is the simple quasi-static small-signal model of the intrinsic part of the MOS transistor that is shown in Figure 3.3, which has the same topology that has just shown in figure 3.2. This is the complete quasi static small signal model for the MOS transistor, where capacitance effects of the drain, source, substrate and gate has been taken into account.

**Figure 3.3** A simple quasi-static intrinsic small-signal model for the MOS transistor (Figure adapted from [1], figure 9.5)

In order to define the quantities that match the physical model which has just been shown in the figure 3.2 with the figure 3.3, the following quantities have been defined in the literature [1];

$$-y_{sd} = j\omega C_{sd} \tag{3.11}$$

$$-y_{gs} = j\omega C_{gs} \tag{3.12}$$

$$-y_{bd} = j\omega C_{bd} \tag{3.13}$$

$$-y_{bs} = j\omega C_{bs} \tag{3.14}$$

$$-y_{\sigma h} = j\omega C_{\sigma h} \tag{3.15}$$

$$-y_{sd} = g_{sd} + j\omega C_{sd} \tag{3.16}$$

$$y_m = g_m - j\omega C_m \tag{3.17}$$

$$y_{mb} = g_{mb} - j\omega C_{mb} \tag{3.18}$$

$$y_{mx} = -j\omega C_{mx} \tag{3.19}$$

The equations (3.11) to (3.15) use five intrinsic capacitances:  $C_{gd}$ ,  $C_{gs}$ ,  $C_{bd}$ ,  $C_{bs}$ ,  $C_{gb}$  and for equation (3.16) to (3.19) three transcapacitances and a capacitance have been used and included as:  $C_m$ ,  $C_{mb}$ ,  $C_{mx}$  and  $C_{sd}$ .

Then, the above relations require no less and no more than six intrinsic capacitances and three transcapacitances:

$$C_{od}$$

,  $C_{os}$ ,  $C_{bd}$ ,  $C_{bs}$ ,  $C_{ob}$ ,  $C_{m}$ ,  $C_{mb}$ ,  $C_{mx}$ ,  $C_{sd}$  (3.20)

To provide more feeling about the model, we can say that each capacitance and transcapacitance represents the effect of each terminal voltage called K, on each terminal current called L, where K and L can be Drain, Gate, Source or Bulk and it is not necessary a real capacitance.

For instance, we may have tendency to think of  $C_{gd}$  and  $C_{dg}$  as the capacitances of two terminal capacitors between drain and gate but such interpretation is not correct. The  $C_{gd}$  represents the effect of the drain on the gate and  $C_{dg}$  represents the effect of the gate on the drain in terms of charging currents.

On the other hand, usually  $C_{mx}$  is very small and will be unimportant in most practical cases and note also that in saturation some capacitances get value zero due to the drain voltage does not influence the device charges. That is expressed as:

$$C_{gd} = C_{bd} = 0 (3.21)$$

As well as the capacitance:

$$C_{sd} = 0 ag{3.22}$$

Finally, it is important to remark that the model that has been presented is a quasi-static model (QS), and is based on the hypothesis that the charge in the channel can reach the balance instantly after applying electrical stimulus. However, the limitation of the QS model is well known and it will be better explained in the next section

#### 3.1.1 The ACM Model

In this work we use the model developed by Galup-Montoro et al. [3]. This model meets several requirements from the designer point of view and is referred as the ACM model from herein. This model is useful for our thesis work because of:

- The model is single piece; it has accurate expressions and presents simple equations as function of the inversion level

- The model has a few parameters but just enough and those parameters are linked strongly with the device structure and fabrication process because the model is physically based

- In addition, the model conserves charge and it correctly represents all the regions of operation

Let us now resume the main expressions of the ACM model because they will be used throughout this work. The MOSFET drain current is expressed as very simple functions of two components of drain current, namely, the forward and reverse saturation currents.

$$I_D = I_s \left( i_f - i_r \right) \tag{3.23}$$

Where  $i_f(i_r)$  is the forward (reverse) normalized current and the normalization current is:

$$I_{S} = \frac{1}{2} \mu n C_{ox}^{'} U_{T}^{2} \frac{W}{L}$$

(3.24)

Where these parameters are:

- *n*: Is the *slope factor*, which is slightly dependent on the gate voltage, but it can be assumed constant for hand calculations and usually n takes value from 1.2 to 1.6 for bulk technology.

- $\mu$ : carriers mobility in the channel

- $\bullet$  W, L: are the channel width and length respectively.

- $C_{ox}$ : oxide capacitance per unit area

•  $U_T$ : Thermal voltage

The forward normalized current  $i_f$  is also referred as the inversion factor since it indicates the inversion level of the MOSFET. As a rule of thumb, values greater than 100 characterize strong inversion and values below 1 characterize weak inversion. Values between 1 and 100 indicate moderate inversion. The pinch-off voltage is defined as:

$$V_P = \frac{V_G - V_{TO}}{n} \tag{3.25}$$

Where every voltage is referred to the bulk voltage, and:

- $V_G$ : is the gate voltage

- $V_{TO}$ : is the threshold voltage when source voltage  $V_S$ , is zero.

The relationship between current and voltage is given by:

$$V_P - V_{S(D)} = U_T \left( \sqrt{1 + i_{f(r)}} - 2 + Ln \left( \sqrt{1 + i_{f(r)}} - 1 \right) \right)$$

(3.26)

$V_{S(D)}$  is the source (drain) voltage.

Used with equation (3.25), we can estimate from this expression, the gate voltage in a forward saturated transistor as a function of the inversion level and the source voltage.

$$V_{G} = V_{TO} + nV_{S} + U_{T} \left( \sqrt{1 + i_{f}} - 2 + Ln \left( \sqrt{1 + i_{f}} - 1 \right) \right)$$

(3.27)

Finally, as we have seen, six capacitances and three transcapacitances characterize the MOS transistor. The complete expressions for these capacitances can be found in reference [3]. Here we will only give an expression for the gate capacitance in the case of a forward saturated transistor with source voltage zero:

$$C_{gs(d)} = C_{ox} \frac{2}{3} \left( 1 - \frac{1}{\sqrt{1 + i_{f(r)}}} \right) \left( 1 - \frac{1 + i_{r(f)}}{\left( \sqrt{1 + i_f} + \sqrt{1 + i_r} \right)^2} \right)$$

(3.28)

$$C_{gb} = C_{bd} = \frac{n-1}{n} \left( C_{ox} - C_{gs} - C_{gd} \right)$$

(3.29)

#### 3.1.2 The $g_m/I_D$ ratio

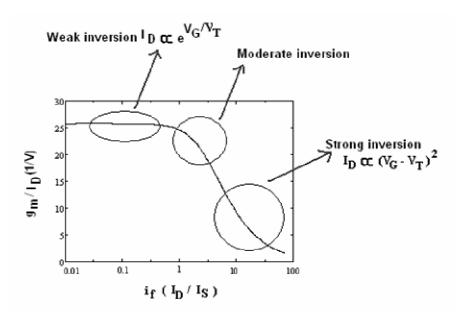

The  $(g_m/I_D)$  ratio is a key parameter in the design methodologies presented in this work. The ACM model provides a simple expression for the  $(g_m/I_D)$  ratio in a forward saturated MOS transistor as a function of the inversion level:

$$\frac{g_m}{I_D} = \frac{1}{nU_T} \frac{2}{\sqrt{1 + i_f} + 1} \tag{3.30}$$

The methodology based on  $g_m/I_D$  ratio considers the relationships between the transconductance over drain current ratio and the normalized drain current, this relationship can be seen in Figure 3.4 where the three regions, strong, moderate and weak inversion, are shown.

This methodology is very useful because it gives us an accurate indication of the device operation region as well as provides the expression to calculate the transistor dimension.

**Figure 3.4** Relationship between the inversion factor  $i_f$  and the  $(g_m/I_D)$  ratio.

#### 3.1.3 Non Quasi-Static Boundary

At this point, one may reasonable think how can highly simplified models be of any use at RF. There are several factors to take into account:

The model presented will become inaccurate at higher frequency when:

- 1) Extrinsic parasites such as overlap capacitances and gate resistance will appear in the device behaviour because these parasites create poles.

- 2) If all voltage terminals are varying very slowly, the inversion layer charge has time to follow the input with practically no delay. However, if the variation of voltage is fast, the "inertia" of the inversion layer becomes non negligible. The inversion layer charge does not have enough time to respond fully. These effects are broadly categorized as non-quasi static (NOS) behaviour[1][5]

The most notable difference between the QS and NQS models appears to be the specific dependence of  $g_m$  with the frequency. The frequency limits of validity is provided in the literature as only rough indications of the regions within which a given model will perform satisfactorily in most cases. There is not a unique limit and general agreement for the boundary frequency does not exist.

To summarize, the frequency limits in <u>strong inversion</u>, provided in [1] are the follows:

- Quasi static model without transcapacitances: frequencies below  $\frac{\omega_o}{10}$

- Quasi static model with transcapacitances: frequencies below  $\frac{\omega_o}{3}$

• First order non quasi static model: frequencies below  $\omega_o$

Where:

$$\omega_0 = \frac{\mu (V_{GS} - V_T)}{\alpha L^2} = \frac{4}{3\tau} \tag{3.31}$$

ullet lpha : coefficient of first –order term in expansion for  $-Q_{B}^{'}/C_{ox}^{'}$

$\bullet$  L: are the channel length.

•  $\tau$ : transit time defined as the average time that a carrier takes for travel the length of the channel.

On the other hand, many NQS models have been proposed in the literature, taking into account different effects and with different degrees of approximation. These models need replacing the intrinsic capacitances and transconductances with higher order admittances and transadmittances [2]. As an example we show the analytical expression of some of them in order to get a feeling.

Some of the equations (3.11) to (3.15) become frequency dependents as follow[1]:

$$y_m = \frac{g_m}{1 + j\omega\tau_1 + \dots} \tag{3.32}$$

$$-y_{gs} = j\omega C_{gs} \frac{1 + j\omega \tau_2 + \dots}{1 + j\omega \tau_1 + \dots}$$

(3.33)

$$-y_{sd} = \frac{g_{sd}}{1 + i\omega\tau_1 + \dots}$$

(3.34)

$$-y_{bs} = j\omega C_{bs} \frac{1 + j\omega \tau_2 + \dots}{1 + j\omega \tau_1 + \dots}$$

(3.35)

Where, the first order time constant is [3]:

$$\tau_1 = \frac{L^2}{\mu U_T} \frac{1}{5} \frac{1}{\sqrt{1 + i_f}} \tag{3.36}$$

Assuming  $\omega \tau_1 \ll 1 \Rightarrow \frac{1}{1 + j\omega \tau_1} \approx 1 - j\omega \tau_1$

Thus, we can write:

$$y_m \approx g_m - j\omega \tau_1 g_m \tag{3.37}$$

A comparison with  $y_m$  obtained for the complete quasi static model (3.17) shows that the form is the same. An examination of the expressions reveals that:  $\tau_1 g_m = C_m$ . Thus, this NQS model could be reduced to the complete quasi static model. The expression is in fact identical, only the form, because the coefficients are different. That is a big problem due to in both models, the value of  $g_m$  is dependent of the frequency. Thus, where is the non quasi static limit exactly, called  $f_{NQS}$  from herein? It is possible to determine the non quasi static limit when the value  $g_m$  stars to drop, due to in both models,  $g_m$  is gone down at higher frequency?

In the literature [1][5], the quasi static assumption used for deriving the small signal circuit does not hold anymore when the frequency gets close to the intrinsic cut-off frequency of the device defined as the frequency at which the short circuit current gain of the transistor becomes unit.

Let us considerer a transistor where the bias is assumed such that operation is in saturation region, the cut- off frequency is defined as the transition frequency at which the common-source small signal current gain becomes unity at short- circuit load, thus we have:

$$f_T = \frac{g_m}{C_{gs} + C_{gd} + C_{par}}$$

(3.38)

Capacitance Cpar includes overlap capacitance and interconnect capacitance to the substrate.

In practice, the current gain of a complete transistor becomes unity at some frequency less than the cut-off frequency due to the presence of extrinsic parasitic elements and velocity saturation.

In general is accepted that the onset frequency of NQS effect is found to be comparable to  $f_T$  and the QS model can do a good job when the operation frequency is sufficiently below  $f_T$ . In this work we use this criterion.

In addition, [3], a typical value  $f_T$  can be roughly approximated to:

$$f_T = \frac{\mu U_T}{2\pi L^2} 2\left(\sqrt{1 + i_f} - 1\right) \tag{3.39}$$

According with [3], the no quasi static correction is significant only for moderate and strong inversion. In weak inversion the quasi static model presented predicts dynamic operation with satisfactory precision at frequencies up to intrinsic cut-off frequency. In moderate and strong inversion the applicability of the quasi-static model should be restricted to frequency values up to one-third of the intrinsic cut-off frequency.

To summarize, the onset frequency of NQS effect is found to be comparable to  $f_T$  and the QS model can do a good job when the operation frequency is sufficiently below  $f_T$ . In this work we use equation (3.52) (see next section).

In addition with this, the modelling of extrinsic effects (source, drain, gate, and substrate resistance, overlap and junction capacitances) must be done with accuracy and taken into account

The performance of the device is largely determined by the geometry of the device, resulting from its layout. Let us considerer a device of length L and width W and we can see in principle there are three possible layout structures.

The first option is a single structure, which means that the device is drawn or laid out as rectangle with width W and length L. It is shown in the figure 3.5. This structure is usually used in digital circuit but, in contrast in RF applications, this is the worst geometry due to gate resistance. The gate resistance can be approximated by:

$$R_g = \frac{1}{3} \frac{W}{L} R_{sq,poly} \tag{3.40}$$

Where  $R_{sq,poly}$  is the sheet resistance of polysilicon.

Figure 3.5 Single structure for a MOS transistor

The second option is a parallel structure, where the device is laid out as n devices in parallel structures with each device with a width W/n. If the gate has contacts at both sides, this device has lower gate resistance than the single device because of the reduced width. This structure will reduce the gate resistance but must be used carefully because the drain junction capacitance is increased and it is not optimal due to the parasitic capacitance reduces the cut-off frequency.

The last option can be seen in figure 3.6 and it is a finger structure where the gate is connected from two sides using metal interconnects where a very low total gate resistance could be achieved. To reduce the contribution of the poly resistance to the gate resistance to less than a few ohms, the device must have as many finger as possible. Nevertheless, this layout will increase gate capacitances causing the degradation of  $f_T$ .

Figure 3.6 Finger structure for a MOS transistor

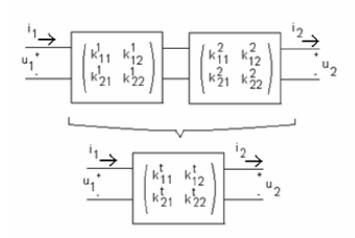

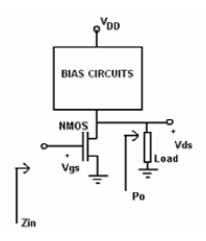

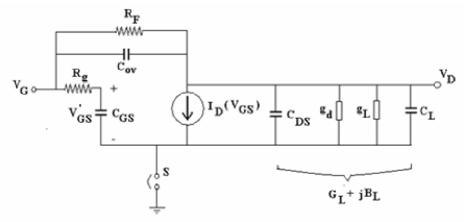

#### 3.2 TOOL MODELLING APPROACH

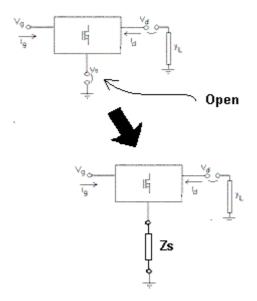

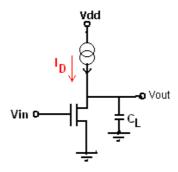

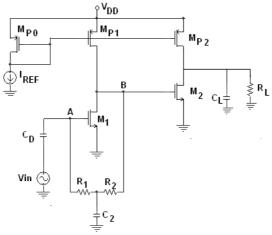

The basic amplifier structures considered in figure 2.6 (preamplifiers stages  $M_{1,2,3}$  and output power amplifier stage  $M_p$ ) could be modeled by quadripoles as it is shown in Figure 3.7.

Figure 3.7: MOS Transistor and basic block model

Assuming source voltage as voltage reference and bulk voltage zero, the two port relations of the quadripole in Fig. 3.7 can be written using equation 3.1 and 3.4 as:

$$i_{d} = y_{dd}v_{ds} + y_{dg}v_{gs} i_{g} = y_{gd}v_{ds} + y_{gg}v_{gs}$$

(3.41)

Assuming that MOS transistor operates in saturation and in the quasi-static regimen as it has been discussed, the y- parameters are:

$$y_{dd} = y_O + y_f \tag{3.42}$$

$$y_{dg} = \frac{g_m}{1 + j.2\pi.f.R_g C_{gs}} - y_f \tag{3.43}$$

$$y_{gd} = -y_f \tag{3.44}$$

$$y_{gg} = \frac{j.2\pi.f.C_{gs}}{1 + j.2\pi.f.R_gC_{gs}} + y_f$$

(3.45)

Where:

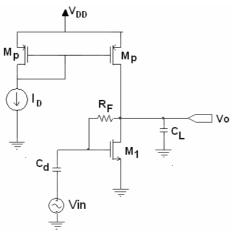

- $y_f$ ,  $y_o$  are respectively the feedback and the output admittances, which include parasites capacitances of the MOS transistor and external components, such as a drain gate feedback resistor when it is added (it is better explained in the next chapter)

- $C_{gs}$ : is the total gate-source capacitance equal to the sum of the gate-source and the gate-substrate capacitances (intrinsic and extrinsic).

- $R_{\sigma}$  : is the gate resistance and f is the frequency.

The admittances shown in equation (3.42) to (3.45) include five intrinsic capacitances and extrinsic capacitances (gate - source and gate - drain overlap capacitances and drain - substrate and source - substrate junction capacitances). For the intrinsic capacitances, the medium frequency, five capacitor model is deemed enough as it has been discussed. Thus, we can write:

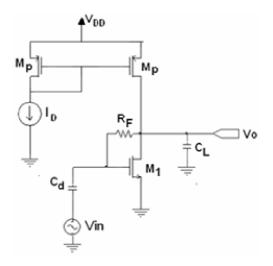

$$y_f = \frac{1}{R_F} + j.2.\pi.f.C_{ov}.W$$

(3.46)

Where:

- W: is the transistor width

- $C_{ov}$ : is the gate-drain overlap capacitance by channel width

- $\bullet$   $R_F$ : is the drain gate feedback resistor (some architectures have this in order to get better matching impedance and flatter frequency response at high frequency and must be included in our model.(see figure 3.8 as an example )

The intrinsic load is:

$$y_O = g_d + j.2.\pi.f.C_{db} (3.47)$$

Where:

- $g_d$  is the small signal output conductance of the MOS transistor.

- ullet  $C_{db}$  is the extrinsic drain substrate parasitic capacitance given by:

$$C_{db} = X.W C_j + (W + 2X).C_{jsw} + W.C_{jswg}$$

(3.48)

Where:

• X is the length of the source and drain regions

- $C_i$  is the drain-substrate capacitance per area,

- $C_{isw}$  is the sidewall parasitic capacitance per unit width

- $\bullet$   $C_{iswg}$  is the sidewall parasitic capacitance per unit width in the channel side of the drain area.

The capacitances,  $C_j$ ,  $C_{jsw}$  and  $C_{jswg}$  must be corrected in function of the parameters  $M_{JSW}$  (sidewall junction grading coefficient) and  $P_B$  (junction potential) and the voltage applied to the junction in the following form:

$$C_{j}(V) = \frac{C_{j}}{\left(1 + \frac{V}{P_{B}}\right)^{M_{JSW}}}$$

$$(3.49)$$

The extrinsic load is:

$$y_L = \frac{1}{Z_{load}} + \left(gd + j.2.\pi.f.C_{db}\right)_{current \ source}$$

(3.50)

This expression is composed by the real external load  $\frac{1}{Z_{load}}$  and the term  $(gd + j.2.\pi.f.C_{db})_{current\_source}$

models the impedance of the bias circuit (which is not shown in Fig.3.7) but we can see an example in the following figure.

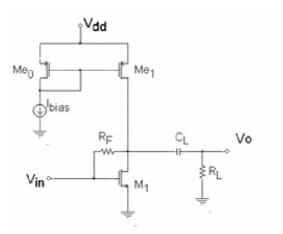

Figure 3.8: Circuit for example

With these expressions, the four admittances can be written as a set of equations suitable to work in MATLAB. Finally, the voltage gain G of the stage is given by:

$$G = \frac{v_{ds}}{v_{gs}} = \frac{-y_{dg}}{y_{dd} + y_L}$$

(3.51-a)

And then:

$$A\left(I_{D}, \frac{g_{m}}{I_{D}}\right) = |G| = \frac{|y_{21}|}{|y_{22} + y_{L}|}$$

(3.51-b)

The model that has been presented is a quasi-static model (QS). That is why it is important to have an estimation

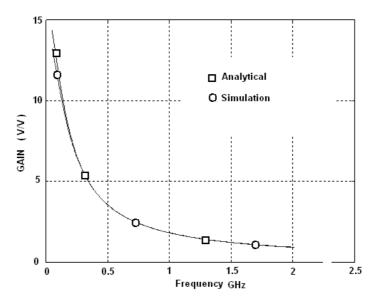

of the frequency which limits the zones of QS and NQS operation. This limit has been fixed at  $0.1 f_T$  (where  $f_T$  is the unitary gain frequency or also called cut-of frequency) as it is proposed in [1][5] and also we have extensity discussed:

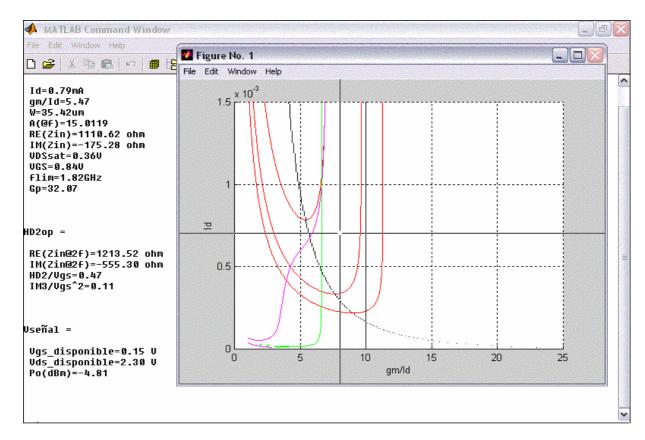

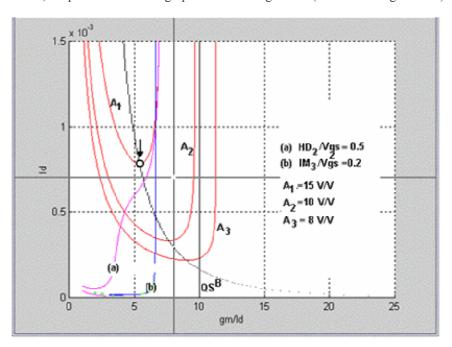

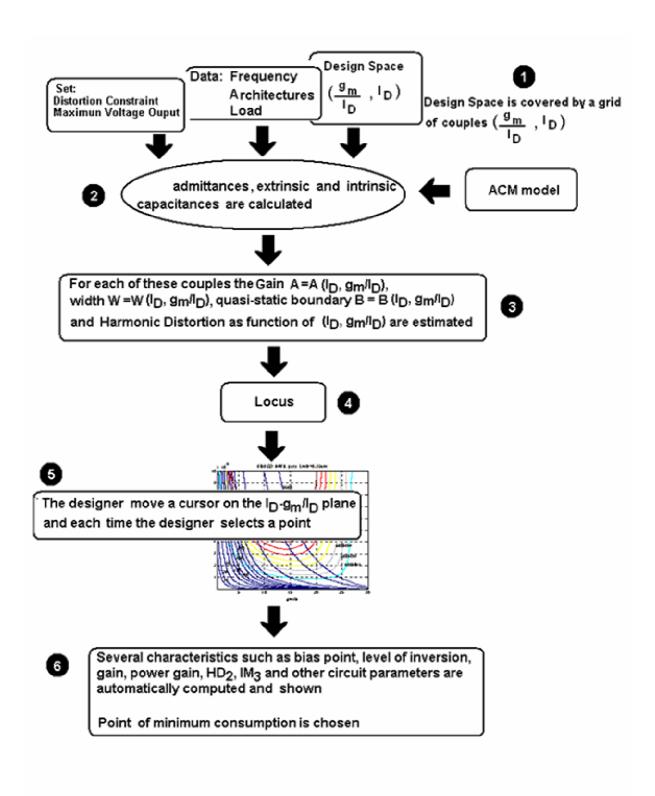

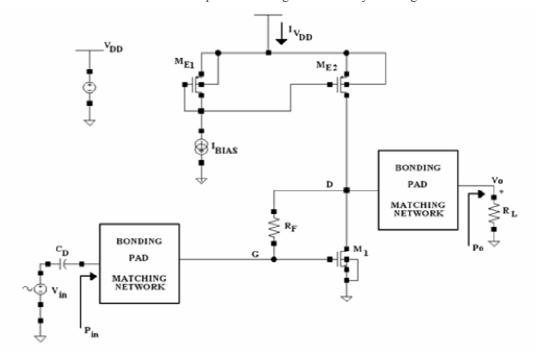

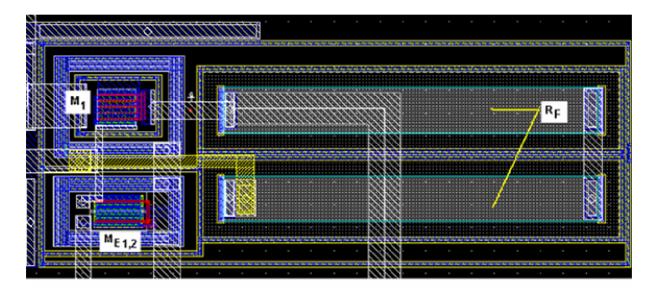

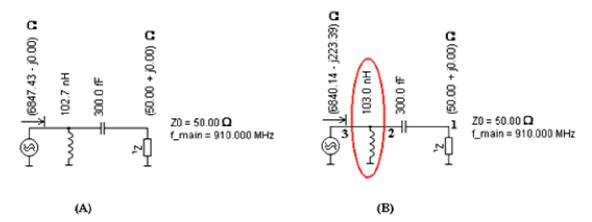

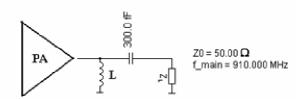

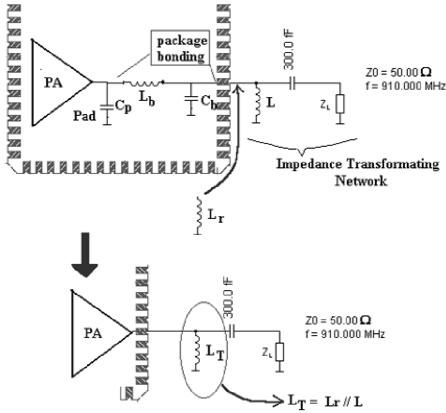

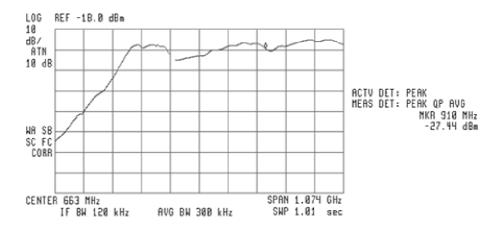

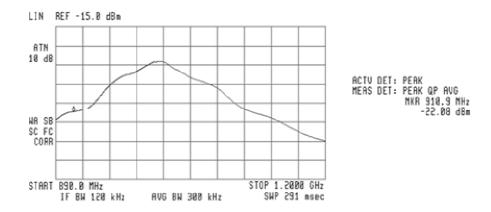

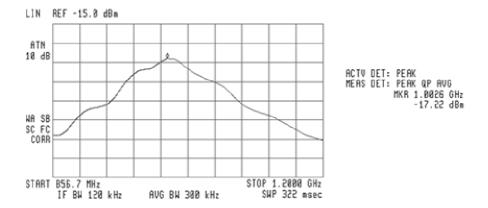

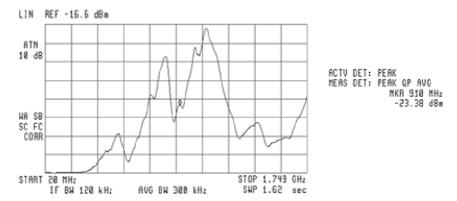

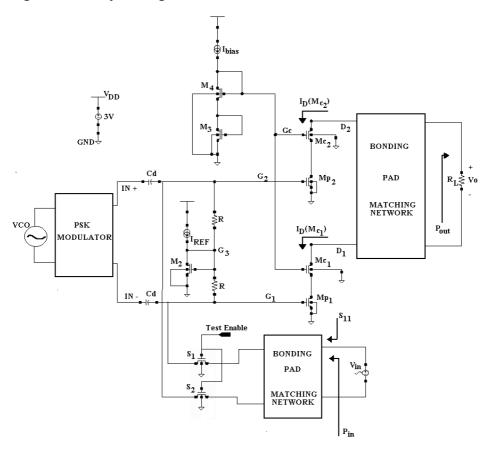

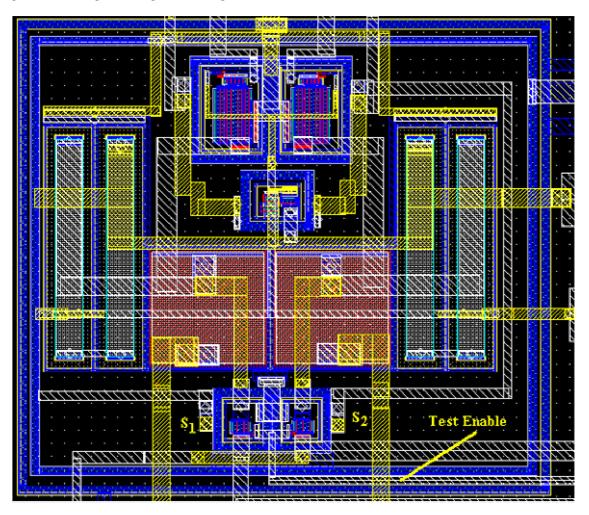

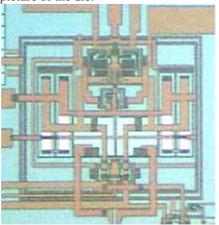

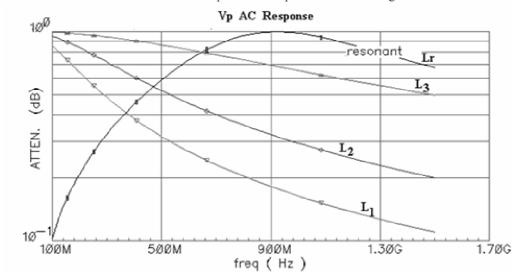

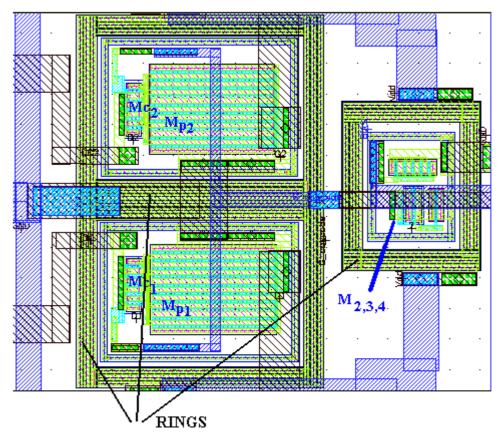

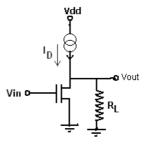

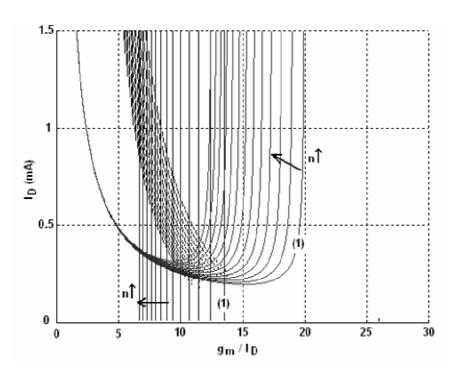

$$f_{QS \max} \approx \frac{f_T}{10} = \frac{0.1 g_m}{2\pi (C_{gs} + C_{gb} + C_{gd})}$$