# Automatic Reusable Design for Analog Micropower Integrated Circuits

Por

### Pablo Aguirre

Tesis Presentada Ante el Instituto de Ingeniería Eléctrica Para Cumplir con Parte de los Requisitos del Grado de

MAGISTER EN INGENIERÍA ELÉCTRICA

En el Área de MICROELECTRÓNICA

Tutor:

Prof. Fernando Silveira

#### Tribunal:

Prof. José Silva-Martinez, Texas A&M, USA.

Prof. Carlos Galup-Montoro, UFSC, Brasil.

Prof. Gregory Randall, UDELAR, Uruguay.

Instituto de Ingeniería Eléctrica Facultad de Ingeniería Universidad de la República Montevideo, Uruguay

Abril 2004

ISSN: 1510-7264

Type setted in LATEX  $2_{\mathcal{E}}$

## Contents

| Lis | st of I | Figures  |                                                       | vi   |

|-----|---------|----------|-------------------------------------------------------|------|

| Lis | st of   | Tables   |                                                       | ix   |

| Lis | st of . | Algoritl | nms                                                   | Х    |

| Αs  | grade   | cimient  | OS                                                    | xi   |

|     |         |          |                                                       |      |

| K€  | esume   | en       |                                                       | .111 |

| Al  | ostrac  | et       |                                                       | ΧV   |

| 1.  | Intro   | oductio  | n                                                     | 1    |

| 2.  | Desi    | gn Met   | hodologies                                            | 5    |

|     | 2.1     | Introd   | uction                                                | 5    |

|     | 2.2     | A Cur    | rrent-Based MOSFET Model for IC Design                | 5    |

|     |         | 2.2.1    | Current - Voltage Relationships                       | 6    |

|     |         | 2.2.2    | The $(g_m/I_D)$ Ratio                                 | 7    |

|     |         | 2.2.3    | Intrinsic Capacitances                                | 7    |

|     |         | 2.2.4    | Noise Model                                           | 8    |

|     |         | 2.2.5    | Output Conductance                                    | 10   |

|     |         | 2.2.6    | Non-quasi-static Model and Second Order Effects       | 10   |

|     |         | 2.2.7    | Why ACM?                                              | 10   |

|     | 2.3     | The (g   | $g_m/I_D$ ) Based Methodology for Analog Design       | 10   |

|     | 2.4     | Auton    | natic Synthesis for Miller Amplifiers                 | 12   |

|     |         | 2.4.1    | The Miller Amplifier                                  | 12   |

|     |         | 2.4.2    | Gain-Bandwidth Driven Synthesis Algorithm             | 17   |

|     |         | 2.4.3    | Design Optimization Through Design Space Exploration  | 17   |

|     |         | 2.4.4    | Synthesis Example: Micropower 100kHz Miller Amplifier | 19   |

|     |         | 2.4.5    | Synthesis Example: 50MHz Miller Amplifier             | 25   |

|     | 2.5     | Concl    | usions                                                | 29   |

| 3.  | Low     | -Power   | OpAmp Cells: Reuse, Architecture and Synthesis        | 31   |

|     | 3.1     | Introd   | luction                                               | 31   |

|     | 3.2     | Analo    | g Design Reuse                                        | 31   |

|    |       | 3.2.1    | Circuit Performance Tuning Through Bias Current                                                            | 32 |

|----|-------|----------|------------------------------------------------------------------------------------------------------------|----|

|    |       | 3.2.2    | Reusable Circuit Architectures                                                                             | 36 |

|    |       | 3.2.3    | Technology Migration                                                                                       | 39 |

|    | 3.3   | Opam     | p Architecture                                                                                             | 40 |

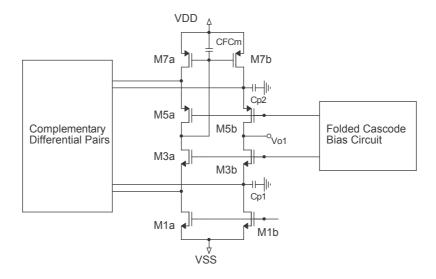

|    |       | 3.3.1    | Constant gm Rail-to-Rail Input Stages                                                                      | 40 |

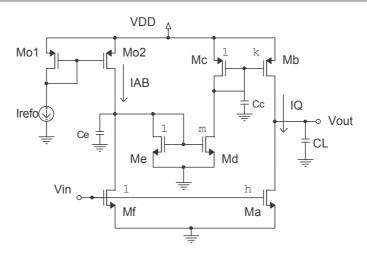

|    |       | 3.3.2    | Low-Power Class AB Output Stage                                                                            | 45 |

|    |       | 3.3.3    | Opamp Complete Architecture                                                                                | 48 |

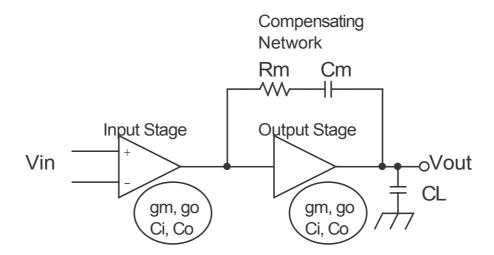

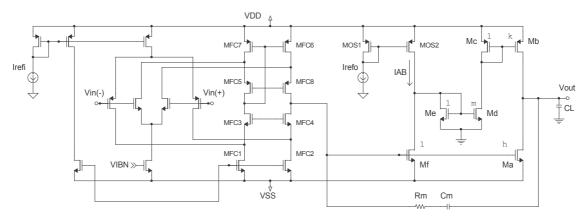

|    | 3.4   | Advan    | aced Design Methodologies                                                                                  | 48 |

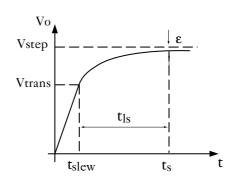

|    |       | 3.4.1    | Power Optimization for a Given Total Settling Time                                                         | 49 |

|    |       | 3.4.2    | Settling Behavior Model                                                                                    | 50 |

|    |       | 3.4.3    | Power Optimization of a Miller OTA                                                                         | 51 |

|    | 3.5   | Conclu   | usions                                                                                                     | 53 |

| 4. | Hiera | archical | Automated Synthesis                                                                                        | 55 |

|    | 4.1   | Introd   | uction                                                                                                     | 55 |

|    | 4.2   | Miller   | ${\bf Compensation} \ {\bf Capacitance} \ {\bf for} \ {\bf Minimum} \ {\bf Power} \ {\bf Consumption} \ .$ | 55 |

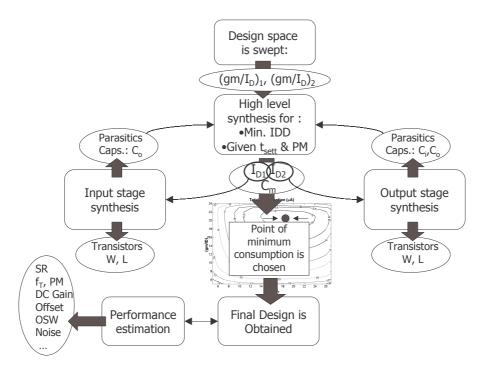

|    | 4.3   | Synthe   | esis Algorithm                                                                                             | 56 |

|    |       | 4.3.1    | High Level Synthesis                                                                                       | 58 |

|    |       | 4.3.2    | Input Stage Synthesis                                                                                      | 61 |

|    |       | 4.3.3    | Output Stage Synthesis                                                                                     | 65 |

|    | 4.4   | Synthe   | esis Results                                                                                               | 69 |

|    |       | 4.4.1    | $1\mu s$ Settling Time Design                                                                              | 70 |

|    |       | 4.4.2    | Opamp Performance Tuning                                                                                   | 75 |

|    |       | 4.4.3    | Synthesized vs. Tuned                                                                                      | 78 |

|    |       | 4.4.4    | Performance Evaluation Against a Simpler Architecture                                                      | 78 |

|    | 4.5   | Analys   | sis of the Constant-gm Circuit                                                                             | 79 |

|    |       | 4.5.1    | Open Loop Transfer                                                                                         | 80 |

|    |       | 4.5.2    | Bias Current Monitor                                                                                       | 82 |

|    |       | 4.5.3    | Redesign of the Constant-gm Circuit                                                                        | 83 |

|    | 4.6   | Conclu   | usions                                                                                                     | 84 |

| 5. | Expe  | eriment  | al Results                                                                                                 | 85 |

|    | 5.1   | Rail-to  | o-rail Operational Amplifier in $0.8 \mu m$ CMOS Technology                                                | 85 |

|    | 5.2   | Compa    | arison with other published results                                                                        | 90 |

|    | 5.3   | Concli   | usions                                                                                                     | 92 |

| 6.  | Conclusions                                       | 93  |

|-----|---------------------------------------------------|-----|

| A.  | Low-Voltage Cascode Bias Transistor Design        | 97  |

| В.  | Size of Transistors in the Experimental Prototype | 99  |

| Bil | bliography                                        | .01 |

# List of Figures

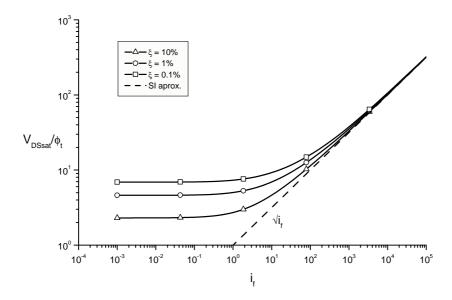

| 2.1  | Normalized $V_{DSsat}$ for several values of $\xi$ and the SI approximation                         | 8  |

|------|-----------------------------------------------------------------------------------------------------|----|

|      |                                                                                                     |    |

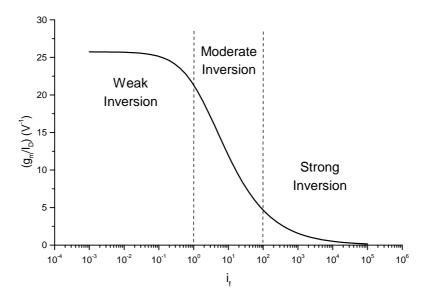

| 2.2  | $(g_m/I_D)$ ratio as a function of the inversion factor $i_f$                                       | 11 |

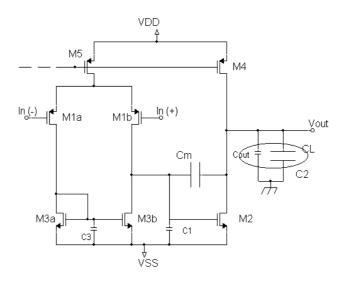

| 2.3  | Miller Amplifier, including parasitics capacitances                                                 | 13 |

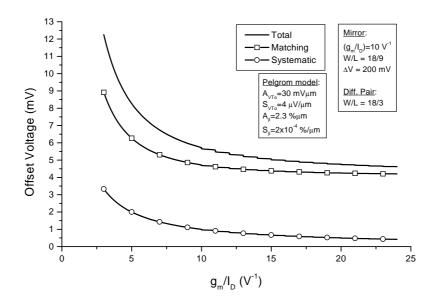

| 2.4  | Offset voltage as a function of $(g_m/I_D)$                                                         | 16 |

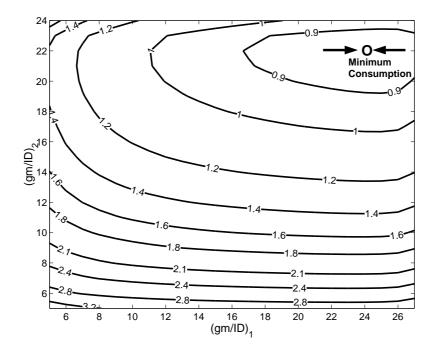

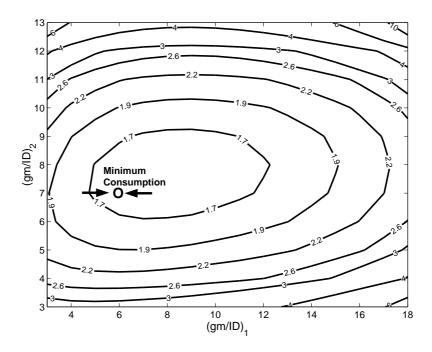

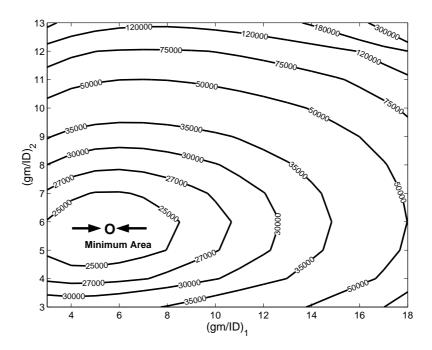

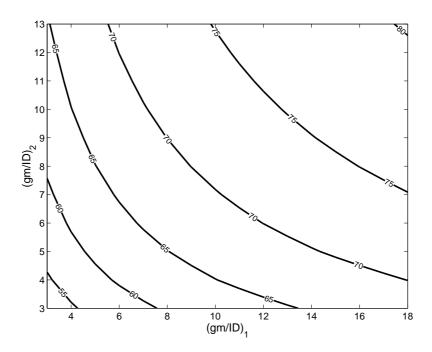

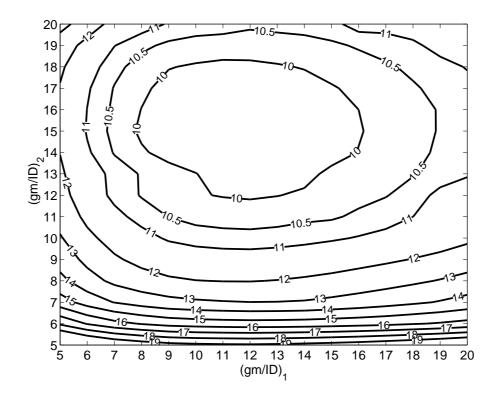

| 2.5  | Design space exploration: Total consumption (in $\mu A$ ) of the 100kHz Miller Amplifier            | 20 |

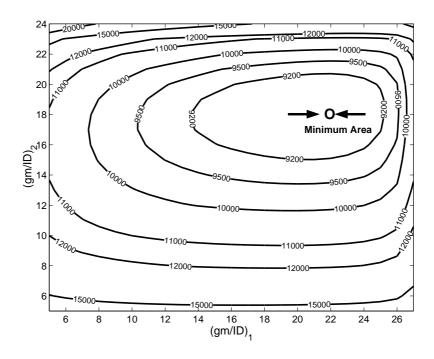

| 2.6  | Design space exploration: Die area estimation (in $\mu m^2$ ) of the 100kHz Miller Amplifier        | 21 |

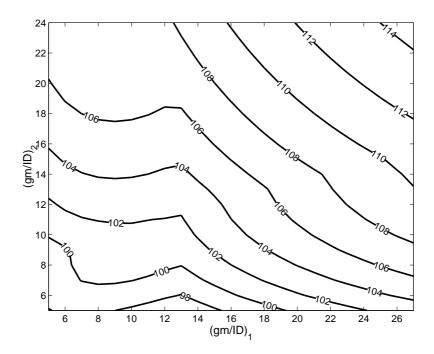

| 2.7  | Design space exploration: DC Gain (in $dB$ ) of the 100kHz Miller Amplifier                         | 21 |

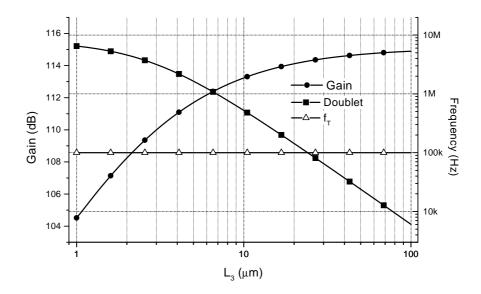

| 2.8  | Gain and doublet frequency dependence on the length of M3                                           | 23 |

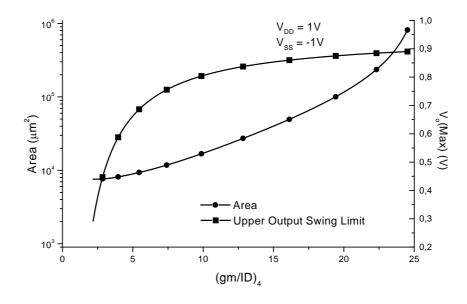

| 2.9  | Output swing and total area dependence on $(g_m/I_D)_4$ ratio                                       | 23 |

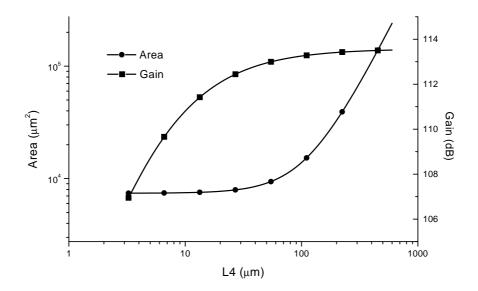

| 2.10 | Gain and total area dependence on the length of M4                                                  | 24 |

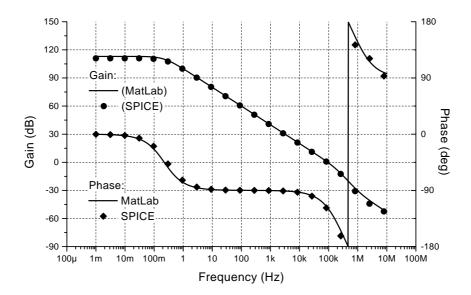

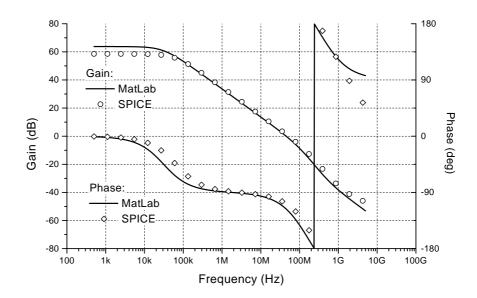

| 2.11 | Frequency response of the 100kHz Miller Amplifier                                                   | 26 |

| 2.12 | Design space exploration: Total consumption (in $mA$ ) of the 50MHz Miller Amplifier                | 27 |

| 2.13 | Design space exploration: Die area estimation (in $\mu m^2$ ) of the 50MHz Miller Amplifier         | 27 |

| 2.14 | Design space exploration: Total gain (in $dB$ ) of the 50MHz Miller Amplifier                       | 28 |

| 2.15 | Frequency response of the 50MHz Miller Amplifier                                                    | 29 |

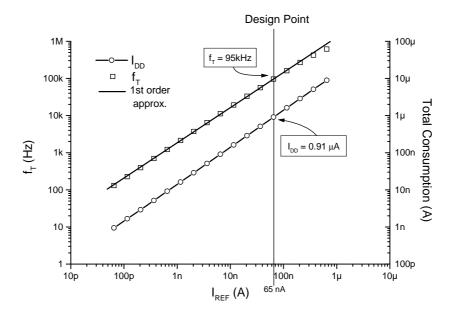

| 3.1  | Gain-Bandwidth product tuning of the Miller amplifier from section 2.4.4                            | 33 |

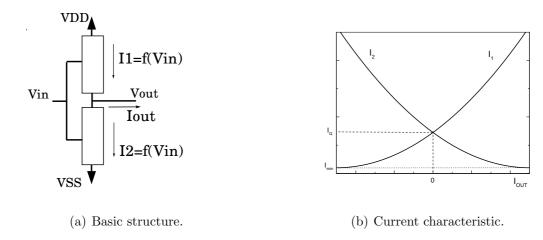

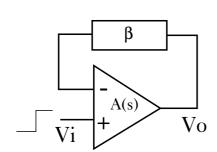

| 3.2  | General characteristic of the class AB stage                                                        | 38 |

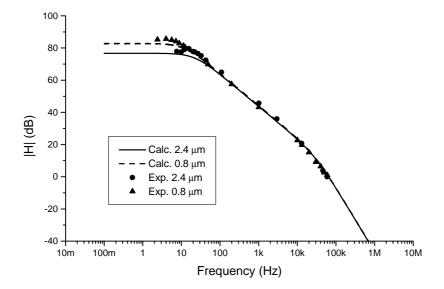

| 3.3  | Open loop frequency response comparison in technology migration                                     | 40 |

| 3.4  | Basic rail-to-rail differential pair architecture                                                   | 41 |

| 3.5  | Transconductance as a function of the input common mode voltage, using architecture from Figure 3.4 | 42 |

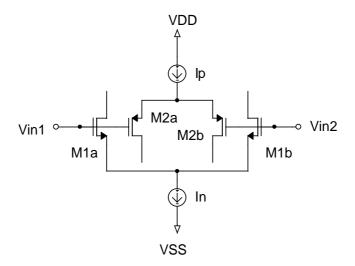

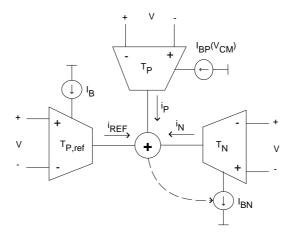

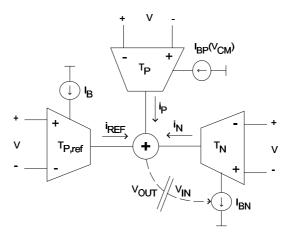

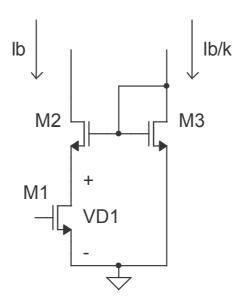

| 3.6  | Schematic view of the constant gm operation principle                                                                   | 43 |

|------|-------------------------------------------------------------------------------------------------------------------------|----|

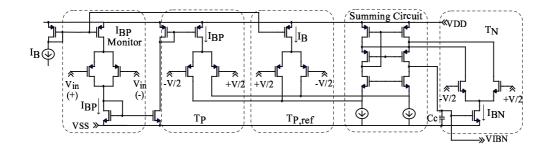

| 3.7  | Implementation of the constant gm technique                                                                             | 44 |

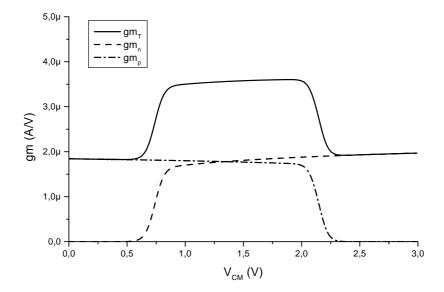

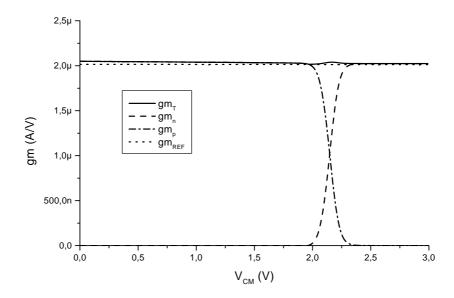

| 3.8  | Transconductance as a function of the input common mode voltage using constant gm technique                             | 45 |

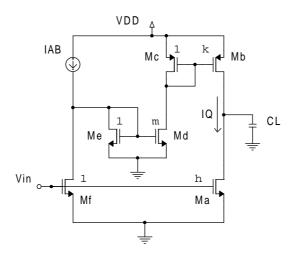

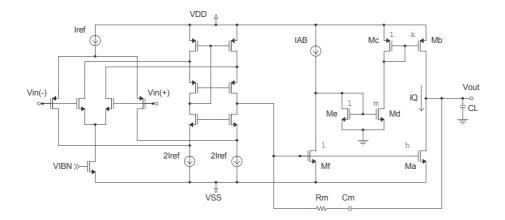

| 3.9  | Class AB output stage                                                                                                   | 46 |

| 3.10 | Amplifier circuit implementation, omitting constant-gm circuit                                                          | 48 |

| 3.11 | Settling time model and step response plot                                                                              | 50 |

| 4.1  | High Level Schematic of the Amplifier                                                                                   | 57 |

| 4.2  | Complete Amplifier Synthesis Algorithm Scheme. $t_{sett}$ is total settling time and $IDD$ is total current consumption | 58 |

| 4.3  | Folded Cascode Circuit                                                                                                  | 63 |

| 4.4  | Class AB output stage                                                                                                   | 65 |

| 4.5  | Opamp cell, omitting constant-gm circuitry                                                                              | 69 |

| 4.6  | Total Consumption (in $\mu A$ ) for a $1\mu sec$ total settling time rail-to-rail OTA                                   | 70 |

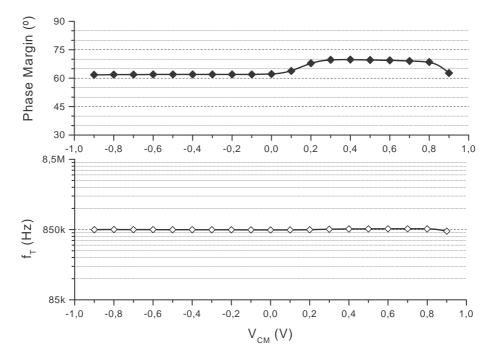

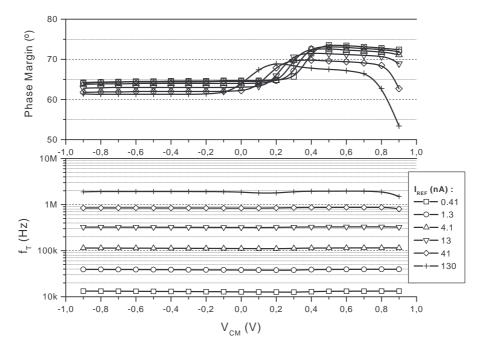

| 4.7  | Transition frequency and Phase Margin along the input common mode range                                                 | 73 |

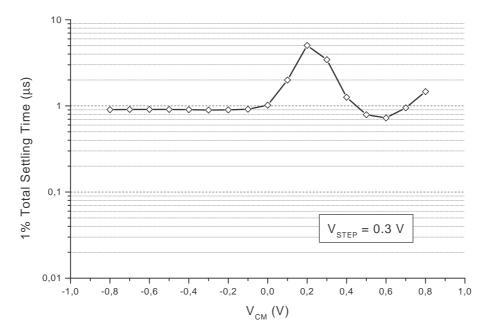

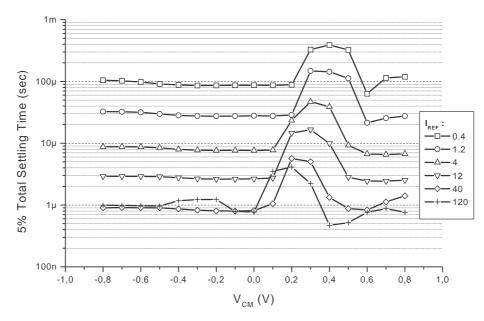

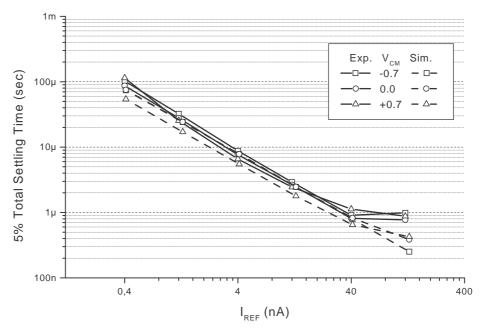

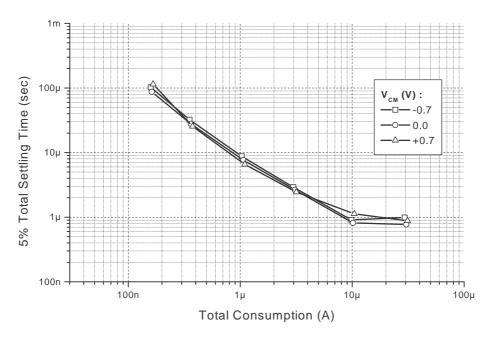

| 4.8  | Total Settling Time for different input common mode range                                                               | 74 |

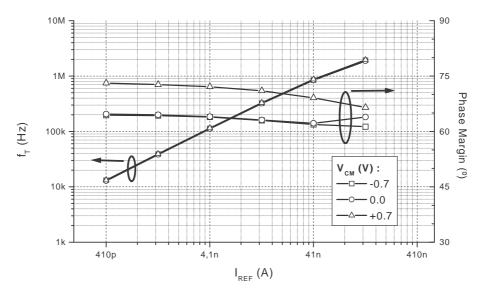

| 4.9  | Transition frequency $(f_T)$ and Phase Margin tuning over more than 3 decades                                           | 75 |

| 4.10 | Transition frequency and phase margin tuning as a function of the input common mode                                     | 76 |

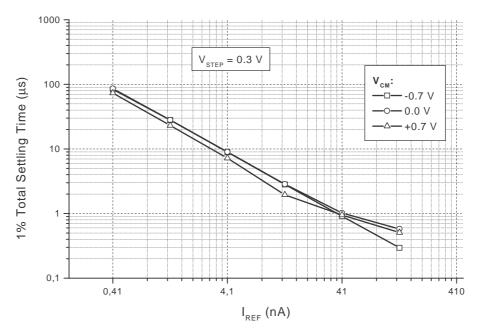

| 4.11 | Total Settling Time tuning for three different input common modes                                                       | 77 |

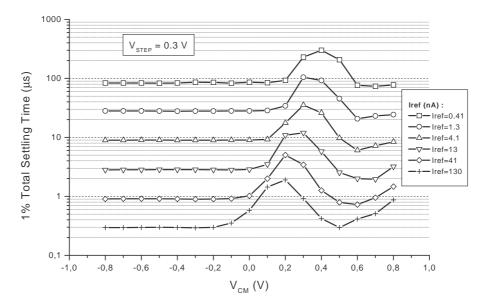

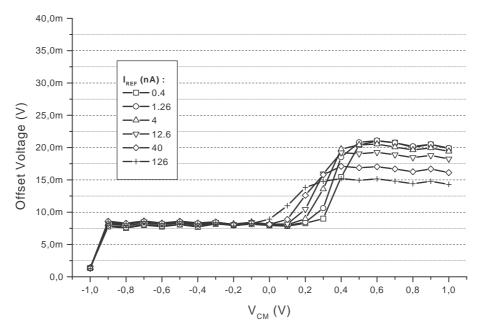

| 4.12 | Total Settling Time tuning as a function of the input common mode range                                                 | 78 |

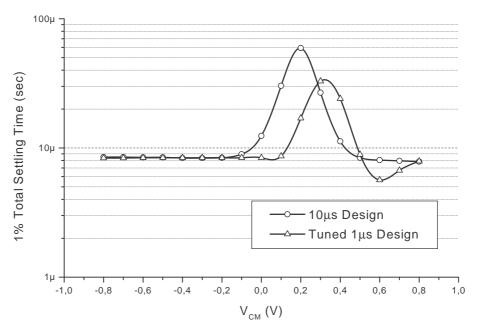

| 4.13 | Total Settling Time comparison between the $10\mu s$ design and the tuned $1\mu s$ design                               | 79 |

| 4.14 | Constant-gm circuit loop                                                                                                | 81 |

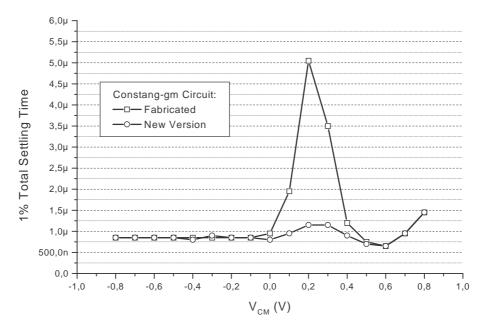

| 4.15 | Settling time as a function of the input common mode with the redesign of the constant-gm circuit                       | 83 |

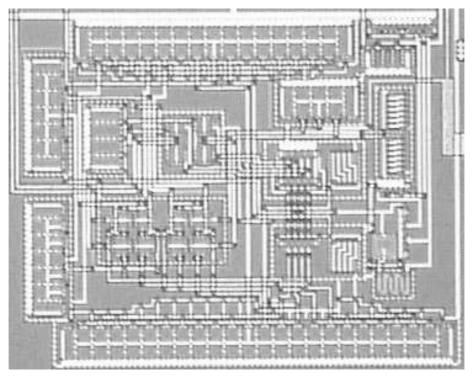

| 5.1 | Opamp Cell Microphotograph                                                                                          | 85 |

|-----|---------------------------------------------------------------------------------------------------------------------|----|

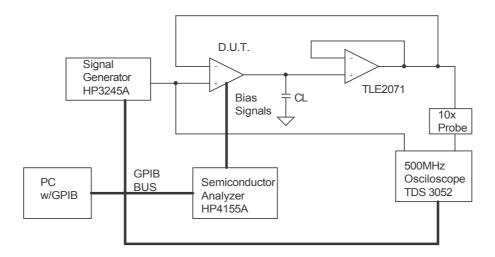

| 5.2 | Settling time automatic measurement system                                                                          | 86 |

| 5.3 | Total settling time tuning as a function of the input common mode range                                             | 87 |

| 5.4 | Comparison between the simulated and experimental total settling time tuning for three different input common modes | 87 |

| 5.5 | Settling time as a function of the total quiescent current consumption                                              | 88 |

| 5.6 | Offset voltage as a function of the input common mode                                                               | 90 |

| A.1 | Cascode transistor bias                                                                                             | 97 |

## List of Tables

| 2.1 | Specifications for a Micropower 100kHz Miller Amplifier                                     | 20 |

|-----|---------------------------------------------------------------------------------------------|----|

| 2.2 | Final design for a 100kHz Miller amplifier                                                  |    |

|     |                                                                                             |    |

| 2.3 | Specifications for a 50MHz Miller Amplifier                                                 | 25 |

| 2.4 | Final design for a 50MHz Miller amplifier                                                   | 28 |

| 3.1 | Tuning of the Miller amplifier introduced on section 2.4.4                                  | 36 |

| 4.1 | Automatic Synthesis Result with Algorithm 4.1                                               | 71 |

| 4.2 | Transistors Sizes Obtained Using Algorithm 4.1                                              | 72 |

| 4.3 | Calculated and simulated characteristics of the OTA with $1\mu sec$ total settling time     | 73 |

| 4.4 | Comparison between the $10\mu s$ design and the tuned $1\mu s$ design                       | 80 |

| 4.5 | Comparison between our amplifier and a simple Miller amplifier designed using Algorithm 3.1 | 80 |

| 5.1 | Opamp Cell characteristics                                                                  | 89 |

| 5.2 | Comparison of the performance of the Opamp Cell                                             | 91 |

| B.1 | Transistors sizes in the experimental prototype                                             | 99 |

## List of Algorithms

| 2.1 | Gain-Bandwidth Driven Automatic Synthesis          | 18 |

|-----|----------------------------------------------------|----|

| 2.2 | Power Optimization Automatic Synthesis             | 19 |

| 3.1 | Power Optimization for a Given Total Settling Time | 54 |

| 4.1 | High Level Synthesis                               | 62 |

| 4.2 | Input Stage Synthesis                              | 65 |

| 4.3 | Output Stage Synthesis                             | 69 |

### Agradecimientos

Si bien esta tesis fue realizada en su totalidad en Uruguay, donde el español es la única lengua oficial, decidimos escribirla en inglés para darle a la misma mayor posibilidad de difusión, ya que como dijo el Prof. Gabor Temes en una conferencia en la que tuve el gusto de escucharlo "The language of scientific research is accented english". Podrá sorprender, entonces, que estas líneas estén escritas en español, pero lo cierto es que todas las personas a las que quiero agradecer tienen la suerte de tener al idioma español por lengua madre, por lo que no veo la razón para agradecerles en otro idioma.

Esta tesis es el resultado del apoyo y el esfuerzo de diversas personas a las que estoy profundamente agradecido.

Mi tutor, Fernando Silveira, ha sido una sólida y fundamental guía en este trabajo. Fernando ha sido quien, a lo largo de estos años, me ha brindado desde su ya amplia experiencia en la investigación científica lo mejor de sí para formarme como investigador en el área de la microelectrónica. De hecho, también fue él quien me formó en los principios básicos de la electrónica en los cursos de grado hace ya 4 años y en los cuales ahora tengo el gusto de desempeñarme como uno de sus ayudantes. A lo largo de estos años y hasta el día de hoy, Fernando siempre esta dispuesto a discutir y solucionar mis mas variadas inquietudes, con su habitual optimismo y a pesar de sus innumerables tareas y obligaciones dentro y fuera de la facultad. Por todo esto y mucho más, que probablemente no queda reflejado en este corto párrafo, estoy sumamente agradecido.

También estoy sumamente agradecido con Alfredo Arnaud, quien por un formalismo administrativo no puede figurar como el co-tutor que fue de esta tesis. Alfredo ha sido fundamental para este trabajo y en general en mi formación en la microelectrónica. Fue él quien me guió en mi primer trabajo en el área y desde entonces y a lo largo de esta maestría nunca ha dudado en apoyarme y asistirme mientras llevaba a cabo exitosamente su propia tesis de doctorado.

Conrado Rossi, con quien compartimos la oficina, ha sido desde que entré en el IIE mi referencia en todo lo que es el funcionamiento del grupo y del propio instituto. Conrado, si bien no participó directamente de este trabajo, siempre estuvo dispuesto a interesarse en el tema y discutir mis dudas, y en los últimos meses me liberó de diversas responsabilidades en el proyecto que él dirige y en el que me desempeño como ayudante, para que pudiera terminar esta tesis en tiempo y forma.

En ellos, junto al resto del grupo de Microelectrónica: Leonardo Barboni, Rafaella Fiorelli, Pablo Mazzara y Linder Reyes, encontré un excelente grupo de trabajo con el que me siento sumamente a gusto y con cuyos integrantes estoy muy agradecido. Aquí también quiero agradecer a Raúl Acosta, quien trabajó en el tema de migración de tecnología y obtuvo los resultados experimentales que se muestran en la sección 3.2.3. También estoy muy agradecido al Instituto de Ingeniería

Eléctrica (IIE), a su director, Gregory Randall, y al jefe de mi departamento, Rafael Canetti.

Debo también agradecer a la Comisión Académica de Posgrados (CAP) de la Facultad de Ingeniería por la beca de apoyo que me asignaron durante estos casi dos años de trabajo y que me permitió dedicarme exclusivamente a mi maestría y a mi trabajo docente en el IIE.

Quiero agradecer también a los Profesores Carlos Galup-Montoro y José Silva Martinez que aceptaron participar de mi tribunal de tesis. Es un verdadero honor para mi contar con la evaluación de dos reconocidos profesores del más alto nivel internacional.

También quiero agradecer a la Dra. Adoración Rueda y a la gente del CNM de Sevilla, España, por recibirme y facilitarme los recursos necesarios para realizar una estancia de investigación de tres meses durante el año 2003. Mis tareas en el CNM, si bien no tienen relación directa con el trabajo de esta tesis, fueron un aporte importantísimo a mi formación en esta maestría.

Para terminar quiero agradecer a mi familia y amigos. A mis padres que desde el principio me formaron para dar lo mejor en lo que me propusiera hacer. A mi madre, que es la principal razón para que esta tesis se haya podido escribir en un nivel aceptable de inglés, y a mi padre, que desde que tengo memoria apoyó e incentivó mi fascinación por las ciencias. A mis hermanos Diego y Fernando, que junto a mis padres, han soportado mis mal humores y que desaparezca de mi casa durante largos períodos de tiempo, otra vez. A Patricia, Choché, Juan Pablo y Agustín quienes desde hace 5 años me hacen sentir parte de la familia. A mis amigos, Ale, Cris, Javo, Jorge, Juan, Leo, Martín, Nacho y Pucho, que siempre me apoyaron y estuvieron más que dispuestos a ir a comer unos lehmeyuns y tomar una(s) cerveza(s) después de un largo día de trabajo.

Por último y muy especialmente, a Virigina, quien desde hace ya más de 5 años me apoya incondicionalmente y hace lo imposible por entender qué es exactamente a lo que se dedica su novio.

#### Resumen

Esta tesis trata sobre el estudio y desarrollo de un algoritmo automático de síntesis para amplificadores operacionales de microconsumo. Los objetivos principales de este trabajo son el estudio de las metodologías existentes de diseño analógico para consumo mínimo y su aplicación en el diseño automático de un amplificador operacional reutilizable de microconsumo con etapas de entrada y salida "rail-to-rail". Por lo tanto, se seguirán dos líneas de investigación en este trabajo. Primero, el desarrollo de un nuevo enfoque jerárquico en algoritmos de síntesis automática, que permite desacoplar la síntesis de cada etapa del amplificador del algoritmo de síntesis principal. Segundo, una revisión y la aplicación de técnicas de reutilización de circuitos analógicos, particularmente en arquitecturas de amplificadores, migración de tecnología y especialmente en la técnica de sintonización del compromiso entre velocidad y consumo utilizando la corriente de polarización.

En esta tesis, utilizando la metodología  $(gm/I_D)$  [1], nos enfocaremos exclusivamente en la obtención de diseños con óptimo consumo de corriente, siguiendo así con la línea de investigación del Grupo de Microelectrónica del IIE.

El punto de partida para el repaso de las metodologías de diseño avanzadas, es un algoritmo simple de diseño automático para un amplificador Miller [2] basado en el producto ganancia por ancho de banda. Este repaso progresa hasta el algoritmo de síntesis automática desarrollado por Silveira [3], con el cual a partir de especificaciones de alto nivel (tiempo total de establecimiento) se puede sistemáticamente obtener las especificaciones del amplificador (producto ganancia por ancho de banda, slew rate) y el tamaño de los transistores. El diseño que se obtiene, cumple con las especificaciones con consumo mínimo. Desde este punto, desarrollamos un algoritmo jerárquico para arquitecturas más complejas que incluyen etapas de entrada "railto-rail" y una etapa de salida clase AB. Este enfoque jerárquico permite separar el algoritmo de síntesis de cada etapa del algoritmo de síntesis de alto nivel que está basado en el algoritmo presentado por Silveira [3].

La elección de las arquitecturas de cada etapa no es arbitraria y está sumergida en el contexto de la segunda línea de investigación de este trabajo: la reutilización de diseños analógicos. En esta linea se investigan dos enfoques. Primero, se estudian arquitecturas para etapas de entrada y salida que son factibles de ser utilizadas en diferentes condiciones de operación, lo que nos permite obtener una celda que puede ser utilizada en un amplio espectro de aplicaciones para baja tensión de alimentación y microconsumo. El segundo enfoque que se investiga, se centra en la posibilidad de sintonizar la performance del circuito mediante la corriente de polarización. La idea es sintonizar el compromiso entre velocidad y consumo del amplificador mientras se mantiene la performance en el resto de los aspectos. Esta no es una idea nueva y ya ha sido implementada con éxito en una aplicación comercial [4]. Sin embargo, hasta

<sup>&</sup>lt;sup>1</sup>Que permiten señales en cualquier nivel de tensión entre las fuentes de alimentación.

donde sabemos, esto solo ha sido realizado en tecnología bipolar, y por lo tanto nos proponemos realizar la primera experiencia exitosa de esta teoría utilizando tecnología CMOS estándar.

En definitiva, el objetivo final de esta tesis fue diseñar, utilizando un algoritmo automático de síntesis, una celda de un amplificador operacional reutilizable, que cumpla con las especificaciones de alto nivel con mínimo consumo.

Los resultados obtenidos, tanto en simulaciones como en las medidas experimentales del prototipo, muestran que el algoritmo de síntesis desarrollado obtiene un diseño que cumple exitosamente con las especificaciones para el tiempo de establecimiento.

Para comparar la eficiencia del amplificador se utilizaron figuras de mérito usuales para medir la performance en términos del compromiso entre velocidad y consumo. Se comparó contra otros resultados publicados en la literatura [3,5–8] y se muestra que la performance del amplificador es superior a todos ellos, lo que permite afirmar que efectivamente se logró optimizar el consumo del amplificador.

El consumo total para el diseño con  $1\mu s$  de tiempo total de establecimiento es de  $10.3\mu A$  con una tensión de alimentación de sólo 2V ( $20.6\mu W$ ). La sintonización del punto de operación también se comprobó exitosamente, pudiéndose sintonizar el mismo por más de 3 décadas de tiempo de establecimiento, con consumos que llegan a 160nA para el amplificador con  $100\mu s$  de tiempo de establecimiento y que puede ser llevado a amplificadores más lentos pero con consumos aún menores.

#### Abstract

This thesis deals with the study and development of an automatic synthesis algorithm for micropower operational amplifiers. The main objectives of this work are the study of the existent power oriented methodologies for analog design and its application in the automatic design of a reusable rail-to-rail input/output micropower operational amplifier cell. Thus, two main lines of research will be attacked in this work. First, the development of a new hierarchical approach in automatic synthesis algorithms to decouple the synthesis algorithm of each stage of the amplifier from the main synthesis algorithm. Second, the review and application of analog reuse techniques, regarding opamp architectures, technology migration, but specially speed-power trade-off tuning through bias current.

In this thesis, we will follow the line of research of our group and focus exclusively in the obtention of optimum power designs, using the  $(g_m/I_D)$  methodology [1].

The introduction of a simple, gain-bandwidth driven, automatic design algorithm for a Miller amplifier [2] is used as a starting point for the review of more advanced design methodologies. This review leads to an automatic synthesis algorithm developed by Silveira [3] which systematically transits from high level specifications (total settling time) to the amplifier specifications (gain-bandwidth, slew rate) and then to transistor sizing. The design obtained complies with the high level specifications with minimum power consumption. We took on from this point into the development of a hierarchical algorithm for more complex architectures that include rail-to-rail input stages and a power efficient class AB output stage. The hierarchical approach allows to decouple the synthesis algorithm of each stage from the high level synthesis algorithm based on the algorithm presented by Silveira [3].

The selection of the architectures of each stage is not arbitrary, but is based on the second line of research of this work: analog design reuse. Two main lines of study are followed here. The study of architectures for input and output stages that are suitable to be used on different environmental conditions, allow us to obtain an opamp cell that can be used in an ample spectrum of low-voltage, micropower applications. The second line of study in analog design reuse focuses on the possibility of circuit performance tuning through the bias current, where preliminary results have already been obtained [9]. The idea in this technique is to tune the power-speed trade off of the opamp cell using the bias current while keeping the performance in all other aspects. This idea is not new, and has already been used in a industrial application [4], but to the best of our knowledge, it has only been done in bipolar technology. Therefore, we intend to make the first experimental test of this theory in standard CMOS technology.

The final objective pursued in this thesis, then, is the successful design and implementation, using an automatic synthesis algorithm, of a reusable opamp cell that complies with the high level specifications with optimum power consumption.

The results show, both in simulations and experimental measurements, that

the synthesized design using the algorithm developed in this work, successfully complies with the settling time specifications.

To compare the efficiency of the amplifier, we used the usual figures of merit to measure the trade-off between speed and power consumption. We achieved superior performance against several other published results [3, 5–8], which shows that the amplifier presents optimum consumption.

Total current consumption on the  $1\mu s$  total settling time design is  $10.3\mu A$  with a supply voltage of only 2V ( $20.6\mu W$ ). Performance tuning was also successfully verified. The cell can be tuned over more than 3 decades of settling time, including consumptions that reach 160nA for a  $100\mu s$  settling time, and beyond.

# Chapter 1 Introduction

This thesis deals with the study and development of an automatic synthesis algorithm for micropower operational amplifiers. The main objectives of this work are the study of the existent power oriented methodologies for analog design and its application in the automatic design of a reusable rail-to-rail input/output micropower operational amplifier cell. Thus, two main lines of research will be attacked in this work. First, the development of a new hierarchical approach in automatic synthesis algorithms to decouple the synthesis algorithm of each stage of the amplifier from the main synthesis algorithm. Second, the review and application of analog reuse techniques, regarding opamp architectures, technology migration, but specially speed-power trade-off tuning through bias current.

The  $(g_m/I_D)$  methodology [1], developed in the Université Catholique de Louvain (UCL), provides a powerful tool for automatic design methodologies, as it allows the designer to systematically explore the design space and obtain an optimum combination of the design variables in a given sense. In this thesis, we will follow the line of research of our group and focus exclusively in the obtention of optimum power designs. Nevertheless, the methods and techniques applied here are general and can be applied to optimize any other aspect of the design.

We begin with the review of the MOSFET model used in this work. The ACM [10,11] model presents simple, single piece, continuous expressions and has many advantages regarding analog design. Specially, the fact that every equation is a function of the inversion level and a few physical-based parameters, makes this model ideal to be used in automatic synthesis algorithms.

The introduction of a simple, gain-bandwidth driven, automatic design algorithm for a Miller amplifier [2] is used as a starting point for the review of more advanced design methodologies. This review leads to an automatic synthesis algorithm developed by Silveira [3] which systematically transits from high level specifications (total settling time) to the amplifier specifications (gain-bandwidth, slew rate) and then to transistor sizing. The design obtained complies with the high level specifications with minimum power consumption. We took on from this point into the development of a hierarchical algorithm for more complex architectures that include rail-to-rail input stages and a power efficient class AB output stage. The hierarchical approach allows to decouple the synthesis algorithm of each stage from the high level synthesis algorithm based on the algorithm presented by Silveira [3].

The selection of the architectures of each stage is not arbitrary, but is based on the second line of research of this work. Analog design reuse has become an essential tool to bridge the gap between circuits complexity and the ever shrinking time-to-market. The urge for implementing reuse capabilities is particularly intense in the analog field [12], since automatic synthesis of analog circuits is a much hard

problem than for the digital counterparts. Not only there are more aspects of the problem to take into account besides consumption, speed and area, but also analog block design is very layout and process dependent and special skills are required to complete them. Hence, analog automatic synthesis is much less developed than digital synthesis, further increasing the demands for experienced designer time in the analog field.

Two main lines of study are followed in analog design reuse. The study of architectures for input and output stages that are suitable to be used on different environmental conditions, allow us to obtain an opamp cell that can be used in different applications. The most important characteristics of rail-to-rail input stages towards reusability are presented together with a new approach presented by Silveira [3] for a power efficient class AB output stage that takes advantage of a transconductance multiplication effect. The complete amplifier architecture obtained, conforms an opamp cell suitable to be used in an ample spectra of low-voltage, micropower applications. The second line of study in analog design reuse focuses on the possibility of circuit performance tuning through the bias current, where preliminary results have already been obtained [9]. The idea in this technique is to tune the power-speed trade off of the opamp cell using the bias current while keeping the performance in all other aspects. This idea is not new, and has already been used in an industrial application [4], but to the best of our knowledge, it has only been done in bipolar technology. Therefore, we intend to make the first experimental test of this theory in standard CMOS technology.

The final objective pursued in this thesis, then, is the successful design and implementation, using an automatic synthesis algorithm, of a reusable opamp cell that complies with the high level specifications with optimum power consumption.

Next we will outline the contents of each chapter,

- Chapter 1: Introduction This chapter, where an introduction with the backgrounds, motivations and objectives of this thesis are presented.

- Chapter 2: Design Methodologies The second chapter introduces the reader with the basic automatic design methodologies and synthesis algorithms. It begins with a review of the MOSFET model used in this work which presents major advantages for analog design. Then the  $(g_m/I_D)$  methodology, which is a keystone in all the algorithms presented and developed in this work, is introduced and explained. On the third part of the chapter, the design of a simple Miller compensated amplifier is presented. First, the characteristic equations for frequency response, offset, dynamic range and parasitic capacitances are presented. Then the basic gain-bandwidth driven algorithm and the design space exploration algorithm for power optimization are presented and explained in two design examples for  $f_T = 100kHz$  and  $f_T = 50MHz$ .

- Chapter 3: Low-Power OpAmp Cells: Reuse, Architecture and Synthesis The third chapter of this thesis presents the theory and actual state of know-ledge in analog reuse and advanced automatic synthesis algorithms for reu-

1. Introduction 3

sable low-power operational amplifier cells. The chapter is divided in three sections. First, we present the theory and some examples of analog design reuse, including performance tuning through bias current, architectures suited for different environmental conditions and technology migration. Second, the selected opamp architecture for the opamp cell is presented. And third, the power optimization algorithm for a given total settling time developed by Silveira [3] is presented as an example of state of the art automatic synthesis algorithm.

Chapter 4: Hierarchical Automated Synthesis The fourth chapter presents the development of the hierarchical automated synthesis algorithm and its application to the design of a  $1\mu s$  total settling time amplifier using the architecture seen on the previous chapter. First, a new expression for directly estimate the Miller compensation capacitance for optimum consumption is presented. This expression is used in the following section in the development of the high level synthesis algorithm, and saves large amounts of processing time. Then, we present the hierarchical approach for the automatic synthesis algorithm, along with the synthesis algorithms for the input and output stages. Finally, we present the simulations of the synthesized cell, including the tuning of the cell over several decades of total settling time.

Chapter 5: Experimental Results The last chapter presents the results obtained from the measurements of the prototype fabricated in a  $0.8\mu m$  standard CMOS process. The performance of the opamp cell is characterized and the reusability of the cell over several decades of total settling time is successfully verified. The usual figures of merit used to measure the power-speed efficiency in amplifiers are used to compare the performance of our cell with several other amplifiers from the literature and excellent results are obtained, proving the true power optimization achieved by the algorithm.

Chapter 6: Conclusions Conclusions and ideas for future research are presented.

# Chapter 2 Design Methodologies

#### 2.1 Introduction

This chapter introduces the basic concepts and ideas that will be used to develop the automatic design algorithms presented on Chapter 3. The chapter begins by introducing the MOSFET model used in this work. By doing so, we introduce the reader with the notation and basic design equations that will be used through out this work.

The development of an automatic synthesis algorithm for two-stage Miller amplifiers, allow us to explain in a simple architecture amplifier the design space exploration using the  $(g_m/I_D)$  methodology [1], which is the main idea behind the synthesis automation for optimum design. The core of the Miller amplifier synthesis algorithm is a gain-bandwidth product driven algorithm presented by Jespers [2].

Section 2.2 briefly reviews the MOSFET model presented by Cunha, Galup-Montoro and Schneider [10, 11]. On section 2.3, the  $(g_m/I_D)$  based methodology will be introduced before entering section 2.4 where the synthesis algorithms for Miller amplifiers is presented. In this section, the Miller amplifier is analyzed and the algorithm driven by the gain-bandwidth product and the algorithm for design space exploration are presented. Also, two design examples are introduced to show the performance of the algorithms.

Finally conclusions are presented on section 2.5.

### 2.2 A Current-Based MOSFET Model for IC Design

The need for an accurate MOSFET model that provides simple expressions is critical in the development of analog design methodologies. In this work we will use the model presented by Galup-Montoro *et al.* [10,11]. This model meets several desirable requirements from the designer point of view. Among them we would like to highlight that

- The model is single piece, continuous and presents simple accurate expressions. Particularly it correctly represents all the regions of operation, from weak inversion to strong inversion, including moderate inversion.

- The model conserves charge.

- The model has a minimum set of parameters, all physically based.

The main approximation of this model, referred as the ACM model from herein, is to consider the depletion and inversion charge densities,  $Q_B'$  and  $Q_I'$ , to be linear functions of the surface potential of the channel  $\phi_S$  for a constant gate-to-bulk

voltage. As a consequence, the MOSFET drain current and charges are expressed as very simple functions of two components of drain current, namely, the forward and reverse saturation currents. A very simple relation between these two components of the drain current and the applied voltages is obtained.

One of the fundamental parameters in the MOSFET model is defined as the inverse of the slope of the curve  $\phi_{Sa}$  versus  $V_G$ , where  $\phi_{Sa}$  is the surface potential for which  $Q'_I = 0$ . This parameter is known as the *slope factor* and is written as

$$n = 1 + \frac{\gamma}{2\sqrt{\phi_{Sa}}} \tag{2.1}$$

where  $\gamma$  is the body effect factor. The *slope factor* is slightly dependent on the gate voltage, but it can be assumed constant for hand calculations and usually  $n = 1, 2, \dots, 1.6$  for bulk technology.

#### 2.2.1 Current - Voltage Relationships

Let us now resume the main expressions of the ACM model, as they will be used throughout this work. The pinch-off voltage, defined as the channel voltage for which the inversion charge density equals  $-\gamma C'_{ox}\phi_t$  being  $C'_{ox}$  the oxide capacitance per unit area and  $\phi_t$  the thermal voltage, can be approximated as

$$V_P = \frac{V_G - V_{T0}}{n} (2.2)$$

where every voltage is referred to the bulk voltage,  $V_G$  is gate voltage and  $V_{T0}$  is the threshold voltage when source voltage,  $V_S$ , is zero.

The drain current is defined as

$$I_D = I_S(i_f - i_r) \tag{2.3}$$

where  $i_{f(r)}$  is the forward (reverse) normalized current and

$$I_S = \frac{1}{2}\mu n C'_{ox} \phi_t^2 \frac{W}{L} \tag{2.4}$$

is the normalization current, which is four time smaller than the same factor as presented in the EKV model [13]. Here  $\mu$  is the carriers mobility in the channel, and W and L are the channel width and length respectively.

In forward saturation  $i_f \gg i_r$ , so the drain current can be approximated by

$$I_D = I_S i_f = \frac{1}{2} \mu n C'_{ox} \phi_t^2 \frac{W}{L} i_f$$

(2.5)

In the EKV model [13] the forward normalized current  $i_f$  is also referred as the inversion factor since it indicates the inversion level of the MOSFET. As a rule of thumb, values of  $i_f$  greater than 100 characterize strong inversion and values below 1

characterize weak inversion<sup>2</sup>. Values between 1 and 100 indicate moderate inversion.

The relationship between current and voltage in the MOSFET transistor is given by:

$$V_P - V_{S(D)} = \phi_t \left[ \sqrt{1 + i_{f(r)}} - 2 + \ln \left( \sqrt{1 + i_{f(r)}} - 1 \right) \right]$$

(2.6)

where  $V_{S(D)}$  is the source (drain) voltage. Used with equation (2.2), we can estimate from this expression the gate voltage in a forward saturated transistor as a function of the inversion level and the source voltage.

$$V_G = V_{T0} + nV_S + n\phi_t \left[ \sqrt{1 + i_f} - 2 + \ln\left(\sqrt{1 + i_f} - 1\right) \right]$$

(2.7)

Another powerful design equation provided by the ACM model is derived from equation (2.6). The theoretical drain to source saturation voltage,  $V_{DSsat}$ , is defined in equation (2.8) as the value of  $V_{DS}$  for which the ratio  $Q'_{ID}/Q'_{IS} = \xi$ , where  $\xi$  is an arbitrary number much smaller than 1. In this definition,  $1 - \xi$  represents the saturation level of the MOSFET.

$$V_{DSsat} = \phi_t \left[ \ln \left( \frac{1}{\xi} \right) + \sqrt{1 + i_f} - 1 \right]$$

$$\simeq \phi_t \left[ \sqrt{1 + i_f} + 3 \right] for \xi = 1\%$$

(2.8)

It can be noted that  $V_{DSsat}$  is independent of the inversion level in weak inversion while in strong inversion it follows the usual square root approximation, as shown in Figure 2.1.

#### 2.2.2 The $(g_m/I_D)$ Ratio

The  $(g_m/I_D)$  ratio will be a key parameter in the design methodologies presented in this work, as we will see in section 2.3 and through out this work. The ACM model provides a simple expression for the  $(g_m/I_D)$  ratio in a forward saturated MOS transistor as a function of the inversion level.

$$\frac{g_m}{I_D} = \frac{1}{n\phi_t} \frac{2}{\sqrt{1 + i_f} + 1} \tag{2.9}$$

#### 2.2.3 Intrinsic Capacitances

Nine intrinsic capacitances characterize the MOS transistor [14]. Among this nine capacitances,  $C_{GS}$ ,  $C_{GD}$ ,  $C_{GB}$ ,  $C_{BS}$  and  $C_{BD}$  are widely used in AC modelling as they accurately describe charge storage up to moderate frequencies. It can be proved [10] that  $C_{GB} = C_{BG}$  so only three more capacitances should be added to the model to complete the nine capacitances. In the case of ACM model  $C_{SD}$ ,  $C_{DS}$

$<sup>^{2}</sup>$ In EKV model values of  $i_f$  greater than 10 characterize strong inversion and values below 0.1 characterize weak inversion. Since the ratio between the normalization current in EKV and ACM is four, these boundaries would correspond to 0.4 and 40 when using ACM. Nevertheless, for simplicity sake, 1 and 100 are taken.

Figure 2.1: Normalized  $V_{DSsat}$  for several values of  $\xi$  and the strong inversion approximation:  $\sqrt{i_f}$

and  $C_{DG}$  are chosen. The complete expressions for these eight capacitances can be found in reference [10]. Here we will only give a simplified expression for the gate capacitance in the case of a forward saturated transistor with  $V_S = 0$ .

$$C_{GS} = \frac{2}{3}C_{ox}\left(1 - \frac{1}{\sqrt{1+i_f}}\right)\left(1 - \frac{1}{(\sqrt{1+i_f}+1)^2}\right)$$

(2.10)

$$C_{GB} = \frac{n-1}{n}(C_{ox} - C_{GS}) \tag{2.11}$$

$$C_G = C_{GS} + C_{GB}$$

$$= \frac{n-1}{n} C_{ox} \left( 1 - \frac{2}{3} \left( 1 - \frac{1}{\sqrt{1+i_f}} \right) \left( 1 - \frac{1}{(\sqrt{1+i_f}+1)^2} \right) \right)$$

(2.12)

These expressions are valid for every operating region and become very useful design tools.

#### 2.2.4 Noise Model

Noise is considered an internally generated, random, small signal and can be modelled by the addition of noise sources to the noiseless small-signal transistor model [14]. MOSFET noise is usually modelled as a current source between source and drain and can be considered to be composed of thermal (white) noise and flicker noise. Both these noise sources are uncorrelated [14], so the power spectral density

of the total noise will be given by

$$S_i(f) = S_{iw}(f) + S_{if}(f)$$

(2.13)

The classical model for the white noise power spectral density follows [14],

$$S_{iw} = -\frac{4k_B T \mu Q_I}{L^2} \tag{2.14}$$

where  $k_B$  is the Boltzmann constant, T the absolute temperature and  $Q_I$  the total inversion charge. Using the expression for  $Q_I$  in the ACM model, a general expression can be obtained [10,15]

$$S_{iw} = \gamma n k_B T g_m \tag{2.15}$$

where  $\gamma = 2$  in weak inversion operation and  $\gamma = \frac{8}{3} \simeq 2$  in strong inversion.

The other component of noise in equation (2.13) is flicker noise, which is also called "1/f" noise because its power spectral density is nearly proportional to the inverse of the frequency. It is quite well accepted that this behavior is due to the random fluctuation of the number of carriers in the channel caused by trapping and detrapping of carriers in energy states near the  $Si - SiO_2$  interface [14,15]. Arnaud and Galup-Montoro [15] provide an expression for the flicker noise power spectral density in the ACM model

$$S_{if}(f) = \frac{q^2 N_{ot} I_D \mu}{L^2 n C'_{ox}} \ln \left( \frac{n C'_{ox} \phi_t - Q'_{IS}}{n C'_{ox} \phi_t - Q'_{ID}} \right) \frac{1}{f}$$

(2.16)

where  $N_{ot}$  is a technology parameter to be adjusted representing the effective number of traps.

This expression can be further simplified into expressions valid in weak inversion or strong inversion. However, in their work, Arnaud and Galup-Montoro provide a simple expression, valid for any inversion level, for the *corner frequency*. The corner frequency is defined as the frequency where both thermal and flicker noise have the same value.

$$f_c \simeq \frac{1}{2} \frac{g_m}{WLC'_{ox}} \frac{N_{ot}}{N^*} \tag{2.17}$$

Equation (2.17), in which  $N^* = \frac{q}{nC_{ox}\phi_t}$ , can be used to obtain a simple expression to easily estimate the total noise power spectral density for a single transistor [15]

$$S_i = 2nk_B T g_m \left( 1 + \frac{f_c}{f} \right) \tag{2.18}$$

From the designer perspective this is a very powerful tool as it allows to identify the source of the most significant terms of noise in a circuit.

#### 2.2.5 Output Conductance

A complete model for the output conductance, including velocity saturation effects, channel length modulation and drain-induced barrier lowering is included in the ACM model. Nevertheless, we will use the usual and much simpler approximated model, valid for the forward saturated long-channel transistor, using

$$g_0 = \frac{dI_D}{dV_D} = \frac{I_D}{V_A}$$

(2.19)

where  $V_A$  is referred as the Early voltage and supposed proportional to the transistor length.

#### 2.2.6 Non-quasi-static Model and Second Order Effects

So far, long and wide channel MOSFETs have been considered and the model presented is valid for low and medium frequency analysis. The ACM model includes a complete non-quasi static model and a set of equations to take into consideration second order effects, as mobility reduction, velocity saturation and channel length modulation.

#### 2.2.7 Why ACM?

The ACM model presented in this section shows major advantages on MOS transistor analog design. All of which might be summed up on the fact that all the ACM model expressions are functions of the forward normalized current (also known as inversion factor) and a very small set of parameters all physically based.

The fact that we can sweep all the regions of operation with one variable and using simple single piece equations for each transistor characteristic is a mayor advantage in design automation algorithms.

Models widely used as BSIM, use large quantities of parameters, most of which are empirical fitting parameters. These models are fine for computer based simulators but are hardly acceptable for hand made calculations and design algorithms.

The EKV model on the other hand has many of the advantages of ACM model: Inversion factor based, simple expressions, few parameters, etc. However it uses nonphysical interpolating curves to bridge the gap between weak and strong inversion. EKV model, then, does not allow the calculation of the nonreciprocal capacitances and does not conserve charge [11]. Nevertheless most of the algorithms introduced on this work can be easily used with the EKV model.

## 2.3 The $(g_m/I_D)$ Based Methodology for Analog Design

The  $(g_m/I_D)$  based methodology allows an unified synthesis methodology in all regions of operation of the MOS transistor. It provides an alternative, taking full advantage of the moderate inversion region, to obtain reasonable power-speed compromise [1]. This methodology has been widely used since its publication proving its advantages in analog circuits design [10, 11, 16–35]

Figure 2.2:  $(g_m/I_D)$  ratio as a function of the inversion factor  $i_f$  for typical bulk-technology parameters.

The proposed methodology considers the relationship between the transconductance over drain current ratio  $(g_m/I_D)$  and the normalized drain current  $(\frac{I_D}{W/L})$ as a fundamental design tool. This choice of the  $(g_m/I_D)$  ratio is based in the following reasons

- 1. It gives an indication of the device operation region.

- 2. It is strongly related to the performance of analog circuits.

- 3. It provides a tool for calculating the transistor dimensions.

The first reason can be explained using the ACM model. Equation (2.9) shows an univocal relationship between the inversion factor  $i_f$  and the  $(g_m/I_D)$  ratio. This relationship can be seen in Figure 2.2 where the three regions, strong, moderate and weak inversion, are shown.

The relationship between  $(g_m/I_D)$  ratio and the power efficiency can be seen in an "intrinsic gain-stage" example, where both gain and transition frequency are linear functions of the transconductance

$$A_0 = -\frac{g_m}{I_D} V_A \tag{2.20}$$

$$A_{0} = -\frac{g_{m}}{I_{D}} V_{A}$$

$$f_{T} = \frac{1}{2\pi} \frac{g_{m}}{C_{L}}$$

(2.20)

where  $V_A$  is the Early voltage of the transistor and  $C_L$  is the load capacitance of the stage. Equations (2.20) and (2.21) show that greater  $(g_m/I_D)$  ratio reflects in

greater gain and bandwidth for the same power consumption.

Finally, the ability to precisely obtain transistors dimension with this methodology lays in the fact that the  $(g_m/I_D)$  vs  $I_D/(W/L)$  characteristic is independent of transistor size, and therefore is a unique characteristic for all transistors of the same type in a given batch [1].

This "universal" quality of the  $(g_m/I_D)$  curve shows that once a pair of values among  $(g_m/I_D)$ ,  $g_m$  and  $I_D$  are chosen, (W/L) ratio is unambiguously determined [1].

#### 2.4 Automatic Synthesis for Miller Amplifiers

In this section an automatic synthesis algorithm for Miller amplifiers is presented. This will illustrate the use of the  $(g_m/I_D)$  methodology applied in automatic circuit synthesis.

First the Miller Amplifier is analyzed and the equations that characterize its behavior are presented. Then the concept of design space exploration for optimum design is presented. The design space exploration in the case of the Miller amplifier is implemented with a gain-bandwidth product driven algorithm that is also explained in this section.

Finally, two amplifiers will be synthesized, each for a different transition frequency. The first for  $f_T = 100kHz$  and the second for  $f_T = 50MHz$ .

#### 2.4.1 The Miller Amplifier

The Miller compensated amplifier is a well known opamp architecture that can achieve good power consumption performances in low frequency applications. Figure 2.3 shows the amplifier schematic, where  $C_m$  is the Miller compensating capacitance,  $C_1$ ,  $C_{out}$  and  $C_3$  are parasitic capacitances and  $C_L$  is the load capacitance. In the notation used,  $C_2 = C_{out} + C_L$  is the total output capacitance of the amplifier.

#### Gain-Bandwidth Product and Phase Margin

The transfer function of this amplifier is given in equation (2.22), where  $gm_1(gm_2)$  is the transconductance of, respectively, the differential pair M1a - M1b (output stage M2) and  $g_1$  ( $g_2$ ) is the output conductance of the first stage (second stage).

$$H(s) = -\frac{gm_1(C_m s - gm_2)\frac{1}{g_1}\frac{1}{g_2}}{1 + (\frac{C_1}{g_1} + \frac{C_2}{g_2} + C_m(\frac{gm_2}{g_1g_2} + \frac{1}{g_1} + \frac{1}{g_2}))s + (\frac{C_1C_2 + C_m(C_1 + C_2)}{g_1g_2})s^2}$$

(2.22)

Figure 2.3: Miller Amplifier, including parasitics capacitances.

DC gain and expressions of poles and zero frequencies can be easily derived from equation (2.22)

$$G = \frac{gm_1gm_2}{q_1q_2} \tag{2.23}$$

$$G = \frac{gm_1gm_2}{g_1g_2}$$

$$\omega_{DP} \simeq \frac{1}{\frac{gm_2}{g_1g_2}C_m}$$

$$\omega_{NDP} \simeq \frac{gm_2C_m}{C_1C_2 + C_m(C_1 + C_2)}$$

(2.23)

$$(2.24)$$

$$\omega_{NDP} \simeq \frac{gm_2C_m}{C_1C_2 + C_m(C_1 + C_2)} \tag{2.25}$$

$$\omega_z = \frac{gm_2}{C_m} \tag{2.26}$$

where G is the DC gain,  $\omega_{DP}$  and  $\omega_{NDP}$  are the amplifier's dominant and nondominant pole angular frequencies and  $\omega_z$  is the amplifier right-half plane zero angular frequency $^3$ .

Equations (2.23-2.26) can be used to obtain the following relationships

$$\omega_T = G\omega_{DP} = \frac{gm_1}{C_m} \tag{2.27}$$

$$\omega_{T} = G\omega_{DP} = \frac{gm_{1}}{C_{m}}$$

$$NDP = \frac{\omega_{NDP}}{\omega_{T}} = \frac{gm_{2}}{gm_{1}} \frac{C_{m}^{2}}{C_{1}C_{2} + C_{m}(C_{1} + C_{2})}$$

$$Z = \frac{\omega_{z}}{\omega_{T}} = \frac{gm_{2}}{gm_{1}}$$

(2.27)

(2.28)

$$Z = \frac{\omega_z}{\omega_T} = \frac{gm_2}{gm_1} \tag{2.29}$$

where  $\omega_T$  is the gain-bandwidth product of the first order system neglecting the effect

<sup>&</sup>lt;sup>3</sup>In what follows, angular frequencies ( $\omega$ ) will be referred in the text, for compactness, as frequencies, while the actual frequencies will be noted as f

of the non-dominant pole. NDP and Z are the non-dominant pole and right-half plane zero frequencies normalized to  $\omega_T$ . These two latter relationships determine the phase margin (PM) of the amplifier. Assuming NDP, Z > 1 (that is  $\omega_{NDP}, \omega_z > \omega_T$ ), PM can be approximated as

$$PM = 90 - \arctan(\frac{1}{NDP}) - \arctan(\frac{1}{Z})$$

(2.30)

The exact PM expression must take into account that the actual transistors frequency is different from the first order approximation.

Finally, equations (2.28) and (2.29) can be combined to obtain an expression for the Miller compensating capacitance for a given NDP over Z ratio.

$$C_m = \frac{1}{2} \frac{NDP}{Z} \left[ C_1 + C_2 + \sqrt{(C_1 + C_2)^2 + 4\frac{Z}{NDP} C_1 C_2} \right]$$

(2.31)

Since NDP and Z ratios determine the phase margin of the amplifier, as we saw in equation (2.30), equations (2.27) and (2.31) become powerful design tools in a Miller amplifier synthesis.

#### Offset

Two effects will be considered in the input offset voltage of a Miller amplifier: systematic offset and random offset. The first one is due to the finite output impedance of the current mirror (M3a - b). The second one is due to the mismatch between the mirror transistors and the mismatch between the differential pair transistors.

**Systematic Offset**, as we said, is due to the finite output impedance of the current mirror. When there is a difference between the drain-source voltage of each mirror transistor, a difference appears between the drain currents. The relative error in the copy can be estimated as

$$\frac{\Delta I_D}{I_D} = \frac{1}{I_D} \frac{\Delta V}{r_o} = \frac{\Delta V}{V_A} \tag{2.32}$$

where  $\Delta V = V_{DS3a} - V_{DS3b}$ ,  $r_o = V_A/I_D$  is the output resistance of the mirror transistors and  $V_A$  is the Early voltage. The offset voltage due to this copy error can be calculated through the differential pair transconductance as

$$V_{off} = \frac{\Delta I_D}{g_m} = \frac{\Delta I_D/I_D}{(g_m/I_D)} = \frac{\Delta V/V_A}{(g_m/I_D)}$$

(2.33)

which is a useful expression as it estimates the systematic offset voltage as a function of the  $(g_m/I_D)$  ratio of the differential pair.

Random Offset is due to the mismatch between the transistors of the mirror and the mismatch between the transistors of the differential pair. To model these

mismatches the following analysis is made. Current through a forward saturated transistor can be expressed as a function of the current factor ( $\beta = \mu C'_{ox}W/L$ ), the threshold voltage ( $V_{T0}$ ) and the gate voltage. As gate voltage is the same for both transistors, either in the mirror or in the differential pair, the current error can be written as

$$I_D - \overline{I_D} = \Delta I_D = \frac{\partial I_D}{\partial V_{T0}} \Delta V_{T0} + \frac{\partial I_D}{\partial \beta} \Delta \beta$$

(2.34)

where  $\overline{I_D}$  is the mean current value and  $I_D$  is the actual current value of each sample. The partial derivatives can be approximated as

$$\frac{\partial I_D}{\partial V_{T0}} = \frac{\partial I_D}{\partial V_G} \frac{\partial V_G}{\partial V_{T0}} = g_m \cdot 1 = g_m \tag{2.35}$$

$$\frac{\partial I_D}{\partial \beta} = \frac{I_D}{\beta} \tag{2.36}$$

allowing us to rewrite equation (2.34) as

$$\Delta I_D = g_m \Delta V_{T0} + \frac{I_D}{\beta} \Delta \beta \tag{2.37}$$

The standard deviation of the current will depend on the standard deviation of  $V_{T0}$  and  $\beta$ . Since this two random effects are considered statistically independent, the standard deviation of the current is

$$\frac{\sigma_{I_D}}{I_D} = \sqrt{\left(\frac{g_m}{I_D}\right)^2 \sigma_{V_{T0}}^2 + \frac{\sigma_{\beta}^2}{\beta^2}}$$

(2.38)

where the standard deviation of  $V_{T0}$  and  $\beta$  ( $\sigma_{V_{T0}}^2$ ,  $\sigma_{\beta}^2$ ) can be expressed using Pelgrom's model [36]:

$$\sigma_{V_{T0}}^2 = \frac{A_{V_{T0}}^2}{W.L} + S_{V_{T0}}^2 D^2 \tag{2.39}$$

$$\frac{\sigma_{\beta}^2}{\beta^2} = \frac{A_{\beta}^2}{W.L} + S_{\beta}^2 D^2 \tag{2.40}$$

Here D represents the distance between transistors and depends strongly on transistors's layout and size. When considering transistors with an almost square structure, D can be approximated as  $D = \sqrt{WL}$  [3]. Finally,  $A_{\beta}$ ,  $A_{V_{T0}}$ ,  $S_{V_{T0}}$  and  $S_{\beta}$  are the coefficients that characterize the matching properties in a particular process and can be obtained from the foundry itself or from published results on matching.

Taking transistor's mismatch on the mirror and the differential pair as statistically independent, total current error can be expressed as

$$\frac{\sigma_{I_D}}{I_D} = \sqrt{\left(\frac{\sigma_{I_D}}{I_D}\right)_{pair}^2 + \left(\frac{\sigma_{I_D}}{I_D}\right)_{mirr}^2} \tag{2.41}$$

Figure 2.4: Offset voltage in a differential pair with active load as a function of  $(g_m/I_D)_{pair}$ .

which gives a total mismatch offset

$$V_{off} = \frac{\sigma_{I_D}/I_D}{(g_m/I_D)_{pair}} \tag{2.42}$$

Equations (2.38)-(2.42) conform a useful set to easily estimate the input offset voltage due to transistor mismatch in the amplifier.

Figure 2.4 shows an example where the offset voltage is evaluated as a function of the  $(g_m/I_D)$  ratio of the differential pair for given transistors sizes and mirror's  $(g_m/I_D)$  ratio. Here we can see that a steep decrease in the offset voltage appears as we move from strong to moderate inversion. As we enter into deep weak inversion the offset voltage tends to a constant value. It can be seen also that generally, systematic offset is much smaller than mismatch offset. Similar and further analysis on the effect of the  $(g_m/I_D)$  ratio on mirror precision and OTA's offset voltage can be found on [3].

#### Input Common Mode Range and Output Swing

Input Common Mode Range (ICMR) and Output Swing (OS) can be easily estimated using the equations provided by the ACM model for saturation voltage  $(V_{DSsat}$ , equation (2.8)) and gate voltages (equation (2.7)).

**ICMR** is determined by the saturation voltage of the differential pair's current source (M5) and the gate voltage of the mirror (M3a - b), see Figure 2.3).

$$V_{SS} + V_{GS3} + V_{DSsat1} - V_{GS1} < V_{iCM} < V_{DD} - V_{DSsat5} - V_{GS1}$$

(2.43)

**Output Swing**, on the other hand is determined by the saturation voltages of the output stage transistors (M2 and M4, see Figure 2.3).

$$V_{SS} + V_{DSsat2} < Vo < V_{DD} - V_{DSsat4} \tag{2.44}$$

#### 2.4.2 Gain-Bandwidth Driven Synthesis Algorithm

The basic synthesis algorithm for the Miller amplifier that will be applied here, was presented by Jespers [2]. The main idea is to synthesize a Miller amplifier for a given gain-bandwidth product  $\omega_T$  and a given phase margin (PM). The rest of the performance specifications (DC gain, SR, noise, etc.) are adjusted by the selection of the design variables  $((g_m/I_D)$  ratios and lengths).

The designer chooses the  $(g_m/I_D)$  ratio of each stage (that is the  $(g_m/I_D)$  ratio of the differential pair transistors and the  $(g_m/I_D)$  ratio of transistor M2) taking into consideration, for example, the objective gain-bandwidth product and the current budget available. Also, the length of the transistors is selected according to noise, gain and matching considerations. NDP and Z ratios can be chosen for a given objective phase margin. For example, it is common to take NDP = 2.2 and Z = 10 to achieve  $PM \simeq 60^{\circ}$ .

Then using equations (2.27) and (2.31) and applying the  $(g_m/I_D)$  methodology, transistors sizes and other parameters (DC gain, SR, noise, etc.) can be obtained.

The basic algorithm, as presented by Jespers is shown in Algorithm 2.1. In this algorithm, there are some missing design criteria. Step 4 (Algorithm 2.1) establishes mirror design to minimize offset. This is one of the choices, but noise, frequency response or gain could be used jointly with or instead of this criterium. On step 5 (Algorithm 2.1), the design criterium for the  $(g_m/I_D)$  ratio isn't even specified. In section 2.4.4 the criterium used in this work is explained.

#### 2.4.3 Design Optimization Through Design Space Exploration

In Algorithm 2.1,  $(g_m/I_D)$  ratios and lengths must be selected a priori by the designer. However, this may not be an easy task for an unexperienced user and can lead to very non-optimum designs.

To obtain an optimum design, we can define a design space by both stage's active transistors  $(g_m/I_D)$  ratios and explore the characteristics of the amplifier on it. This may be achieved applying Algorithm 2.1 in a mesh of points for the defined design space. In this way constant-level curves for every aspect of the amplifier required by the designer can be plotted to graphically show the behavior of the amplifier in the design space. This idea is based on the  $(g_m/I_D)$  based

<sup>&</sup>lt;sup>4</sup>Actually, since NDP and Z are normalized to  $\omega_T$  of the first order system approximation, we could expect that the real PM will be bigger. However, other effects present in the real amplifier, as the pole-zero doublet from the input stage mirror, will eventually have a negative impact on the PM, leading to actual PM of about  $60^{\circ}$ .

#### **Algorithm 2.1** Gain-Bandwidth Driven Automatic Synthesis.

- 1. Miller compensating capacitance  $C_m$  is grossly estimated in a first guess.

- 2. Differential pair is synthesized using equations (2.27) and (2.5)

$$gm_1 = \omega_T C_m \Rightarrow I_{D1} = \frac{gm_1}{(g_m/I_D)_1}$$

$(W/L)_1 = \frac{I_{D1}}{\frac{1}{2}\mu n C'_{ox}\phi_t^2 i_{f1}}$

3. Output stage transistor M2 is synthesized using equations (2.29) and (2.5)

$$gm_5 = Zgm_1 \Rightarrow I_{D2} = \frac{gm_2}{(g_m/I_D)_2}$$

$(W/L)_2 = \frac{I_{D2}}{\frac{1}{2}\mu nC'_{ox}\phi_t^2 i_{f2}}$

4. Minimum systematic offset criterion can be used to design the current mirror M3a-M3b

$$V_{G3a} = V_{D3b} = V_{G2} \Rightarrow (g_m/I_D)_3 = (g_m/I_D)_2$$

$I_{D3} = I_{D1} \Rightarrow (W/L)_3 = \frac{I_{D1}}{\frac{1}{2}\mu n C'_{ox}\phi_t^2 i_{f2}}$

5. The design of the output stage current source transistor M4 can be based in several criteria. An example is shown in section 2.4.4.

$$(W/L)_4 = \frac{I_{D2}}{\frac{1}{2}\mu n C'_{ox}\phi_t^2 i_{f4}}$$

6. First stage current source transistor M5 synthesis follows

$$V_{G5} = V_{G4} \Rightarrow (g_m/I_D)_5 = (g_m/I_D)_4$$

$I_{D5} = 2I_{D1} \Rightarrow (W/L)_5 = \frac{2I_{D1}}{\frac{1}{2}\mu n C'_{ox}\phi_t^2 i_{f4}}$

- 7. All the transistors sizes are obtained using the selected lengths.

- 8. Parasitic capacitances  $C_1$  and  $C_2$  are calculated. Now we can use equation (2.31) to obtain a new Miller capacitance  $C_m$

$$C_m = \frac{1}{2} \frac{NDP}{Z} \left[ C_1 + C_2 + \sqrt{(C_1 + C_2)^2 + 4\frac{Z}{NDP}C_1C_2} \right]$$

9. With the newly calculated  $C_m$  we iterate from step 2, until the value of  $C_m$  converges.

#### Algorithm 2.2 Power Optimization Automatic Synthesis

- 1. The length of all transistors is set to minimum.

- 2.  $(g_m/I_D)_4$  ratio is fixed somewhere in moderate inversion.

- 3. The design space is swept using Algorithm 2.1. We choose the optimum combination of input and output stage  $(g_m/I_D)$  ratio.

- 4. The length of M3 is swept. We choose  $L_3$  to obtain good gain and frequency response.

- 5.  $(g_m/I_D)_4$  ratio is swept. We choose it to obtain good Output Swing and total area.

- 6. The length of M4 is swept. We choose  $L_4$  to obtain good gain and total area. We iterate with step 5 until we converge to a solution for both  $(g_m/I_D)_4$  and  $L_4$ .

- 7. We run Algorithm 2.1 with the values obtained for  $(g_m/I_D)$  ratios and L's.

methodology [1], explained in section 2.3, and has been used in previous works ([2,3]).

Doing so, not only optimum combinations of the  $(g_m/I_D)$  ratios can be obtained, but also the evolution of the aspect under study can be evaluated. This means that we may consider several aspects of the amplifier and select an optimum combination of the  $(g_m/I_D)$  ratios in a multi-aspect sense.

Lengths and non-critical  $(g_m/I_D)$  ratios (e.g. second stage bias transistor) can also be selected using similar methodology. For example, a sweep of the length of mirror transistors can be used to select an optimum trade-off between frequency response and gain.

Applying these ideas, we developed an algorithm that explores the design space of the Miller amplifier to obtain optimum consumption with good gain and area. thus, the algorithm also analyzes the effects of lengths and passive transistor's  $(g_m/I_D)$  ratios to consider the trade-offs in the performance of the amplifier.

This algorithm is presented in Algorithm 2.2 and in sections 2.4.4 and 2.4.5 we present two design examples. The algorithm is explained thoroughly when the first example is introduced in section 2.4.4.

#### 2.4.4 Synthesis Example: Micropower 100kHz Miller Amplifier

Table (2.1) shows the specifications for the design of this first example. As it can be seen, this design is intended for low frequency, low supply voltage, micropower operation. The process parameters are taken from a  $0.8\mu m$  technology.

First, the initial conditions for the algorithm (steps 1 and 2) are set. The length of the transistors can be latter adjusted to improve gain and  $(g_m/I_D)_4$  was set to 10. We then sweep the design space to obtain constant consumption, area

| $f_T$        | 100kHz     |

|--------------|------------|

| Consumption  | $< 1\mu A$ |

| Power Supply | 2V         |

| $C_L$        | 10pF       |

| PM           | > 60       |

| Tech.        | $0.8\mu m$ |

Table 2.1: Specifications for a Micropower 100kHz Miller Amplifier

Figure 2.5: Design space exploration: Total consumption (in  $\mu A$ ) of the 100kHz Miller Amplifier.

and dc gain curves.

Figures 2.5, 2.6 and 2.7 show the space exploration for consumption, area and dc gain respectively. They clearly show that optimum consumption with reasonable gain and die area can be obtained when both stage's active transistors are in weak inversion. Particularly we choose:

$$(g_m/I_D)_1 = 24$$

$(g_m/I_D)_2 = 22$

The lengths of the differential pair transistors and output stage active transistor are chosen  $3\mu m$  to avoid big sizes, but at the same time obtain a good gain.

Mirror's transistors can be designed according to several criteria. As shown in Algorithm 2.1 (step 4) we choose to minimize the systematic offset of the amplifier. As seen in section 2.4.1, systematic offset is due to a difference in the drain-source

Figure 2.6: Design space exploration: Die area estimation (in  $\mu m^2$ ) of the 100kHz Miller Amplifier..

Figure 2.7: Design space exploration: DC Gain (in dB) of the 100kHz Miller Amplifier..

voltage of both transistors. Thus it can be minimized if both voltages are designed to be the same, which can be achieved using the same  $(g_m/I_D)$  ratio than transistor M2. Now, we only need to choose the length of both transistors. To do so, we will consider two effects of the length in the amplifier's behavior: gain and frequency response (step 4).

The effect on gain, lays on the fact that the output resistance of the transistors can be modelled to be proportional to the length through the Early voltage  $(r_o =$  $V_A/I_D$ ,  $V_A=V_EL$ ). Regarding, the frequency response, a given  $(g_m/I_D)$  ratio and drain current fix the W/L ratio. That means that larger length implies larger width and, thus, larger parasitic capacitance (which depends grossly on W and on the WL product). Since the parasitic capacitance  $C_3$  adds a pole-zero doublet to the response of the Miller amplifier [37], the length of the mirror transistors also has an effect on the frequency response. This doublet has a small impact on the frequency response but a large one on the transient response and should be kept beyond the working frequencies.

$$\omega_{pDOUB} = \frac{g_{m3}}{C_3} \tag{2.45}$$

$$\omega_{pDOUB} = \frac{g_{m3}}{C_3}$$

$$\omega_{zDOUB} = \frac{2g_{m3}}{C_3}$$

(2.45)

Both effects can be seen on Figure 2.8 where the doublet frequency is calculated using equation (2.45). The improvement on the gain starts to diminish as a longer transistor is selected, because for  $L_3 \gg L_1$  the gain is determined only by  $L_1$ . Thus, in this design we choose:

$$L_3 = 9\mu m \tag{2.47}$$

which gives a good gain and a doublet frequency almost a decade above the transition frequency.

The design criteria for the output stage bias transistor (M4) wasn't specified on Algorithm 2.1. We choose to select its  $(g_m/I_D)$  ratio and length with the following analysis (steps 5 and 6). The design of transistor M4 affects gain, total area (like any transistor) and output swing. Length will affect gain and area (eqs. 2.49 and (2.50) and  $(g_m/I_D)$  ratio will affect area and output swing (eqs. 2.48 and 2.49).

$$V_{DSsat} = f\left((g_m/I_D)\right) \Rightarrow OS = f\left((g_m/I_D)\right)$$

(2.48)

$$\left(\frac{W}{L}\right) = f\left((g_m/I_D)\right) \Rightarrow Area = f\left((g_m/I_D)\right), L_4$$

(2.49)

$$Gain = f(g_4 + g_2) \Rightarrow Gain = f(L_4)$$

(2.50)

where  $g_4, g_2$  are the output conductance of transistors M4, M2 respectively.

Figure 2.9 shows the dependence of the output swing and total area with  $(g_m/I_D)_4$ . In this figure we see that the output swing behaves, as expected, according to the relationship between  $V_{DSsat}$  and  $(g_m/I_D)$  ratio seen on equation (2.8). This behavior shows that there is no reason to go into deep weak inversion because

Figure 2.8: Gain and doublet frequency dependence on the length of M3.

Figure 2.9: Output swing and total area dependence on  $(g_m/I_D)_4$  ratio.

Figure 2.10: Gain and total area dependence on the length of M4.

no further increase on the output swing is achieved. What is more, the total area starts to raise exponentially as we move beyond  $(g_m/I_D)_4 > 10$ . Thus, we choose

$$(g_m/I_D)_4 = 6$$

which gives an upper output swing limit of 0.7V (power supply:  $\pm 1V$ ) and a total area of about  $10^4 \mu m^2$ .

Figure 2.10 shows the dependence of the gain and total area with  $L_4$ . As with the case of transistor M3, increasing the length improves the gain, but only to some extent. We choose

$$L_4 = 60 \mu m$$

which gives a good gain and a total area of about  $10^4 \mu m^2$ .

#### Final Design

The final design obtained (step 7) can be seen on Table (2.2). Here we see that, as expected, the frequency response isn't fully achieved due to the presence of higher order effects like the mirror pole-zero doublet. Systematic offset is effectively eliminated, as simulation showed that drain-source voltage difference in mirror transistors is below 5mV. Total consumption is kept below  $1\mu A$ . The ratio between both stage's bias current is due to factor Z (equation (2.29)). It can be easily seen that for the same  $(g_m/I_D)$  ratios the currents ratio equals Z. A more efficient architecture is obtained when using a R-C compensating network that eliminates the right-half plane zero.

This design was simulated on SPICE using the BSIM3v3 transistor model.

| 100kHz Miller Amplifier |                       |                    |  |  |

|-------------------------|-----------------------|--------------------|--|--|

| Gain                    | Total                 | 113.04dB           |  |  |

|                         | 1st stage             | 55.23dB            |  |  |

|                         | 2nd stage             | 57.81dB            |  |  |