## Universidad de la República Facultad de Ingeniería

# On the design of ultra low voltage CMOS oscillators

# Tesis presentada a la Facultad de Ingeniería de la Universidad de la República por

## Mariana Siniscalchi

EN CUMPLIMIENTO PARCIAL DE LOS REQUERIMIENTOS

PARA LA OBTENCIÓN DEL TÍTULO DE

DOCTORA EN INGENIERÍA ELÉCTRICA.

| DIRECTORES DE TESIS                                         |

|-------------------------------------------------------------|

| Carlos Galup Universidade Federal de Santa Catarina         |

| Fernando Silveira Universidad de la República               |

|                                                             |

| Tribunal                                                    |

| Andreas Andreou Johns Hopkins University, Estados Unidos    |

| Sylvain Bourdel Université Grenoble Alpes, Francia          |

| Conrado Rossi Universidad de la República                   |

| Carlos Galup Universidade Federal de Santa Catarina, Brasil |

| Fernando Silveira Universidad de la República               |

|                                                             |

| Director Académico                                          |

| Fernando Silveira                                           |

$\begin{array}{c} {\rm Montevideo} \\ {\rm Tuesday} \ 12^{\rm th} \ {\rm May}, \ 2020 \end{array}$

$On\ the\ design\ of\ ultra\ low\ voltage\ CMOS\ oscillators,\ Mariana\ Siniscalchi.$

## ISSN 1688-2784

This thesis was prepared in LATeX using the iietesis class (v1.1). Total number of pages 115. Compiled on Tuesday  $12^{\rm th}$  May, 2020.  $\label{eq:hatch} \text{http://iie.fing.edu.uy/}$  Why repeat the old errors, if there are so many new errors to commit?

Bertrand Russell

# Acknowledgment

First of all, I would like to thank my advisors Prof. Carlos Galup-Montoro and Prof. Fernando Silveira for their support, patience and knowledge.

I am thankful to the members of the committee, Prof. Andreas Andreou, Prof. Sylvain Bourdel and Prof. Conrado Rossi for their kind participation.

I would like to acknowledge the support from grant ANII POS\_NAC\_2015\_1\_109743, CAP and CSIC Universidad de la República, the project STIC AmSud O2ERF and the Brazilian research agency Coordenação de Aperfeiçoamento de Pessoal de Nível Superior (CAPES), Finance Code 001, along with MOSIS for providing access to integration.

My sincere thanks also goes to my colleagues from the IIE of Universidad de la República who, in one way or another, are part of this process. Special thanks to Carolina Cabrera, Andrés Seré and Guillermo Antúnez, for their support and insightful suggestions.

Also, I am thankful to my colleagues from the LCI of Universidade Federal de Santa Catarina for making me feel welcome, specially to Daniel Novack for helping me out with some of the measurements and also to Andrés Hurtado, Márcio Schneider, Jefferson Ribeiro and Franciele Norenberg for many useful discussions and their valuable support.

I would also like to thank the people of the RFIC-Lab of Université Grenoble Alpes for receiving me during my stay to work on the project O2ERF.

I am grateful to the director of the Laboratory of UTE, Daniel Slomowitz, and members of his staff for making themselves and their equipment available for the high precision frequency measurements.

Last but not least, I would like to thank my friends and family for their continuous support. Without them, none of this would have been possible. My special thanks goes to Mariana del Castillo, Juliana Viera and Nicolás Gammarano. I am thankful to Nicolás, not only for supporting me through the ups and downs during my studies, but also for many useful discussions and his valuable work.

# Resumen

Los nodos sensores inalámbricos tienen fuertes requerimientos de bajo consumo de manera de operar con baterías pequeñas o algún mecanismo de cosecha de energía, o ambos. En muchos casos, la cosecha de energía térmica o electroquímica provee tensiones muy bajas del orden de 100 mV o incluso menos. Los sistemas de internet de las cosas incluyen un módulo de reloj que debe estar siempre encendido a efectos de contar el tiempo. Los osciladores a cristal son probadamente útiles como relojes de bajo consumo, y en este contexto la reducción de la tensión es una estrategia conveniente. Por lo tanto, presentamos osciladores a cristal de 32 kHz operando con sólo 60 mV de tensión de alimentación. Dos implementaciones, basadas en el circuito Schmitt trigger para dos cristales diferentes, se diseñan y caracterizan experimentalmente.

Estos osciladores a cristal están basados en la aplicación del Schmitt trigger como amplificador. Se provee una guía para el diseño de este bloque para funcionar como el amplificador de un oscilador a cristal. Adicionalmente se propone un modelo dinámico del Schmitt trigger y los resultados del modelo son comparados con resultados de simulación. Los amplificadores son caracterizados experimentalmente, proveyendo una ganancia de 2.48 V/V con 60 mV de tensión de alimentación. Tal como se pretende en la etapa de diseño, para tensiones mayores a 100 mV aparece el fenómeno de histéresis y el Schmitt trigger comienza a operar como un comparador.

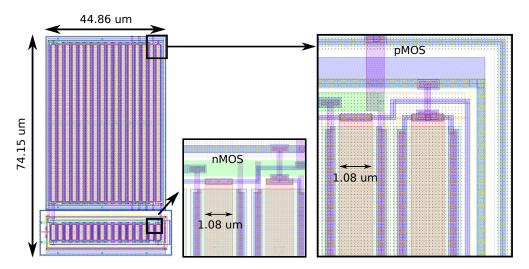

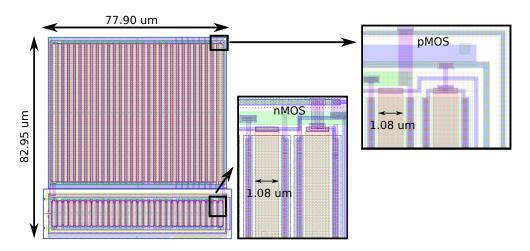

Los Schmitt trigger para operar como amplificadores de los osciladores a cristal son diseñados en un proceso CMOS de 130 nm y ocupan un área de 45 µm x 74 µm y 78 µm x 83 µm, respectivamente. El consumo de potencia de sendos osciladores es 2.26 nW y 15 nW y la estabilidad en temperatura obtenida es de 62 ppm (25-62°C) y 50 ppm (5-62°C), respectivamente. Se midieron la dependencia del consumo de corriente con respecto a la tensión de alimentación, la frequencia de oscilación, el tiempo de arranque y la amplitud de oscilación. La desviación de Allan es 30 ppb en ambos osciladores.

Por otra parte, un oscilador LC controlado por voltaje es diseñado en un proceso CMOS de silicio sobre aislante en deplexión total de 28 nm, para aplicaciones de radiofrecuencia. Se estudia la posibilidad de utilizar en este caso el mismo modelo utilizado para el diseño del Schmitt trigger. Dicho modelo es válido en todas las regiones de inversión y está desarrollado para transistores de tipo sustrato y de canal largo. La arquitectura de transistores nMOS entrelazados es la utilizada para este oscilador. Se estudia el límite teórico para la mínima tensión de alimentación. Los transistores son dimensionados de manera óptima para obtener

el mínimo consumo de potencia posible, utilizando un enfoque de baja tensión y el desempeño del oscilador se obtuvo mediante simulaciones.

# **Abstract**

Wireless sensor nodes require very tight power budgets to operate from either a small battery, some energy harvesting mechanism or both. In many cases, thermal or electrochemical harvesting devices provide very low voltages of the order of 100 mV or even lower. Time-keeping functionality is required in IoT systems and the time-keeping module must be on at all times. Crystal oscillators have proven to be useful for low power time-keeping applications, and in this context supply voltage lowering is a convenient strategy. Therefore, 32 kHz crystal oscillators operating with only 60 mV supply are presented. Two implementations based on a Schmitt trigger circuit for two different crystals were designed and experimentally characterized.

These crystal oscillators are based on the application of a Schmitt trigger as an amplifier. Guidelines for designing this block to be the amplifier of a crystal oscillator are provided. Furthermore, a dynamic model of the Schmitt trigger is proposed and the model results are compared against simulations. The amplifiers were experimentally characterized, providing a gain of  $2.48~\rm V/V$  with a  $60~\rm mV$  power supply. As it was intended in the design stage, for voltages above  $100~\rm mV$  hysteresis appears and the Schmitt trigger starts operating as a comparator.

The Schmitt triggers to operate as amplifiers of the crystal oscillators are designed in a 130 nm CMOS process, requiring an area of 45  $\mu$ m x 74  $\mu$ m and 78  $\mu$ m x 83  $\mu$ m, respectively. The power consumptions of the crystal oscillators are 2.26 nW and 15 nW and the temperature stabilities attained are 62 ppm (25-62°C) and 50 ppm (5-62°C), respectively. The dependence on the supply voltage of the current consumption, fractional frequency, start-up time and oscillation amplitude were measured. The Allan deviation is 30 ppb for both oscillators.

On the other hand, an LC voltage controlled oscillator (VCO) is designed in 28 nm FD-SOI for RF applications. The possibility of modeling the transistors in the 28 nm FD-SOI technology by means of the all inversion region long channel bulk transistor model used for the Schmitt trigger circuits, is studied. A cross-coupled nMOS architecture is used to build the VCO. The theoretical limit for the minimum supply voltage that enables oscillation is studied. The transistors were optimally sized to aim the minimum power consumption through a low-voltage approach and the performance of the VCO was obtained through simulations.

# List of Abbreviations

AC alternate current BLE Bluetooth low-energy

CMOS complementary metal oxide semiconductor

DC direct current

FD-SOI fully depleted silicon on insulator

IoT internet of things

LC-VCO LC-tank voltage controlled oscillator

LUT look up table MI moderate inversion

MOSFET metal oxide semiconductor field effect transistor

nMOS n-type metal oxide semiconductor

PCB printed circuit board PLL phase locked loop

pMOS p-type metal oxide semiconductor

RF radio frequency SI strong inversion SoC system on chip

UTBB ultra thin body and buried oxide

WI weak inversion

WSN wireless sensor network

# List of Symbols

Avoltage gain  $A_{Sk}$ drain or source diffusion area of transistor k $C_J'$   $C_{Jk}$ junction capacitance per unit area extrinsic capacitance of the drain or source to bulk junction  $C_{jk}$ capacitance between nodes j and k  $C_m$ motional capacitance of the crystal oxide capacitance per unit area  $C_{pk\,ov}$ overlap capacitance at node p of transistor k $f_T$ transition frequency  $G_m$ equivalent transconductance  $g_{mb}$ bulk transconductance critical value of the transconductance to enable oscillation  $G_{mcrit}$ drain transconductance  $g_{md}$ gate transconductance  $g_{mg}$ transconductance value to achieve the maximum negative  $G_{mopt}$ resistance source transconductance  $g_{ms}$  $G_o$ equivalent output conductance  $I_D$ drain current  $I_F$ forward current  $i_f$ forward inversion level current strength of an nMOS transistor  $I_N$ current strength of a pMOS transistor  $I_P$ current strength of transistor k $I_k$  $I_R$ reverse current reverse inversion level  $i_r$  $I_S$ specific current Ltransistor channel length specific current of an equivalent square transistor  $I_{SQ}$ Boltzmann's constant (=  $1.38 \times 10^{-23}$  J/K) LDoverlapping distance on the channel length direction be-

tween the source or drain and the gate

# Chapter 0. List of Symbols

| $L_m$             | motional inductance of the crystal                      |

|-------------------|---------------------------------------------------------|

| $\mu$             | carrier mobility                                        |

| n                 | slope factor                                            |

| $\phi_t$          | thermal voltage $(=kT/q)$                               |

| q                 | electronic charge (= $1.60 \times 10^{-19} \text{ C}$ ) |

| $Q_B$             | total bulk charge                                       |

| $Q_D$             | total drain charge                                      |

| $Q_G$             | total gate charge                                       |

| $Q_{ID}^{\prime}$ | inversion charge per unit area at drain                 |

| $q_{ID}'$         | normalized inversion charge density at drain            |

| $Q_{IS}^{\prime}$ | inversion charge per unit area at source                |

| $q_{IS}'$         | normalized inversion charge density at source           |

| $Q_S$             | total source charge                                     |

| $R_m$             | motional resistance of the crystal                      |

| $R_O$             | output resistance                                       |

| T                 | absolute temperature                                    |

| au                | time constant                                           |

| $V_{BP}$          | back-plane voltage                                      |

| $V_D$             | drain-to-bulk voltage                                   |

| $V_{DD}$          | supply voltage                                          |

| $V_{DDH}$         | minimum supply voltage to obtain hysteresis             |

| $V_G$             | gate-to-bulk voltage                                    |

| $V_P$             | pinch-off voltage                                       |

| $V_S$             | source-to-bulk voltage                                  |

| $V_T$             | threshold voltage                                       |

| $V_{T0}$          | zero-bias threshold voltage                             |

| W                 | transistor channel width                                |

| $Z_{Cr}$          | crystal impedance                                       |

| $Z_m$             | motional impedance of the crystal                       |

|                   |                                                         |

# Contents

| A             | ckno  | wledgment                                                          | ii  |

|---------------|-------|--------------------------------------------------------------------|-----|

| $\mathbf{R}$  | esum  | nen                                                                | vi  |

| $\mathbf{A}$  | bstra | net                                                                | ix  |

| Li            | st of | Abbreviations                                                      | x   |

| $\mathbf{Li}$ | st of | Symbols                                                            | xii |

| 1             | Inti  | roduction                                                          | 1   |

| 2             | Sch   | mitt trigger as an amplifier for ultra low voltage                 | 7   |

|               | 2.1   | Basic all-region MOSFET model                                      | 7   |

|               |       | 2.1.1 Weak inversion model of the MOSFET                           | 8   |

|               | 2.2   | Small-signal transconductances                                     | Ć   |

|               | 2.3   | Capacitive coefficients                                            | 10  |

|               | 2.4   | Parameter extraction                                               | 11  |

|               | 2.5   | DC transfer characteristic of the Schmitt trigger                  | 12  |

|               | 2.6   | Low-frequency small signal equivalent model of the Schmitt trigger | 14  |

|               | 2.7   | Comparison between Schmitt trigger and CMOS inverter               | 17  |

| 3             | Sch   | mitt trigger dynamic model                                         | 19  |

|               | 3.1   | Capacitive coefficients                                            | 19  |

|               | 3.2   | Intrinsic transition frequency                                     | 22  |

|               | 3.3   | Schmitt trigger with hysteresis                                    | 23  |

| 4             | Des   | sign of crystal oscillators                                        | 27  |

|               | 4.1   | Equivalent impedance of the quartz crystal                         | 27  |

|               | 4.2   | Linear analysis of the basic Pierce oscillator                     | 28  |

|               | 4.3   | Pierce crystal oscillator operation                                | 30  |

|               |       | 4.3.1 Lossless amplifier                                           | 31  |

|               |       | 4.3.2 Lossy amplifier                                              | 32  |

|               | 4.4   | Design of crystal oscillators based on Schmitt trigger             | 33  |

## Contents

| <b>5</b>     | 5 Results of two crystal oscillators based on Schmitt trigger |                                                                         |                                                           |            |  |

|--------------|---------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------|------------|--|

|              | 5.1                                                           | 1 Measurement results of the Schmitt trigger as a stand-alone amplifier |                                                           |            |  |

|              | 5.2                                                           | Measu                                                                   | rement results of the crystal oscillators                 | 41         |  |

|              |                                                               | 5.2.1                                                                   | Oscillator power and current consumption                  | 43         |  |

|              |                                                               | 5.2.2                                                                   | Oscillator start-up                                       | 45         |  |

|              |                                                               | 5.2.3                                                                   | Oscillator output voltage amplitude                       | 47         |  |

|              |                                                               | 5.2.4                                                                   | Oscillator frequency                                      | 49         |  |

|              |                                                               | 5.2.5                                                                   | Comparison against state-of-the-art                       | 50         |  |

| 6            | Low                                                           | powe                                                                    | r LC voltage controlled oscillator                        | <b>55</b>  |  |

|              | 6.1                                                           | Model                                                                   | ing a nanometer FD-SOI transistor with a basic all-region |            |  |

|              |                                                               | MOSF                                                                    | ET model                                                  | 55         |  |

|              |                                                               | 6.1.1                                                                   | Parameter extraction for FD-SOI nanometer device          | 57         |  |

|              |                                                               | 6.1.2                                                                   | Comparison of the model against simulations               | 58         |  |

|              | 6.2                                                           | $\operatorname{Study}$                                                  | of the minimum operating voltage limit                    | 61         |  |

|              |                                                               | 6.2.1                                                                   | Design of the inductor                                    | 63         |  |

|              |                                                               | 6.2.2                                                                   | Design of the transistors for minimum supply voltage      | 64         |  |

|              | 6.3                                                           | Low p                                                                   | ower voltage controlled oscillator                        | 66         |  |

|              |                                                               | 6.3.1                                                                   | Design and simulations of the VCO                         | 66         |  |

|              |                                                               | 6.3.2                                                                   | Comparison of the designed VCO to prior works             | 70         |  |

|              |                                                               | 6.3.3                                                                   | How to reduce phase noise                                 | 72         |  |

| 7            | Con                                                           | clusio                                                                  |                                                           | <b>75</b>  |  |

|              | 7.1                                                           | Future                                                                  | e work                                                    | 76         |  |

| Aŗ           | pen                                                           | dixes                                                                   |                                                           | <b>7</b> 8 |  |

| $\mathbf{A}$ | Disp                                                          | olacem                                                                  | ent of the locus of the impedance $Z_C$ due to losses in  |            |  |

|              | the                                                           | amplif                                                                  | der                                                       | <b>7</b> 9 |  |

| В            | Schr                                                          | nitt tr                                                                 | rigger circuit layout                                     | 81         |  |

| Bi           | bliog                                                         | raphy                                                                   |                                                           | 83         |  |

| Lis          | List of tables 8                                              |                                                                         |                                                           |            |  |

|              | List of figures 90                                            |                                                                         |                                                           |            |  |

| 111          | JU UI                                                         | ngui C                                                                  | <i>ა</i>                                                  | 50         |  |

# Chapter 1

# Introduction

Wireless sensor nodes, among other Internet of Things (IoT) elements, require a very tight power budget in order to be powered from either a small battery, some energy harvesting mechanism or both. Applications involving continuous monitoring or idle listening must spend the least energy possible. If so, the battery lifetime would be extended and operation with a harvester only may be possible. In fact, the limited power budget might be the most significant challenge [1].

Voltage scaling has proven effective for energy consumption reduction [2]. Subthreshold design has been extensively used in power constrained applications, such as time-keeping wrist watches [3]. More recently, near threshold design techniques have been developed and supply voltage has been more aggressively lowered to further reduce power consumption [2]. All kinds of circuits are involved, from a Bluetooth Low-Energy (BLE) receiver front-end operating with 0.18 V [4] to a whole System on Chip (SoC) [5].

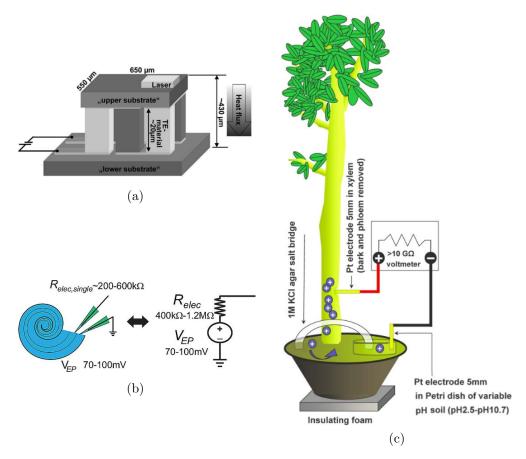

However, there are harvesters that provide smaller voltage levels. This is the case of thermoelectric generators [6], which provide a voltage supply in presence of a temperature difference as it is shown in the schematic drawing of Fig. 1.1a. In the IoT applications context, a small thermoelectric generator patch may be worn on the skin and 2 °C, found between the air and the skin, suffice to obtain 150 mV. However, the voltage obtained drops with the temperature difference, compromising the operation of the device powered from this harvester.

Photovoltaic cells arrangements used indoors also provide low voltage levels [7]. For an indoor well illuminated environment, say 200 lux, 0.88 V and 132  $\mu$ W are extracted. However, if light diminishes to 50 lux, power would drop to less than 50  $\mu$ W and voltage to 0.3 V. Moreover, each one of these photovoltaic cells spends much more area (19.6 mm  $\times$  50 mm) than the aforementioned thermoelectric generator in Fig. 1.1a.

In many cases, thermal or electrochemical harvesting devices provide very low voltages of the order of 100 mV or even lower [8–10]. A startup boost converter is presented in [9] using a thermoelectric generator that provides 50 mV. In [10], energy is harvested from the endocochlear potential, as shown in Fig. 1.1b. This is a 70 to 100 mV electrochemical bio-potential inside the mammalian ear, that provides power within the range from 1.1 to 6.25 nW. In [8], less than 100 mV are

### Chapter 1. Introduction

Figure 1.1: (a) Schematic drawing of an application of the Micro-Peltier coolers, taken from [6]. Electrochemical bio-potential examples: schematic drawing of (b) the endocochlear potential as an energy harvesting source, extracted from [10], and (c) the bio-potential between a tree and its soil, taken from [8].

obtained as a result of the pH difference between a tree and its soil. Figure 1.1c shows a schematic diagram on how this voltage difference appears.

Complementary Metal Oxide Semiconductor (CMOS) electronics is possible at such low supply voltages [11,12], which are well below the supply that minimizes the energy per operation, typically in the range of 200 to 350 mV. The minimum energy per operation point may be the ideal condition for the active operation of a circuit [2], but this is not the case for circuits with long standby times. In effect for such circuits the power spent can be minimized by setting the supply voltage to its lowest possible value in the standby mode [12].

Supply voltage constrained applications are those powered from the aforementioned very low voltage harvesters, given that no higher voltage sources are available. Then, supply voltage reduction techniques should be developed to provide functional circuits within those levels. In particular, for digital circuits, supply voltage reduction beyond the minimum energy per operation point are advantageous and can help to considerably reduce standby power consumption [12]. This is

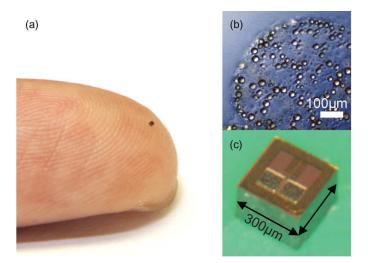

Figure 1.2: (a) Transmitter on fingertip and (b) *Thiomargarita namibiensis*, at the same scale with (c) die photo. Figure taken from [13].

so, even though most efforts are made towards the minimum energy per operation point and near threshold design [2]. In [12], Schmitt trigger gates were proven to be more efficient than CMOS gates for 75 mV supply, with respect to power/delay.

Due to the positive feedback, the Schmitt trigger provides a significant gain for voltages below 4kT/q, approximately 100 mV at room temperature. This feature could enable CMOS electronics operating from such voltage levels. Practical ultra low voltage levels would be 5kT/q for analog RF circuits [13] and 4kT/q for digital circuits [14]. In [13], the miniaturization of an RF transmitter compatible with bio-potential energy harvesting sources around 5kT/q is addressed. Figure 1.2 shows the SoC on a finger tip, together with a photo of the die and some vacuoles (Thiomargarita namibiensis) as a possible source of energy.

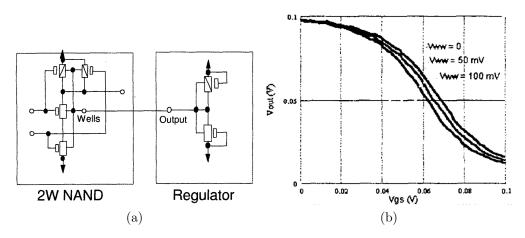

To obtain functional digital circuits at ultra low voltage levels, the threshold voltage of nMOS and pMOS devices may be matched by means of a simple regulator circuit [14]. Figure 1.3a shows a NAND gate connected to the regulator circuit. The voltage transfer characteristic of the NAND gate can be modified by adjusting the well bias, as shown in Fig. 1.3b. Additionally, for circuits powered from low voltage energy harvesters, reducing the minimum supply voltage required by the electronics simplifies the design of the voltage step-up converters.

Besides the digital circuits, all kinds of building blocks able to work with such voltage levels are required. Examples of circuits developed to this aim are a 75 mV 71 nW fully-integrated temperature sensor [15] and a 0.18 V 382 µW BLE receiver front-end with 1.33 nW sleep power [4].

Time-keeping functionality is required in IoT systems. Synchronization between nodes in a wireless sensors network (WSN) is vital in order to keep the exchange of coordination messages to the minimum [1]. In addition, the time-keeping module is likely to be always on.

When it comes to ultra low voltage oscillators capable of operating at tens of mV, inductively loaded ring oscillators and Colpitts oscillators may be suita-

### Chapter 1. Introduction

Figure 1.3: Well biasing technique to enable digital circuits at 4kT/q supply voltage: (a) circuit schematic showing a NAND and the regulator circuit to bias the wells, and (b) voltage transfer characteristic of circuit in (a). Figures taken from [14].

ble choices for the 100 MHz range [16]. To fulfill the low voltage budget, these oscillators are implemented with zero-VT transistors and high quality factor inductors. The latter might be either external inductors or on chip, area demanding, inductors. Without these, not only the voltage supply and current consumption would have to be increased to enable starting up, but also the performance of the oscillator would worsen.

A relaxation oscillator for time-keeping operating in the Hz-range from 0.3 V to 1.8 V with 3.32 pW has been reported in [17]. Maybe due to the very low power consumption achieved, it exhibits a high frequency spread (8.9 %) and a poor long term stability (<1 000 ppm). In the kHz-range, another relaxation oscillator [18] operates with 0.4 V and 1.14 nW and has 60 Hz variation over the range from 0.4 V to 0.65 V. It accomplishes a frequency stability of 94 ppm/°C and an Allan deviation floor of 58 ppm, which are remarkable considering it being the relaxation type. Nevertheless, RF communications synchronization applications demand better frequency stability and accuracy [1]. A cross-coupled LC-tank Voltage Controlled Oscillator (LC-VCO) with very low phase noise and frequency stability features was presented in [19]. This LC-VCO operates with 0.3 V at 3 579 MHz, but consumes 0.225 mW owing to the high frequency, making it unsuitable for the aforementioned applications.

Crystal oscillators have proven to be useful for low power time-keeping applications, and supply voltage lowering a convenient strategy [3, 20, 21]. Crystal oscillators operating in the range of tens of MHz shall attain  $\mu$ W-power consumption by means of a low supply voltage of 0.7 V in [22] and between 0.3 and 0.5 V in [23, 24].

In [25], a 0.15 V 32 kHz crystal oscillator is presented. A very low power consumption of 1.89 nW and a fine frequency stability performance are accomplished using a self-charging scheme. However, the output waveform is deformed possibly jeopardizing the frequency spectrum of the oscillator. A one-pin oscillator (instead

of two pins) based on the same scheme, but with 0.25 V and 2.89 nW, was reported in [26].

A 32 kHz phase locked loop (PLL) assisted crystal oscillator working within hundreds of mV supply and a remarkable performance is reported in [27], involving additional complex circuits and consequently a large amount of silicon area. Moreover, two different supply sources are required.

Regarding ultra low voltage 32 kHz crystal oscillators, the lowest power consumption is that reported in [28], attaining 0.55 nW by means of downconverting the signal to DC, amplifying in DC and then upconverting the signal to the frequency of the crystal. An excellent phase synchronization is achieved providing excellent frequency stability over temperature and over time. The output waveform is the result of switching DC levels to obtain a four level switched signal, which will have important harmonic content. The output harmonic content would be filtered by the high quality factor of the crystal. Nevertheless, this might be an issue if spectral purity is needed. Other examples in the single digit nW range are those reported in [29], [30] and [31].

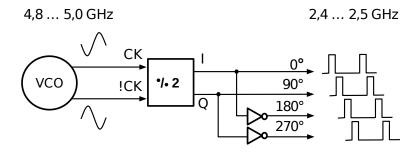

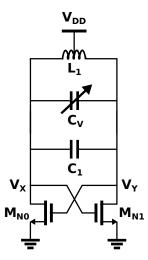

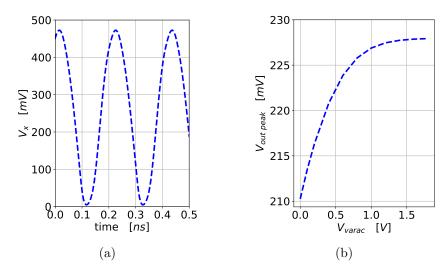

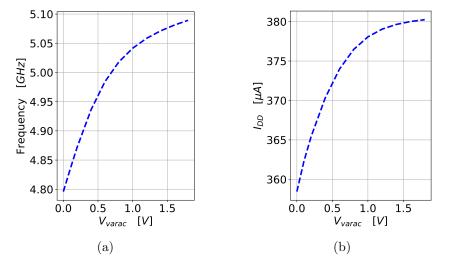

This thesis is organized as follows. The Schmitt trigger circuit topology, which is extensively referred to in this thesis, will be presented in Chapter 2. In the first place, the long-channel MOS transistor model used herein and the procedure for the extraction of the parameters of the transistor, are revisited. Then, the smallsignal low-frequency model of the Schmitt trigger and its operation as an amplifier for ultra low voltage are also revisited. Finally, a brief comparison between the Schmitt trigger and a CMOS inverter is presented. Chapter 3 is dedicated to the dynamic model of the Schmitt trigger, including the capacitive coefficients due to intrinsic and extrinsic capacitances, the intrinsic transition frequency and the main parameters to describe its operation in the region with hysteresis. The dynamic model is verified through simulations. In Chapter 4, the design of two crystal oscillators is assessed. Firstly, the operation of the Pierce oscillator is revisited. Secondly, the particulars of the design of a Pierce oscillator based on a Schmitt trigger as an amplifier are presented. In Chapter 5, the design and performance of the oscillator are verified through simulations and measurements. Finally, Chapter 6 deals with an LC-VCO for RF applications in a 28 nm Fully Depleted Silicon on Insulator (FD-SOI) technology. First, the model and parameter extraction procedure explained in Chapter 2 are translated to the present circuit and FD-SOI technology. Then, a non-tuneable version of the LC oscillator that operates at the minimum possible supply voltage is studied. The performance of the LC oscillator under this condition is obtained through simulations. Finally, an LC-VCO is optimally designed for the frequency band from 2.4 GHz to 2.5 GHz to minimize the power consumption by means of a low-voltage strategy. The performance of the LC-VCO is obtained through simulations. Finally in Chapter 7 the conclusions of this thesis are drawn.

# Chapter 2

# Schmitt trigger as an amplifier for ultra low voltage

To design a Schmitt trigger circuit to operate as an amplifier, a small-signal model is used and presented in this chapter. First, a basic all-region MOSFET model is revisited in Section 2.1. Then, expressions for the small-signal transconductances and the capacitive coefficients are provided in Sections 2.2 and 2.3. The equations within the model require the parameters of the technology of use. Thus, a parameter extraction procedure is followed as presented in Section 2.4. The DC transfer characteristic of the Schmitt trigger is subject of Section 2.5, where analytic expressions for obtaining the characteristic are provided. The low-frequency small-signal equivalent model of the Schmitt trigger is derived in Section 2.6 using the MOSFET model aided by the extracted parameters. Finally, the Schmitt trigger is compared to a CMOS inverter to see the benefits of using a Schmitt trigger circuit in ultra low voltage applications through numerical examples.

## 2.1 Basic all-region MOSFET model

In this section an all-region MOSFET model [32] is briefly reviewed.

The drain current of a long-channel transistor is expressed as the difference between two currents, namely, the forward and reverse currents,  $I_F$  and  $I_R$ , respectively, as follows

$$I_D = I_F - I_R = I_S(i_f - i_r),$$

(2.1)

where  $I_S$  (called specific current) is given by

$$I_S = \mu \, n \, C'_{ox} \, \frac{\phi_t^2}{2} \, \frac{W}{L} \tag{2.2}$$

and  $i_f$  and  $i_r$  are the forward and reverse inversion coefficients, respectively.

In (2.2),  $\mu$  is the mobility, n is the slope factor,  $C'_{ox}$  is the oxide capacitance per unit area,  $\phi_t$  is the thermal voltage and W/L is the aspect ratio.

### Chapter 2. Schmitt trigger as an amplifier for ultra low voltage

The specific current is normalized to the aspect ratio, leading to the specific current of an equivalent square transistor  $I_{SQ}$ , with W = L, giving

$$I_{SQ} = \frac{I_S}{W/L}. (2.3)$$

The forward and reverse currents in (2.1) relate to the normalized inversion charge density at source and drain,  $q'_{IS}$  and  $q'_{ID}$ , respectively, as follows

$$I_{F(R)} = I_S \left[ q_{IS(D)}^{\prime 2} + 2q_{IS(D)}^{\prime} \right], \tag{2.4}$$

where  $q'_{IS}$  and  $q'_{ID}$  are defined in terms of the inversion charge per unit area  $Q'_{IS}$  and  $Q'_{ID}$ , such that

$$q'_{IS(D)} = -\frac{Q'_{IS(D)}}{nC'_{cor}\phi_t}. (2.5)$$

The relationship between the terminal voltages  $V_G$ ,  $V_S$ ,  $V_D$  (all referred to the bulk) and the charge densities is

$$\frac{V_P - V_{S(D)}}{\phi_t} = q'_{IS(D)} - 1 + \ln\left(q'_{IS(D)}\right),\tag{2.6}$$

where the pinch-off voltage  $V_P$  can be approximated by

$$V_P \cong \frac{V_G - V_{T0}}{n},\tag{2.7}$$

being  $V_{T0}$  the threshold voltage at  $V_S = 0$ .

Expressing the inversion coefficients in terms of the normalized inversion charge, results in

$$i_{f(r)} = [q'_{IS(D)} + 1]^2 - 1.$$

(2.8)

Note that  $i_f$  does not depend on  $q'_{ID}$  and  $i_r$  does not depend on  $q'_{IS}$ .

Thus, (2.6) can be rewritten in terms of the inversion coefficients in (2.8) as follows

$$\frac{V_P - V_{S(D)}}{\phi_t} = \sqrt{1 + i_{f(r)}} - 2 + \ln\left(\sqrt{1 + i_{f(r)}} - 1\right). \tag{2.9}$$

## 2.1.1 Weak inversion model of the MOSFET

Deep in weak inversion (WI),  $i_{f(r)} \to 0$ . In this condition, the square root term in  $i_{f(r)}$  becomes negligible and we can approximate the logarithmic term using that  $\sqrt{1+x} \approx 1 + \frac{x}{2}$  in (2.9), resulting in

$$\frac{V_P - V_{S(D)}}{\phi_t} = -1 + \ln\left(\frac{i_{f(r)}}{2}\right). \tag{2.10}$$

Substituting (2.10) into (2.1) and using the pinch-off voltage approximation in (2.7), it follows the expression of the drain current  $I_D$  for the nMOS transistor operating in WI

$$I_{DN} = I_N e^{\frac{V_{GB}}{n_N \phi_t}} \left( e^{-\frac{V_{SB}}{\phi_t}} - e^{-\frac{V_{DB}}{\phi_t}} \right),$$

(2.11)

where the current scaling factor  $I_N$ , which represents the transistor current strength, is given by

$$I_N = 2 I_{SN} e^{1 - \frac{V_{T0N}}{n_N \phi_t}}. (2.12)$$

The expression for the pMOS current is obtained from (2.11) changing  $V_{SB}$  by  $V_{BS}$ ,  $V_{DB}$  by  $V_{BD}$  and  $V_{GB}$  by  $V_{BG}$ . The expression for the current strength of the pMOS transistor,  $I_P$ , is the same as (2.12), using the pMOS parameters.

# 2.2 Small-signal transconductances

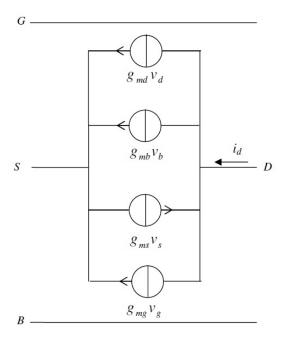

Provided that the MOSFET is a four terminal device, an increase in the voltage of these terminals translates to an increase in the drain current. Thus,

$$\Delta I_D = g_{mq} \Delta V_G - g_{ms} \Delta V_S + g_{md} \Delta V_D + g_{mb} \Delta V_B \tag{2.13}$$

where

$$g_{mg} = \frac{\partial I_D}{\partial V_G}, g_{ms} = -\frac{\partial I_D}{\partial V_S}, g_{md} = \frac{\partial I_D}{\partial V_D}, g_{mb} = \frac{\partial I_D}{\partial V_B}$$

(2.14)

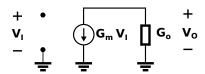

are the gate, source, drain and bulk transconductances, respectively. Figure 2.1 depicts the circuit schematic of this low-frequency small-signal model.

An expression for  $g_{ms}$  and  $g_{md}$  can be deduced from their definition in (2.14) and from the definition of the drain current in (2.1), giving

$$g_{ms(d)} = -(+)I_S \frac{\partial (i_f - i_r)}{\partial V_{S(D)}} = -I_S \frac{\partial i_{f(r)}}{\partial V_{S(D)}}.$$

(2.15)

Figure 2.1: Low-frequency small-signal model of the MOSFET. Figure taken from [32].

### Chapter 2. Schmitt trigger as an amplifier for ultra low voltage

From (2.9) it can be obtained an expression for the derivative  $(\partial i_{f(r)}/\partial V_{S(D)})$ . Thus, (2.15) becomes

$$g_{ms(d)} = \frac{2I_S}{\phi_t} \left( \sqrt{1 + i_{f(r)}} - 1 \right).$$

(2.16)

The expression for  $g_{mg}$  can be deduced from its definition in (2.14) and from (2.1), giving

$$g_{mg} = I_S \frac{\partial (i_f - i_r)}{\partial V_G}. (2.17)$$

Noting from (2.9) that

$$\frac{\partial i_{f(r)}}{\partial V_P} = -\frac{\partial i_{f(r)}}{\partial V_{S(D)}},\tag{2.18}$$

equation (2.17) can be rewritten as

$$g_{mg} = I_S \frac{\partial V_P}{\partial V_G} \left( -\frac{\partial i_f}{\partial V_S} + \frac{\partial i_r}{\partial V_D} \right). \tag{2.19}$$

Using the expression for  $g_{ms}$  and  $g_{md}$  in (2.16), and the definition of  $V_P$  in (2.7),  $g_{mg}$  reduces to

$$g_{mg} = \frac{g_{ms} - g_{md}}{n}. (2.20)$$

The bulk transconductance  $g_{mb}$  can be derived from (2.13) by noting that, if the four terminals of the MOSFET increase the voltage by the same amount,  $\Delta I_D = 0$ , thus

$$q_{ma} - q_{ms} + q_{md} + q_{mb} = 0. (2.21)$$

From (2.20) and (2.21),  $g_{mb}$  reduces to

$$g_{mb} = (n-1)g_{mq}. (2.22)$$

## 2.3 Capacitive coefficients

All charges  $Q_j$  (j = G, S, D, B) can be expressed in terms of the instantaneous values of the terminal voltages, by applying the chain rule of differentiation, obtaining an expression for the charging currents as

$$\frac{\partial Q_j}{\partial t} = \frac{\partial Q_j}{\partial V_G} \frac{\partial V_G}{\partial t} + \frac{\partial Q_j}{\partial V_S} \frac{\partial V_S}{\partial t} + \frac{\partial Q_j}{\partial V_D} \frac{\partial V_D}{\partial t} + \frac{\partial Q_j}{\partial V_B} \frac{\partial V_B}{\partial t}.$$

(2.23)

The four-by-four matrix of the MOSFET intrinsic capacitances for quasi-static operation is defined by [33]

$$C_{jk} = -\frac{\partial Q_j}{\partial V_k} \bigg|_{0}, \quad j \neq k,$$

(2.24)

$$C_{jj} = \frac{\partial Q_j}{\partial V_j} \bigg|_0, \tag{2.25}$$

where  $Q_j$  can be any one of the charges  $Q_S$ ,  $Q_D$ ,  $Q_B$  or  $Q_G$ , and  $V_j$  and  $V_k$  can be any of the voltages  $V_S$ ,  $V_D$ ,  $V_B$ , and  $V_G$ . The notation "0" indicates that the derivatives are calculated at the bias point.  $C_{jk}$  determines the current transferred out of node j because of a voltage change on node k, all the other node voltages remaining constant.

Because the MOSFET is an active device, the capacitances  $C_{jk}$  are non-reciprocal, that is, in general,  $C_{jk} \neq C_{kj}$  for  $j \neq k$ . Only 9 of the 16 capacitive coefficients are linearly independent, due to charge conservation and the fact that only three voltage differences from four terminal voltages can be chosen independently.

From the expressions for the MOSFET charges, explicit formulas for the capacitive coefficients can be derived from (2.23) and (2.24). Thus,

$$C_{gs} = \frac{2}{3}C_{ox}\frac{1+2\alpha}{(1+\alpha)^2}\frac{q'_{IS}}{1+q'_{IS}},$$

(2.26a)

$$C_{gd} = \frac{2}{3} C_{ox} \frac{\alpha^2 + 2\alpha}{(1+\alpha)^2} \frac{q'_{ID}}{1 + q'_{ID}},$$

(2.26b)

$$C_{bs(d)} = (n-1) C_{gs(d)},$$

(2.26c)

$$C_{gb} = C_{bg} = \frac{(n-1)}{n}(C_{ox} - C_{gs} - C_{gd}),$$

(2.26d)

$$C_{sd} = -\frac{4}{15}nC_{ox}\frac{\alpha + 3\alpha^2 + \alpha^3}{(1+\alpha)^3}\frac{q'_{ID}}{1 + q'_{ID}},$$

(2.26e)

$$C_{ds} = -\frac{4}{15}nC_{ox}\frac{1+3\alpha+\alpha^2}{(1+\alpha)^2}\frac{q'_{IS}}{1+q'_{IS}},$$

(2.26f)

$$C_{dg} - C_{gd} = C_m = \frac{C_{sd} - C_{ds}}{r},$$

(2.26g)

where

$$C_{ox} = WLC'_{ox}, (2.27)$$

and

$$\alpha = \frac{q'_{ID} + 1}{q'_{IS} + 1}. (2.28)$$

## 2.4 Parameter extraction

The all-region model in 2.1 is the basic long channel compact model applied to extract the parameters of the transistors.

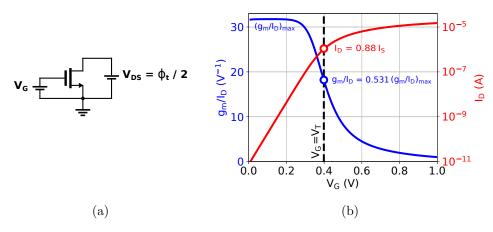

For parameter extraction, the  $g_m/I_D$  based procedure described in [34] is followed, where the authors propose to extract the parameters n,  $V_{T0}$  and  $I_S$  using  $V_S = 0$ ,  $V_D = \phi_t/2$ , sweeping  $V_G$  (as shown in Fig. 2.2a) and plotting  $I_D$  and  $g_m/I_D$  with respect to  $V_G$  (as shown in Fig. 2.2b).

From (2.20), the  $g_m/I_D$  ratio can be expressed as

$$\frac{g_m}{I_D} = \frac{1}{I_D} \frac{\partial I_D}{\partial V_G} = \frac{g_{ms} - g_{md}}{nI_D}.$$

(2.29)

Figure 2.2: (a) Circuit schematic and (b) graphical representation of the  $g_m/I_D$  procedure for the extraction of  $V_T$ .

Using the expressions for  $g_{ms}$  and  $g_{md}$  in (2.16),  $g_m/I_D$  in (2.29) simplifies to

$$\frac{g_m}{I_D} = \frac{2}{n\phi_t \left(\sqrt{1 + i_f} + \sqrt{1 + i_r}\right)}. (2.30)$$

The extraction of the parameters is then based on the following relationships. The maximum value of  $g_m/I_D$  (for  $i_f = i_r = 0$ ) is  $1/(n\phi_t)$ .

For  $V_S=0$  and  $V_G=V_T$  (which implies  $V_P=0$ ), we obtain  $i_f=3$  from (2.9). For  $V_{DS}=\phi_t/2$ ,  $V_S=0$  and  $V_G=V_T$  we obtain  $i_r=2.12$  from (2.9). For these values of  $i_f$  and  $i_r$ , we have  $g_m/I_D=0.531/\left(n\phi_t\right)$  from (2.30) and  $I_D=0.88I_S$  from (2.1).

So the parameters are extracted as follows. First,  $n=1/(\phi_t (g_m/I_D)_{max})$ , then  $V_T$  such that  $g_m/I_D (V_G = V_T) = 0.531/(n\phi_t)$  is determined and, finally,  $I_S = I_D (V_G = V_T)/0.88$ .

Even though an nMOS transistor is used to exemplify the extraction procedure, the parameters of a pMOS transistor are extracted in the same way but with  $V_{SD} = \phi_t/2$ . Once the extraction is completed, the designer can choose the dimensions of a transistor to match certain parameters. Moreover, by using series and parallel arrangements of unit transistors, one can have an equivalent transistor, build of many transistors in series or in parallel, with the exact same parameters as each of the unit transistors [35].

## 2.5 DC transfer characteristic of the Schmitt trigger

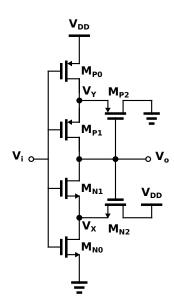

The Schmitt trigger topology is shown in Fig. 2.3. The bulk of the nMOS and pMOS transistors are connected to ground and  $V_{DD}$ , respectively.

In ultra low voltage operation, both nMOS and pMOS are in the WI region. The MOS transistor drain current in WI is given by (2.11) and rewritten here for

Figure 2.3: Six transistor Schmitt trigger circuit schematic.

convenience. Thus,

$$I_{DN} = I_N e^{\frac{V_{GB}}{n_N \phi_t}} \left( e^{-\frac{V_{SB}}{\phi_t}} - e^{-\frac{V_{DB}}{\phi_t}} \right),$$

(2.31)

where  $I_N$ , represents the transistor current strength, and is given in (2.12).

The expression for the pMOS current is obtained from (2.31) changing  $V_{SB}$  by  $V_{BS}$ ,  $V_{DB}$  by  $V_{BD}$  and  $V_{GB}$  by  $V_{BG}$ . The expression for the current strength of the pMOS transistor is the same as (2.12), using the pMOS parameters.

In order to design a Schmitt trigger, first the parameters of the transistor are extracted as explained in Section 2.4. The extracted parameters are then replaced in (2.31) to evaluate the drain current of each of the transistors. As a result, the remaining variables are exclusively currents and voltages. Moreover, the transistors may be sized to match certain parameters. The sizing of the transistors is discussed in Section 4.4 applied to the case of a Pierce oscillator using a Schmitt trigger as the inverting amplifier.

All transistors of the Schmitt trigger are composed of parallel arrangements of either nMOS or pMOS unit transistors. Thus, all of the parallel arrangements have the same  $V_T$ ,  $I_{SQ}$  and n as the unit transistor of choice [35]. This strategy significantly simplifies the calculations in circuits with many transistors.

The number of transistors in parallel must be such that every pMOS has the same current strength as its symmetric nMOS, that is,  $I_{N0} = I_{P0} = I_0$ ,  $I_{N1} = I_{P1} = I_1$ ,  $I_{N2} = I_{P2} = I_2$  and  $n_N = n_P = n$ .

Calculating the drain currents of the six transistors in Fig. 2.3 from (2.31), the DC equations for nodes  $V_X$  and  $V_Y$  are [36]

$$e^{\frac{V_X}{\phi_t}} = \frac{I_0 + I_1 + I_2 e^{\frac{V_O - V_I}{\phi_t}}}{I_0 + I_1 e^{-\frac{V_0}{\phi_t}} + I_2 e^{\frac{V_O - V_I}{\phi_t}} e^{-\frac{V_{DD}}{\phi_t}}},$$

(2.32)

### Chapter 2. Schmitt trigger as an amplifier for ultra low voltage

Figure 2.4: Output voltage  $V_O$  of the Schmitt trigger obtained from analytical expressions (2.32), (2.33) and (2.34), with  $I_1/I_0 = 0.25$  and  $I_2/I_0 = 0.5$ .

and

$$e^{\frac{V_Y}{\phi_t}} = \frac{I_0 e^{\frac{V_{DD}}{\phi_t}} + I_1 e^{\frac{V_O}{\phi_t}} + I_2 e^{\frac{V_I - V_O}{\phi_t}}}{I_0 + I_1 + I_2 e^{\frac{V_I - V_O}{\phi_t}}},$$

(2.33)

where  $n_N = n_P = 1$  for simplicity. The DC equation for node  $V_O$  is given by

$$e^{\frac{V_I - V_X}{\phi_t}} - e^{\frac{V_I - V_O}{\phi_t}} = e^{\frac{V_Y - V_I}{\phi_t}} - e^{\frac{V_O - V_I}{\phi_t}}.$$

(2.34)

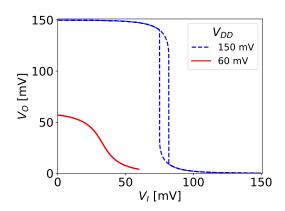

Figure 2.4 shows the voltage transfer characteristic of the Schmitt trigger, calculated from (2.32), (2.33) and (2.34). For  $V_{DD} = 150$  mV the voltage transfer characteristic presents hysteresis, but for  $V_{DD} = 60$  mV it does not.

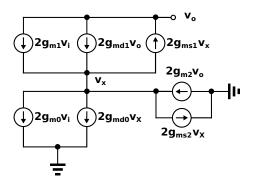

## 2.6 Low-frequency small signal equivalent model of the Schmitt trigger

The equivalent small-signal model of the Schmitt trigger is depicted in Fig. 2.5. The transconductances present in Fig. 2.5 follow the definition in (2.14) and are evaluated around the operating point  $V_I = V_O = V_{DD}/2$ , giving

$$g_{mk} = -\frac{\partial I_{DN}}{\partial V_{GB}}\bigg|_{V_r = V_O = V_{DD}/2}, \tag{2.35a}$$

$$g_{mdk} = \frac{\partial I_{DN}}{\partial V_{DB}} \bigg|_{V_t = V_O = V_{DD}/2}, \tag{2.35b}$$

$$g_{mk} = \frac{\partial I_{DN}}{\partial V_{GB}}\Big|_{V_I = V_O = V_{DD}/2}, \qquad (2.35a)$$

$$g_{mdk} = \frac{\partial I_{DN}}{\partial V_{DB}}\Big|_{V_I = V_O = V_{DD}/2}, \qquad (2.35b)$$

$$g_{msk} = -\frac{\partial I_{DN}}{\partial V_{SB}}\Big|_{V_I = V_O = V_{DD}/2}, \qquad (2.35c)$$

where  $g_{mk}$ ,  $g_{mdk}$  and  $g_{msk}$ , are the gate, drain and source transconductances of transistor k, respectively. The values of the transconductances, according to (2.35), are given in Table 2.1.

### 2.6. Low-frequency small signal equivalent model of the Schmitt trigger

Figure 2.5: Six transistor Schmitt trigger circuit low-frequency small-signal equivalent model for  $V_I = V_O = V_{DD}/2$ .

Table 2.1: Transconductances of the Schmitt trigger

|                     | $g_m$                                                                                                                                        | $g_{ms}$                                                                                          | $g_{md}$                                                                                           |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| $M_{N0},$ $M_{P0}$  | $\frac{I_0}{n\phi_t} \left[ \frac{1 - e^{-\frac{V_{X0}}{\phi_t}}}{e^{-\frac{V_{DD}}{2n\phi_t}}} \right]$                                     |                                                                                                   | $\frac{I_0}{\phi_t} \left[ \frac{e^{\frac{V_{DD}}{2n\phi_t}}}{e^{\frac{V_{X0}}{\phi_t}}} \right]$  |

| $M_{N1}$ , $M_{P1}$ | $\frac{I_{1}}{n\phi_{t}} \left[ \frac{e^{-\frac{V_{X0}}{\phi_{t}}} - e^{-\frac{V_{DD}}{2\phi_{t}}}}{e^{-\frac{V_{DD}}{2n\phi_{t}}}} \right]$ | $\frac{I_1}{\phi_t} \left[ \frac{e^{\frac{V_{DD}}{2n\phi_t}}}{e^{\frac{V_{X0}}{\phi_t}}} \right]$ | $\frac{I_1}{\phi_t} \left[ \frac{e^{\frac{V_{DD}}{2n\phi_t}}}{e^{\frac{V_{DD}}{2\phi_t}}} \right]$ |

| $M_{N2}$ , $M_{P2}$ | $\frac{I_2}{n\phi_t} \left[ \frac{e^{-\frac{V_{X0}}{\phi_t}} - e^{-\frac{V_{DD}}{\phi_t}}}{e^{-\frac{V_{DD}}{2n\phi_t}}} \right]$            | $\frac{I_2}{\phi_t} \left[ \frac{e^{\frac{V_{DD}}{2n\phi_t}}}{e^{\frac{V_{X0}}{\phi_t}}} \right]$ |                                                                                                    |

The equivalent small-signal model of the Schmitt trigger in Fig. 2.5, looks like the nMOS network small-signal model, but all transconductance values are doubled.

The Schmitt trigger can be represented by an equivalent transconductance  $G_m$  and an equivalent output conductance  $G_o$  [37]

$$G_m = \frac{i_o}{v_i} \bigg|_{V_I = V_O = V_{DD}/2} = -2 \times \frac{g_{m1}(g_{ms2} + g_{md0}) + g_{ms1}g_{m0}}{g_{ms1} + g_{ms2} + g_{md0}},$$

(2.36)

and

$$G_o = \frac{i_o}{v_o} \Big|_{V_I = V_O = V_{DD}/2} = -2 \times \frac{g_{md1}(g_{ms2} + g_{md0}) - g_{ms1}g_{m2}}{g_{ms1} + g_{ms2} + g_{md0}}.$$

(2.37)

The equivalent transconductance  $G_m$  can be rewritten in terms of the supply

### Chapter 2. Schmitt trigger as an amplifier for ultra low voltage

Figure 2.6: Circuit schematic of the small-signal equivalent model of a Schmitt trigger as an amplifier.

Figure 2.7: Voltage gain as a function of  $I_1/I_0$  and  $I_2/I_0$  given by (2.40), with n=1.3 and  $V_{DD}=60\,mV$ , based on [37].

voltage,  $V_{DD}$ , and the current strengths,  $I_0$ ,  $I_1$  and  $I_2$ , as follows

$$G_m = \frac{2I_1/n}{e^{-V_{DD}/2n\phi_t}} \left[ \frac{(I_0 + I_2)e^{-V_{DD}/2\phi_t} - I_2e^{-V_{X0}/\phi_t}}{I_0 e^{(V_{X0} - V_{DD})/\phi_t} + I_1 + I_2} \right], \tag{2.38}$$

where  $V_{X0}$ , the value of  $V_X$  at  $V_I = V_O = V_{DD}/2$ , is such that

$$e^{-V_{X0}/\phi_t} = \frac{I_0 + I_1 e^{-V_{DD}/2\phi_t} + I_2 e^{-V_{DD}/\phi_t}}{I_0 + I_1 + I_2}.$$

(2.39)

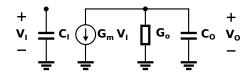

Figure 2.6 depicts the schematic of the small-signal equivalent model of the Schmitt trigger as an amplifier, with  $G_m$  and  $G_o$  the equivalent transconductance and output conductance in (2.36) and (2.37), respectively.

Lastly, the Schmitt trigger voltage gain is expressed as

$$A = \frac{v_o}{v_i} \Big|_{V_I = V_O = V_{DD}/2} = -\frac{G_m}{G_o}.$$

(2.40)

The voltage gain A is a function of the supply voltage  $V_{DD}$ , the ratios  $I_1/I_0$  and  $I_2/I_0$ , and the slope factor of nMOS and pMOS devices  $n_N$  and  $n_P$  (considered equal for the sake of simplicity, without loss of generality, thus:  $n = n_N = n_P$ ).

Figure 2.7 shows the dependence of the voltage gain on  $I_2/I_0$ , for constant values of  $I_1/I_0$  and supply voltage  $V_{DD} = 60$  mV. We have chosen this ultra low

### 2.7. Comparison between Schmitt trigger and CMOS inverter

voltage to explore the frontier of the design space. A practical ultra low voltage complex circuit should operate with a minimum supply of 100 mV as explained in the introduction. For values of  $I_2/I_0$  close to 0.5, independently of the ratio  $I_1/I_0$ , the maximum absolute gain is reached. Therefore,  $I_2/I_0 = 0.5$  is chosen. On the other hand, the lower the ratio  $I_1/I_0$ , the larger the magnitude of the voltage gain.  $I_1/I_0 = 0.25$  is chosen for the sake of layout simplicity. In this case, the voltage gain is A = -2.48 V/V.

As a consequence, after  $V_{DD}$ ,  $I_1/I_0$  and  $I_2/I_0$  have been selected and n is given by the process chosen,  $G_m$  and  $G_o$  can be expressed only in terms of the current strength  $I_0$ .

# 2.7 Comparison between Schmitt trigger and CMOS inverter

Hysteresis is the most distinguishing characteristic of a Schmitt trigger circuit, when comparing it to a CMOS inverter. As shown in [36], the minimum supply voltage to obtain hysteresis in a Schmitt trigger with balanced pMOS and nMOS subcircuits is given by

$$V_{DDH} \approx 2\phi_t \ln \left[ n \left( 1 + \frac{I_0}{I_2} \right) \left( 1 + \frac{I_1}{I_0} + \frac{I_2}{I_0} \right) - \frac{I_1}{I_0} \right].$$

(2.41)

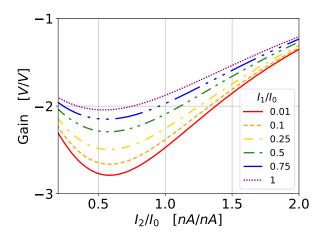

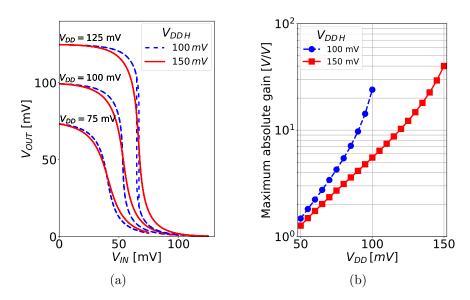

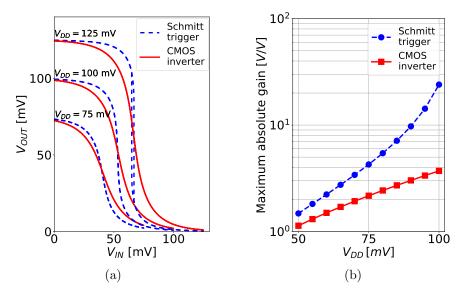

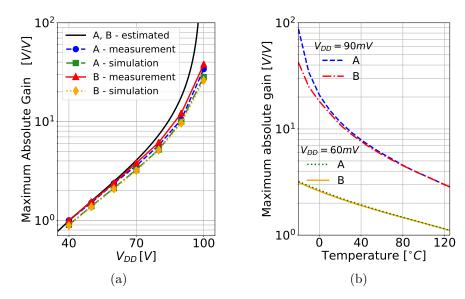

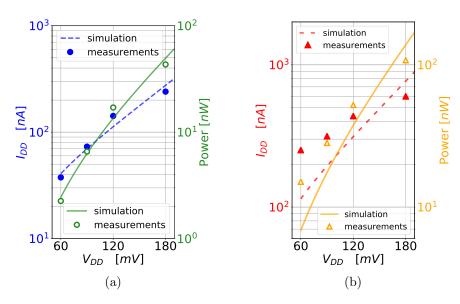

Figures 2.8a and 2.8b show the voltage transfer characteristic and the maximum absolute gain, respectively, of two Schmitt triggers, one with  $V_{DDH}=100~\mathrm{mV}$  and the other with  $V_{DDH}=150~\mathrm{mV}$ .

Note that the maximum absolute gain increases until hysteresis appears at a certain level, herein  $V_{DDH}$ . It can be seen that, for the same supply voltage  $V_{DD}$ , the Schmitt trigger that exhibits hysteresis at a lower voltage consistently has a higher maximum absolute gain. The value of  $V_{DDH}$  depends on the values of  $I_0$ ,  $I_1$  and  $I_2$ , and thus is chosen during the design.  $I_0 = 70$  nA,  $I_1 = 2.8$  nA and  $I_2 = 25$  nA give  $V_{DDH} = 100$  mV, while  $I_0 = 46$  nA,  $I_1 = 7.4$  nA and  $I_2 = 4.6$  nA give  $V_{DDH} = 150$  mV.

On the other hand, Figures 2.9a and 2.9b let us compare the gain of a CMOS inverter to the gain of a Schmitt trigger, as a function of  $V_{DD}$ . The Schmitt trigger exhibits a much higher maximum absolute gain. Thus, for a given supply voltage it is possible to design a Schmitt trigger with maximum absolute gain much higher than that of a CMOS inverter.

## Chapter 2. Schmitt trigger as an amplifier for ultra low voltage

Figure 2.8: (a) Voltage transfer characteristic of two Schmitt triggers designed to exhibit hysteresis at different supply voltages,  $V_{DDH}$ , and (b) their maximum absolute gain as a function of the supply voltage  $V_{DD}$ .

Figure 2.9: (a) Voltage transfer characteristic of a Schmitt trigger with  $V_{DDH}=100~\rm mV$  and of a CMOS inverter and (b) their maximum absolute gain as a function of the supply voltage  $V_{DD}$ .

# Chapter 3

# Schmitt trigger dynamic model

Besides the low-frequency small-signal model presented in Section 2.6, a dynamic model requires insight on the circuit behaviour in the frequency domain. In this chapter, the capacitive coefficients of the transistors are calculated and a model with an equivalent input and output capacitances is proposed. The transition frequency is also derived, completing the model for the Schmitt trigger operating as an amplifier. Afterwards, the key parameters of the operation of the Schmitt trigger with hysteresis are also estimated. These are, the thresholds of the hysteresis and the step response. The model is verified through simulations.

# 3.1 Capacitive coefficients

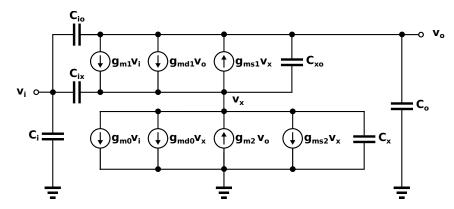

Here the capacitive coefficients for the nMOS network only are considered. Later, the results are extended to the entire Schmitt trigger. Figure 3.1 presents the small-signal equivalent model for high-frequency operation, including both transconductances and parasitic capacitances.

In WI the intrinsic capacitances, other than the gate-bulk capacitance  $C_{qb}$ , are

Figure 3.1: nMOS network of the six transistor Schmitt Trigger circuit. High-frequency small-signal equivalent model for  $V_I=V_O=V_{DD}/2$ , accounting for parasitic capacitances.

#### Chapter 3. Schmitt trigger dynamic model

negligible. This can be verified by deriving the expressions in WI for the intrinsic capacitances in (2.26a)-(2.26g), as follows. In WI,  $\alpha \approx 1$ ,  $1 + q'_{IS(D)} \approx 1$ , obtaining

$$C_{gs(d)} = \frac{C_{ox} \, q'_{IS(D)}}{2},$$

(3.1a)

$$C_{bs(d)} = \frac{(n-1) C_{ox} q'_{IS(D)}}{2},$$

(3.1b)

$$C_{sd} = -\frac{n \, C_{ox} \, q'_{ID}}{3},\tag{3.1c}$$

$$C_{ds} = -\frac{n \, C_{ox} \, q_{IS}'}{3},\tag{3.1d}$$

$$C_{gb} = C_{bg} = \frac{n-1}{n}(C_{ox} - C_{gs} - C_{gd}),$$

(3.1e)

$$C_{dg} = C_{gd} + (C_{sd} - C_{ds})/n,$$

(3.1f)

with  $q'_{IS(D)}$  much less than one. Consequently, all the intrinsic capacitances are negligible, except for  $C_{gb}$  and  $C_{bg}$  that can be approximated as

$$C_{gb} = C_{bg} \approx \frac{(n-1)}{n} C_{ox}.$$

(3.2)

Thus, the gate to bulk intrinsic capacitance of transistor k is given by

$$C_{gbk} = \left(\frac{n-1}{n}\right) W_k L_k C'_{ox},\tag{3.3}$$

where  $W_k$  and  $L_k$  are the width and length of transistor  $M_{Nk}$ , respectively.

On the other hand, the overlap and junction extrinsic capacitances are taken into consideration.

Each of the parasitic capacitances contribute to one of the equivalent capacitances in Fig. 3.1, giving

$$C_i = C_{s0\,ov} + C_{ab0} + C_{ab1}, \tag{3.4a}$$

$$C_x = C_{i0} + C_{i1} + C_{i2}, (3.4b)$$

$$C_{ix} = C_{d0 ov} + C_{s1 ov},$$

(3.4c)

$$C_o = C_{d2 ov} + C_{qb2} + C_{j1},$$

(3.4d)

$$C_{io} = C_{d1 ov}, (3.4e)$$

$$C_{xo} = C_{s2 ov}, \tag{3.4f}$$

where  $C_{pk\,ov}$  is the overlap capacitance at node p of transistor k and  $C_{Jk}$  is the extrinsic capacitance within the drain or source to bulk junction.

The extrinsic overlap capacitances of transistor k are expressed as

$$C_{sk ov} = C_{dk ov} = C'_{ox} W_k LD, (3.5)$$

being LD the overlapping distance.

Figure 3.2: Circuit schematic of the dynamic model of a Schmitt trigger as an amplifier.

For the sake of simplicity, the extrinsic junction capacitances are considered to be independent of any voltage variations, this is

$$C_{Jk} = C_J' \times A_{Sk}, \tag{3.6}$$

where  $C'_{J}$  and  $A_{Sk}$  are the junction capacitance per unit area and the drain or source diffusion area of transistor k, respectively.

Figure 3.2 depicts the schematic of the dynamic model of the Schmitt trigger as an amplifier, with  $G_m$  and  $G_o$  the equivalent transconductance and output conductance derived in Section 2.6 in (2.36) and (2.37), respectively. The equivalent input and output capacitances,  $C_I$  and  $C_O$ , can be expressed taking into consideration the Miller effect [38] as

$$C_I = C_i + C_{io} (1 + |A_{io}|) + C_{ix} (1 + |A_{ix}|),$$

(3.7)

$$C_O = C_o + C_{io} \left( 1 + \frac{1}{|A_{io}|} \right) + C_{xo} \left( 1 + \frac{|A_{ix}|}{|A_{io}|} \right),$$

(3.8)

where  $A_{io}$  and  $A_{ix}$  are the low frequency voltage gain between  $v_o$  and  $v_i$  and between  $v_x$  and  $v_i$ , respectively.  $A_{io}$  and  $A_{ix}$  can be expressed as

$$A_{io} = \frac{v_o}{v_i} \bigg|_{V_I = V_O = V_{DD}/2} = \frac{g_{m1}(g_{ms2} + g_{md0}) + g_{ms1}g_{m0}}{g_{md1}(g_{ms2} + g_{md0}) - g_{ms1}g_{m2}},$$

(3.9)

$$A_{ix} = \frac{v_x}{v_i} \bigg|_{V_I = V_O = V_{DD}/2} = \frac{g_{m1} - g_{m0}}{g_{ms1} + g_{md0} + g_{ms2} - g_{m2}},$$

(3.10)

being the transconductances those in Table 2.1.

Due to the symmetry of the Schmitt trigger circuit, each capacitive component within the pMOS network is modeled in parallel with the same component in the nMOS network. Thus, the capacitances of the Schmitt trigger shall be computed as those in the nMOS network times  $(1 + W_{pMOS}/W_{nMOS})$ , provided that the pMOS and nMOS transistors have the same channel length.

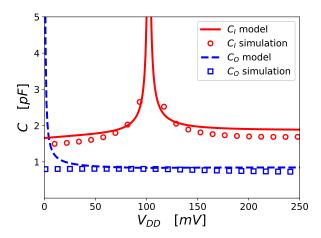

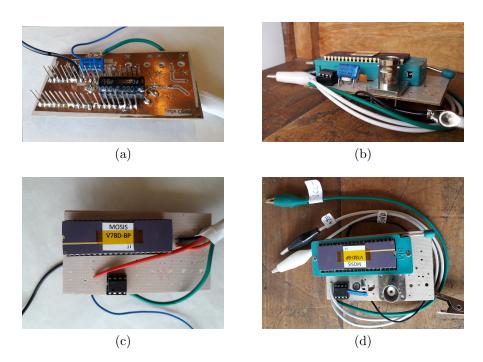

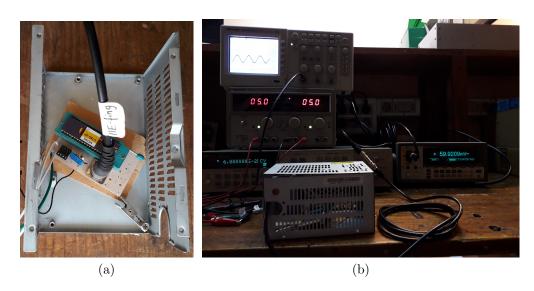

In order to verify the model, simulations were run based on the Schmitt trigger circuit designed to work as the inverting amplifier of one of the oscillators presented in Chapter 4. The dimensions of the transistors are shown in Table 3.1 for convenience.

The simulation results are presented in Fig. 3.3 and so are the analytical curves. At  $V_{DD} = V_{DDH}$ ,  $C_I$  curve presents a singularity, due to the appearance of hysteresis. An expression for  $V_{DDH}$  is provided in (2.41) and the main parameters of the Schmitt trigger with hysteresis are modeled and verified through simulations in Section 3.3.

#### Chapter 3. Schmitt trigger dynamic model

Table 3.1: Transistor dimensions of the Schmitt trigger circuit.

| $L_{N,P}$ | $W_{N0}$  | $W_{P0}$  | $W_{N1}$       | $W_{P1}$  | $W_{N2}$       | $W_{P2}$  |

|-----------|-----------|-----------|----------------|-----------|----------------|-----------|

| $[\mu m]$ | $[\mu m]$ | $[\mu m]$ | $[\mu m]$      | $[\mu m]$ | $[\mu m]$      | $[\mu m]$ |

| 1.08      | 8×5.1     | 8×53      | $2 \times 5.1$ | 2×53      | $4 \times 5.1$ | 4×53      |

Figure 3.3: Equivalent input and output capacitances as functions of the supply voltage,  $V_{DD}$ . The analytic curves follow the equations (3.7) and (3.8) and are contrasted to simulation results.

Furthermore in Fig. 3.3, the simulation results are well predicted by the model, not only in the amplifier region  $(V_{DD} < V_{DDH})$ , but also in the region with hysteresis  $(V_{DD} > V_{DDH})$ . This is due to the simulations being AC simulations and the model a linear one.

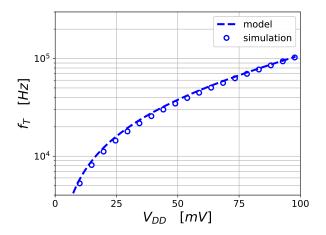

# 3.2 Intrinsic transition frequency

The transition frequency of the Schmitt Trigger is defined similarly to that of a single transistor [39]. Firstly, the short-circuit current gain magnitude  $a_i$  is defined as the ratio of the amplitude of the small-signal output current to the amplitude of the small-signal input current, this is

$$a_i = \frac{i_{out}}{i_{in}} = \frac{G_m}{2\pi f C_{IT}},\tag{3.11}$$

being  $G_m$  the equivalent transconductance of the Schmitt trigger in (2.36) and  $C_{IT}$  the total input capacitance. Note that  $C_{IT}$  is simply the sum of all the capacitances in the input node, since  $a_i$  is a current gain, in contrast to the voltage gain involved in the calculations of  $C_I$  and  $C_O$  in Section 3.1. Thus,

$$C_{IT} = C_i + C_{io} + C_{ix}. (3.12)$$

Figure 3.4: Transition frequency as a function of the supply voltage,  $V_{DD}$ , estimated analytically and contrasted to simulation results.

The intrinsic transition frequency  $f_T$ , is defined as the frequency at which  $a_i$  drops to the value of 1. This is

$$f_T = \frac{G_m}{2\pi C_{IT}},\tag{3.13}$$

where, according to (2.38),  $G_m$  can be expressed as

$$G_m = \frac{2I_1/n}{e^{-V_{DD}/2n\phi_t}} \left[ \frac{(I_0 + I_2)e^{-V_{DD}/2\phi_t} - I_2e^{-V_{X0}/\phi_t}}{I_0 e^{(V_{X0} - V_{DD})/\phi_t} + I_1 + I_2} \right].$$

(3.14)

Figure 3.4 shows the simulation results of the transition frequency and the analytic curve provided in (3.13). It is seen that the model fairly predicts the simulation results.

# 3.3 Schmitt trigger with hysteresis

As explained in Section 2.7, the minimum supply voltage to obtain hysteresis is provided in (2.41) and rewritten here for convenience

$$V_{DDH} \approx 2\phi_t \ln \left[ n \left( 1 + \frac{I_0}{I_2} \right) \left( 1 + \frac{I_1}{I_0} + \frac{I_2}{I_0} \right) - \frac{I_1}{I_0} \right].$$

(3.15)

The hysteresis width is approximated by [37]

$$V_L \approx \frac{(V_{DD} - 2V_{X0}) \left(1 - e^{V_{DDH} - V_{DD}}\right)}{2 + \frac{I_0}{I_2} + \frac{I_1}{I_2}},$$

(3.16)

provided that the transistors are in WI region. Owing to the symmetry of the circuit, the input value of the upper and lower thresholds of the hysteresis loop are

$$V_{TH\pm} = \frac{V_{DD}}{2} \pm \frac{V_L}{2}. (3.17)$$

#### Chapter 3. Schmitt trigger dynamic model

Figure 3.5: Thresholds of the hysteresis as a function of the supply voltage,  $V_{DD}$ , estimated analytically and contrasted to simulation results.

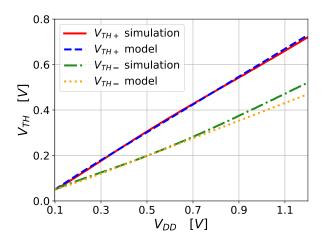

Figure 3.5 shows the model results obtained from (3.17) and the simulation results of  $V_{TH+}$  and  $V_{TH-}$  as a function of the supply voltage.

In the region with hysteresis, the response to a step from  $V_{DD}$  to zero is given by

$$v_o(t) = V_{DD} \left( 1 - e^{-t/\tau} \right),$$

(3.18)

with the time constant

$$\tau = R_O C_O \tag{3.19}$$

and the output resistance

$$R_O = \frac{V_O}{I_O} \bigg|_{V_I = 0}. (3.20)$$

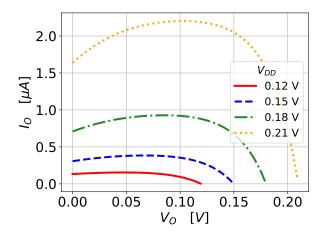

The output current  $I_O$  is calculated as the difference between the drain currents of transistors  $M_{N1}$  and  $M_{P1}$ , at  $V_I = 0$  V. The drain currents are  $I_{DN1}$  and  $I_{DP1}$ , respectively, and follow (2.1). The results of the output current predicted by the model are presented in Fig. 3.6, showing that the output current is highly dependent on the output voltage. Therefore, for each value of  $V_{DD}$  an approximation of the output current is required to estimate an equivalent resistance  $R_O$  and the time constant  $\tau$ . Thus, the mean value of the output current is chosen to this aim.

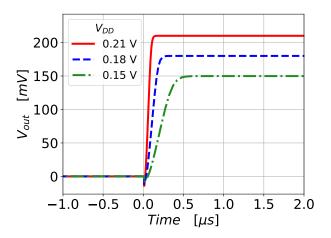

Figure 3.7 shows the transient simulation results of the step response for several values of  $V_{DD}$ . The time constant  $\tau$  is extracted from the rise time (between 10% and 90% of the final value  $V_{DD}$ ) of the step response in Fig. 3.7. It is seen that the rise time decreases with the supply voltage, as expected.

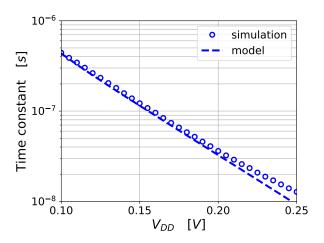

The time constant is calculated following (3.19). Thus, the results predicted by the equations are shown in Fig. 3.8 together with the simulation results.

Figure 3.6: Model results of the output current of the Schmitt trigger,  $I_O$ , at  $V_I=0~{\rm V}$ , as a function of the output voltage  $V_O$  and for several values of supply voltage  $V_{DD}$ .

Figure 3.7: Transient simulation results of the step response of the Schmitt trigger with hysteresis for several values of supply voltage  $V_{DD}$ .

## Chapter 3. Schmitt trigger dynamic model

Figure 3.8: Time constant  $\tau$  as a function of the supply voltage,  $V_{DD}$ , estimated analytically and contrasted to simulation results.

# Chapter 4

# Design of crystal oscillators

In this chapter, the basic concepts to fully understand the operation of the Pierce crystal oscillator are revisited. An amplifier, connected in parallel to a crystal resonator, compensates the losses in the crystal to enable oscillation. Firstly, it is briefly explained how to model the crystal resonator in Section 4.1. Secondly, a linear analysis on how the most simple Pierce circuit works is addressed in Section 4.2. The operation of a Pierce oscillator in a more general form, is presented in Section 4.3. The simplified case of the amplifier being lossless is studied in Section 4.3.1. In the ultra low voltage context, the losses in the amplifier are not negligible. The quantification of these losses and how to deal with them, is subject of Section 4.3.2. The design of two crystal oscillators is presented in Section 4.4, based on our work in [40]. A Schmitt trigger circuit is used as the amplifier of each of the crystal oscillators. The design of the Schmitt trigger circuits is the one explained in Section 2.6.

# 4.1 Equivalent impedance of the quartz crystal

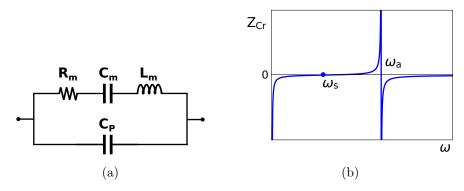

A quartz crystal can be modeled by means of a motional impedance in parallel with a capacitance [3]. This motional impedance depends on the resonance mode of the crystal resonator. Fig. 4.1a shows the equivalent impedance model, used in the fundamental mode, where  $R_m$ ,  $C_m$  and  $L_m$  are the motional resistance, capacitance and inductance, respectively, and  $C_P$  is the parallel capacitance.

Thus, the motional impedance of the crystal is given by

$$Z_m = R_m + j\omega L_m + \frac{1}{j\omega C_m}. (4.1)$$

Neglecting  $R_m$ , the equivalent impedance in Fig. 4.1a is such that

$$Z_{Cr} \approx \frac{1}{s} \frac{1 + L_m C_m s^2}{L_m C_m C_P s^2 + C_m + C_P}.$$

(4.2)

$Z_{Cr}$  in (4.2) has one pole at zero frequency, a double zero at  $\omega_s$ , with

$$\omega_s = \frac{1}{\sqrt{L_m C_m}},\tag{4.3}$$

#### Chapter 4. Design of crystal oscillators

Figure 4.1: Crystal resonator: (a) circuit schematic of the equivalent impedance model and (b) value of the module of the impedance of the crystal as a function of the frequency  $\omega$ .

and a double pole at  $\omega_a$ , with

$$\omega_a = \omega_s \sqrt{1 + \frac{C_m}{C_P}} \approx \omega_s \left( 1 + \frac{C_m}{2C_P} \right),$$

(4.4)

provided that  $C_m/C_P \ll 1$ .

Thus, the crystal impedance can be rewritten as follows

$$Z_{Cr} \approx \frac{1}{j\omega C_P} \frac{1 - \frac{\omega^2}{\omega_s^2}}{1 - \frac{\omega^2}{\omega^2}}.$$

(4.5)

Figure 4.1b shows the dependence of the module of the crystal impedance on frequency.

# 4.2 Linear analysis of the basic Pierce oscillator

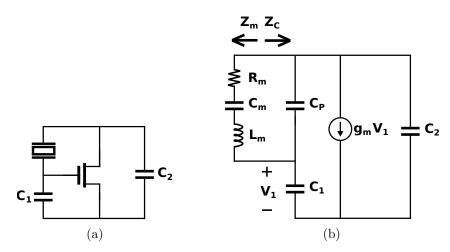

The most basic form of the Pierce oscillator is depicted in Fig. 4.2a, where a single nMOS transistor is used. The biasing circuit is omitted, without losing generality. On the right hand, Fig. 4.2b shows the impedance equivalent model of the circuit in Fig. 4.2a, where  $Z_m$  in parallel to  $C_P$  represents the crystal equivalent model seen in Section 4.1.

The oscillation condition is given by

$$Z_C + Z_m = 0, (4.6)$$

where the impedance  $Z_C$  represents the rest of the circuit, besides motional impedance, as marked in Fig. 4.2b.

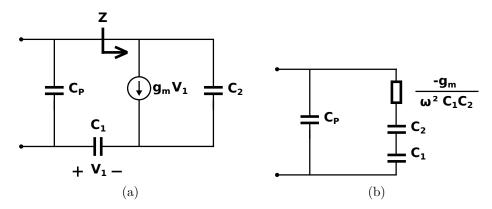

To obtain an expression for  $Z_C$  it is useful to compute the impedance Z marked in Fig. 4.3a, this is, the transconductance in parallel with  $C_2$ . Thus,

$$Z = \frac{g_m + j\omega C_1}{j\omega C_2 j\omega C_1} = \frac{1}{j\omega C_2} + \frac{g_m}{(j\omega)^2 C_1 C_2}.$$

(4.7)

Figure 4.2: Single nMOS Pierce crystal oscillator (a) circuit schematic and (b) impedance equivalent model.

Figure 4.3: Two equivalent circuit schematics representing the same impedance  $Z_C$ .

In this way, the circuit schematic in Fig. 4.3a can be redrawn as that depicted in Fig. 4.3b. Thus, the impedance  $Z_C$  is given by

$$Z_C = -\frac{g_m + j\omega(C_1 + C_2)}{(C_1C_2 + C_1C_P + C_2C_P)\omega^2 - j\omega q_m C_P}.$$

(4.8)

Rearranging (4.8) it is obtained

$$Z_C = -\frac{g_m C_1 C_2 + j[\omega(C_1 + C_2)(C_1 C_2 + C_1 C_P + C_2 C_P) + g_m^2 C_P/\omega]}{\omega^2 (C_1 C_2 + C_1 C_P + C_2 C_P)^2 + (g_m C_P)^2}.$$

(4.9)

From (4.1) and (4.3), and neglecting  $R_m$ , it can be seen that  $Z_m$  at the oscillation frequency  $\omega_P$  is such that

$$Z_m(\omega_P) = \frac{\omega_s^2 - \omega_P^2}{j\omega_s^2\omega_P C_m} \approx \frac{2(\omega_s - \omega_P)}{j\omega_s\omega_P C_m},\tag{4.10}$$

#### Chapter 4. Design of crystal oscillators

since  $(\omega_s + \omega_P) \approx 2\omega_s$ . Then the oscillation condition in (4.6), aided by (4.9) and (4.10), for  $g_m \to 0$ , reduces to

$$\frac{2(\omega_P - \omega_s)}{C_m \omega_s^2} = \frac{C_1 + C_2}{\omega_s (C_1 C_2 + C_1 C_P + C_2 C_P)}.$$

(4.11)

Defining

$$C_L = \frac{C_1 C_2}{C_1 + C_2},\tag{4.12}$$

the oscillation frequency is obtained from (4.11) and (4.12) as

$$\omega_P = \omega_s \left[ 1 + \frac{C_m}{2(C_P + C_L)} \right]. \tag{4.13}$$

Note that (4.13) is the same result that was obtained in (4.4), by calculating the pole of the impedance of the crystal.

Comparing (4.13) and (4.4), we observe that  $\omega_s < \omega_P < \omega_a$ . Thus, at the oscillation frequency the impedance of the crystal is inductive, as expected. The impedance of the crystal  $Z_{Cr}$  in (4.5) can be obtained at the oscillation frequency, using the expressions for  $\omega_s$  and  $\omega_a$  in (4.3) and (4.4), respectively, giving

$$Z_{Cr}(\omega_P) = \frac{1}{j\omega_P C_P} \frac{1 - \left[1 + \frac{C_m}{2(C_P + C_L)}\right]^2}{1 - \frac{\left[1 + \frac{C_m}{2(C_P + C_L)}\right]^2}{\left[1 + \frac{C_m}{2C_P}\right]^2}} \approx \frac{j}{\omega_s C_L}.$$

(4.14)

The critical value of the transconductance to enable oscillation, called  $g_{mcrit}$ , is obtained by means of balancing the real parts of  $Z_C$  and  $Z_m$  when  $g_m \to 0$ , this is

$$-\operatorname{Re}(Z_C)\big|_{g_m\to 0} = R_m,\tag{4.15}$$

thus, giving

$$g_{mcrit} = \omega_s^2 R_m C_1 C_2 \left( 1 + \frac{C_P}{C_L} \right). \tag{4.16}$$

If  $C_1 = C_2 = 2 \times C_L$ , (4.16) reduces to

$$g_{mcrit} = 4\omega_s^2 R_m (C_L + C_P)^2.$$

(4.17)

# 4.3 Pierce crystal oscillator operation

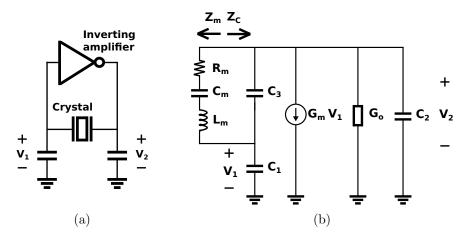

The schematic of a Pierce oscillator is depicted in Fig. 4.4a, consisting of a quartz crystal connected to an amplifier and two functional capacitors [3]. The amplifier provides the negative resistance required to compensate for the crystal losses, in order for the oscillation to take place.

Figure 4.4b shows the equivalent impedance model of the circuit in Fig. 4.4a. On the left hand side, the motional impedance  $Z_m$ , accounts for the motional part of the crystal by means of the series of  $R_m$ ,  $C_m$  and  $L_m$ , the crystal motional

Figure 4.4: Pierce crystal oscillator (a) circuit schematic and (b) impedance equivalent model.

resistance, capacitor and inductor, respectively. On the right hand side,  $Z_C$  represents the rest of the circuit impedance for the fundamental frequency, this is, the compact small-signal model of the rest of the circuit connected in parallel to the crystal and also the crystal parallel capacitance  $C_3$ .  $G_m$  and  $G_o$  are the transconductance and the output conductance of the inverting amplifier, respectively. All of the parasitic capacitances within the inverting amplifier as well as the functional capacitors, are grouped in the capacitances  $C_1$  and  $C_2$ .

#### 4.3.1 Lossless amplifier

Having a lossless amplifier implies that the conductance  $G_o$  in Fig. 4.4b is neglected. According to [3], and by inspection of the schematic in Fig. 4.4b,  $Z_C$  can be expressed as

$$Z_C = \frac{Z_1 Z_3 + Z_2 Z_3 + G_m Z_1 Z_2 Z_3}{Z_1 + Z_2 + Z_3 + G_m Z_1 Z_2},$$

(4.18)

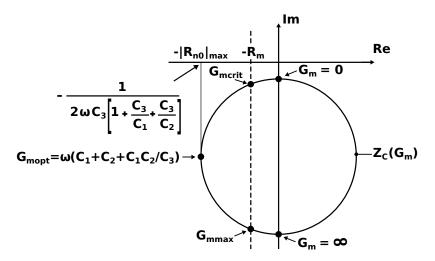

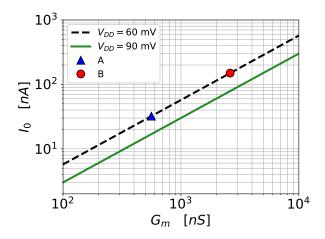

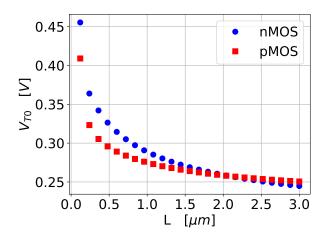

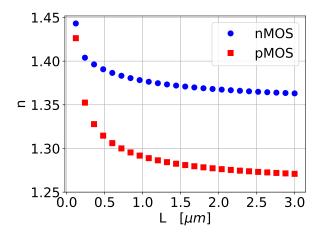

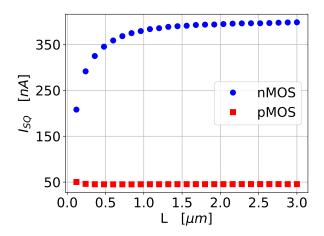

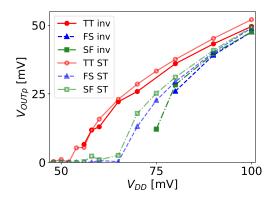

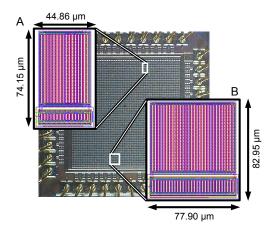

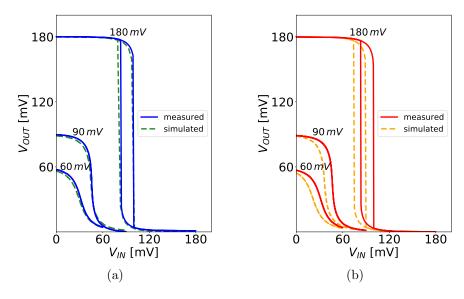

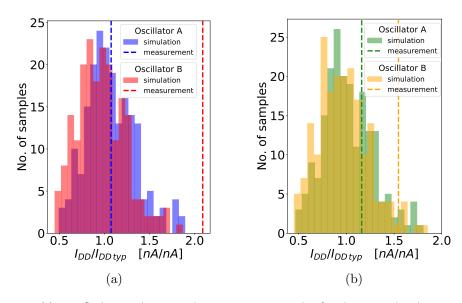

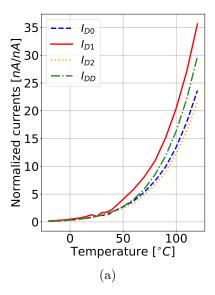

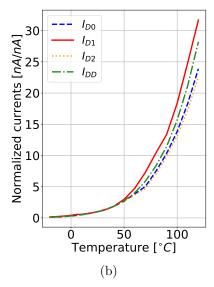

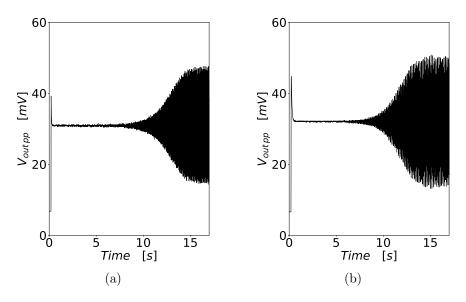

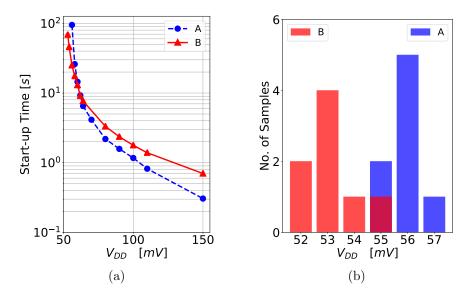

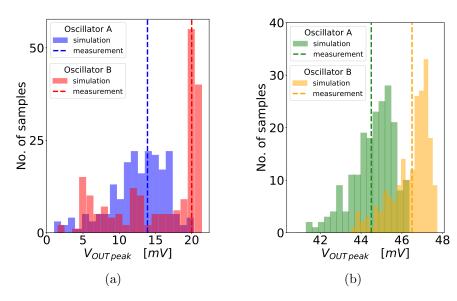

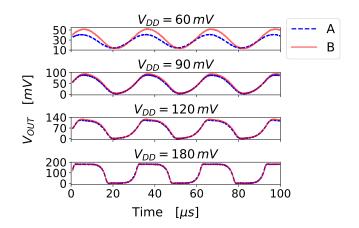

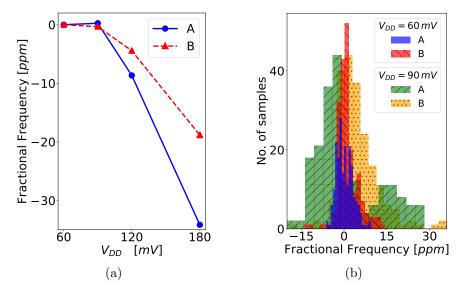

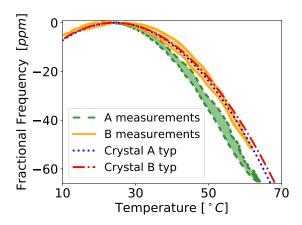

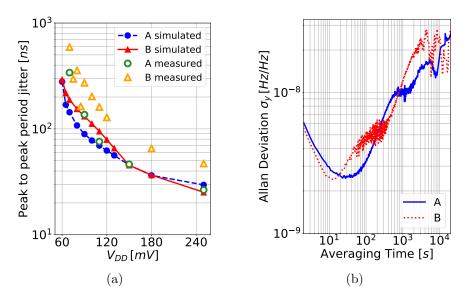

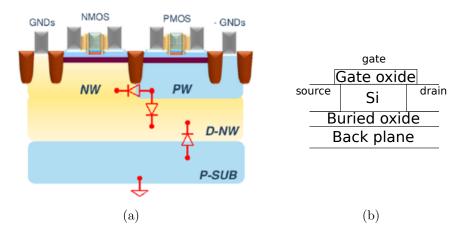

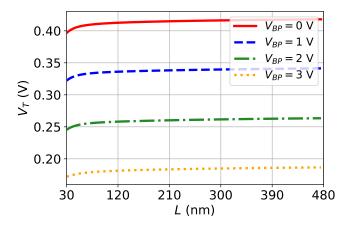

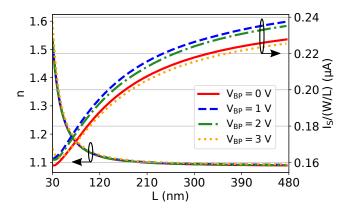

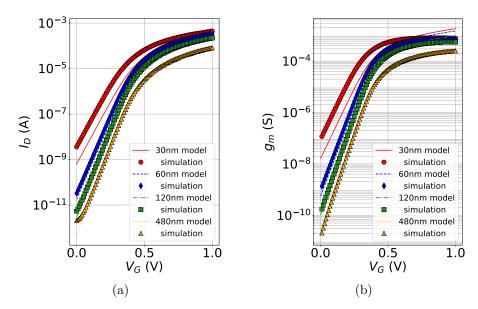

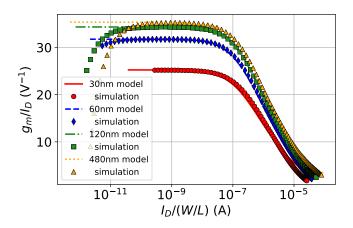

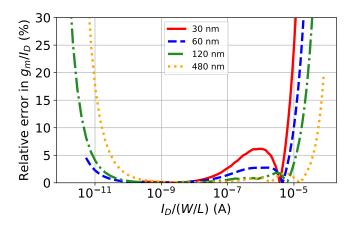

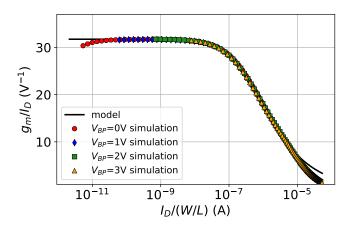

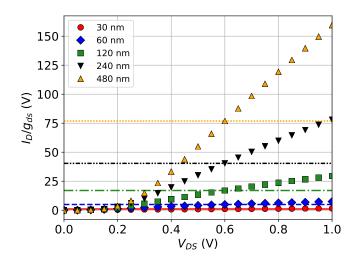

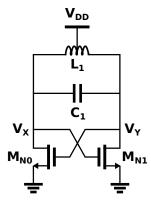

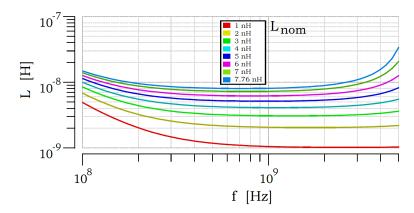

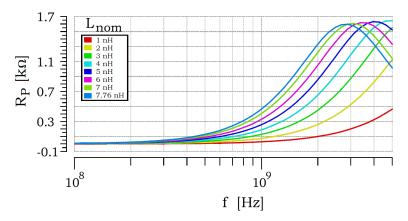

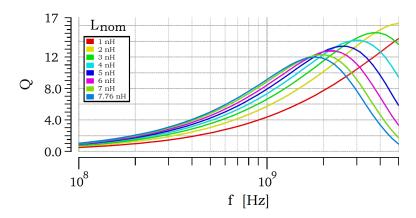

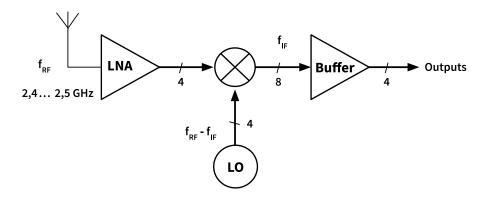

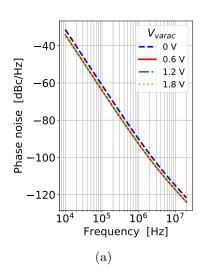

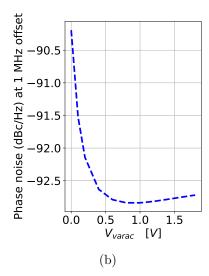

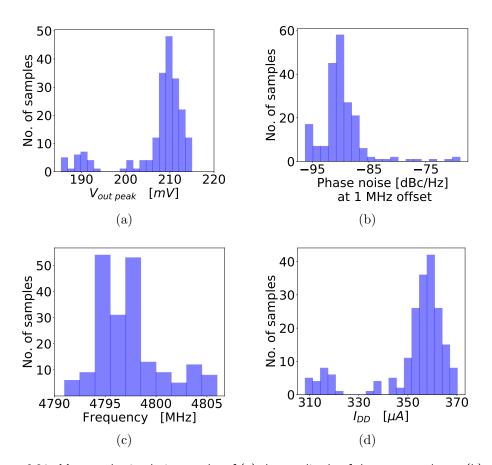

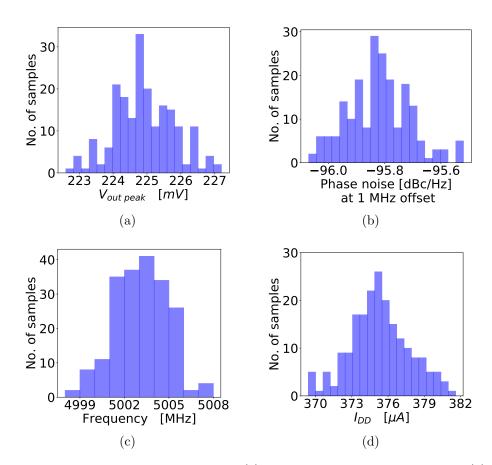

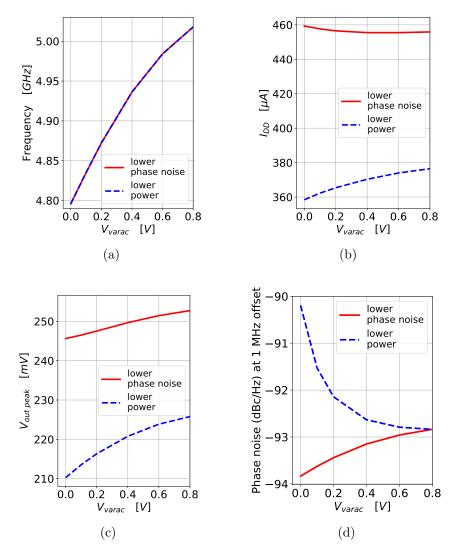

being  $Z_1 = 1/j\omega C_1$ ,  $Z_2 = 1/(G_o + j\omega C_2)$  and  $Z_3 = 1/j\omega C_3$ .