### Universidad de la República Facultad de Ingeniería

### Reciclado de carga y circuitos para mejora de la eficiencia en conversores DC/DC integrados de ultra baja potencia

Tesis presentada a la Facultad de Ingeniería de la Universidad de la República por

### Pablo Castro Lisboa

EN CUMPLIMIENTO PARCIAL DE LOS REQUERIMIENTOS

PARA LA OBTENCIÓN DEL TÍTULO DE

DOCTOR EN INGENIERÍA ELÉCTRICA.

| Directores de Tesis                                                   |

|-----------------------------------------------------------------------|

| Dr. Fernando Silveira (Director) Universidad de la República          |

| Dr.Gabriel Eirea (co-Director) Universidad de la República            |

| ·                                                                     |

| Tribunal                                                              |

| Dr. Eduard Alarcon, Profesor Titular (Revisor Externo), Universidad   |

| Politécnica de Cataluña, España                                       |

| Dr. Marcio Cherem Schneider, Profesor Titular (Revisor Externo),      |

| Universidad Federal de Santa Catarina, Florianópolis, Brasil          |

| Dr. Alejandro Oliva, Profesor Adjunto, Universidad Nacional del Sur,  |

| Argentina                                                             |

| Dr. Gabriel Eirea, Profesor Agregado, Universidad de la República,    |

| Uruguay                                                               |

| Dr. Fernando Silveira, Profesor Titular, Universidad de la República, |

| · · · · · · · · · · · · · · · · · · ·                                 |

| Uruguay                                                               |

|                                                                       |

| Director Académico                                                    |

| Dr.Fernando Silveira                                                  |

Montevideo viernes 3 febrero, 2017

Reciclado de carga y circuitos para mejora de la eficiencia en conversores DC/DC integrados de ultra baja potencia, Pablo Castro Lisboa.

### ISSN 1688-2784

Esta tesis fue preparada en LATEX usando la clase iietesis (v1.1). Contiene un total de 127 páginas.

Compilada el viernes 3 febrero, 2017.

http://iie.fing.edu.uy/

### Agradecimientos

A mis tutores Fernando Silveira y Gabriel Eirea para la confianza depositada, y por su apoyo en todos estos años.

A la Comisión Académica de Posgrados de la UDELAR por la beca de finalización de doctorado.

Pablo Pérez-Nicoli, Francisco Veirano y Sebastián Besio, por haber dedicado su tesis de grado al apoyo de este trabajo. Particularmente en los circuitos presentados en el capítulo 4 así como parte de la sección 5.1. Francisco Veirano, mediante una beca de iniciación a la investigación trabajó en el desarrollo de la técnica presentada en la sección 2.2.

### Resumen

El presente trabajo profundiza en el estudio de conversores DC/DC de capacitores conmutados totalmente integrados para aplicaciones de ultra bajo consumo como ser: dispositivos implantables, redes de sensores inalámbricos, dispositivos portátiles, etc. El objetivo de este tipo de sistemas es el de suministrar energía al circuito correspondiente pero con una tensión diferente a la de la batería utilizada. Básicamente hay dos razones para suministrar una tensión diferente a la de la fuente principal. Por un lado, en los circuitos digitales existe un compromiso entre performance (velocidad de procesamiento) y consumo, que en general se puede manejar mediante la técnica de escalado dinámico de voltaje y frecuencia ("Dynamic Voltage and Frequency Scaling"); esta técnica básicamente disminuye la tensión de alimentación y la frecuencia del sistema cuando la exigencia de procesamiento es baja y los sube cuando es alta. De esta forma, en muchas aplicaciones se puede ahorrar una cantidad significativa de energía. Por otro lado, el escalado de las nuevas tecnologías ha alcanzado un punto donde los transistores básicos no soportan la tensión de las baterías que se consiguen en el mercado. Para ambos casos, tener un conversor DC/DC que sea capaz de manejar todo el rango (o al menos una buena parte) entre tierra y la tensión de alimentación es esencial.

En esta tesis, se contribuye a la mejora de la eficiencia de este tipo de conversores con varias técnicas que permiten reciclar parte de la carga asociada a capacidades parásitas, y por técnicas de diseño de circuitos de bloques auxiliares.

La idea de reciclar la carga de las capacidades parásitas ha sido explorada en la literatura, sin embargo todos los antecedentes están limitados a arquitecturas particulares del conversor DC/DC. En este trabajo se proponen técnicas generales para reciclar la carga de capacidades parásitas asociadas a las placas de los capacitores principales (capacidades parásitas de "top/bottom plate") y capacidad de gate independientemente de la arquitectura del conversor. Dichas técnicas son independientes de la arquitectura del conversor.

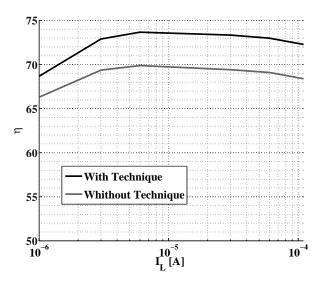

La técnica general del reciclado de carga de las capacidades de top/bottom plate es comprobada mediante simulaciones eléctricas de un conversor particular con relación de conversion de 1/3. Estas simulaciones se realizaron con una tecnología CMOS de 130nm y una alimentación de 1,2V. Los resultados muestran una eficiencia máxima de 74,5% basada en una mejora de hasta 7% en la eficiencia

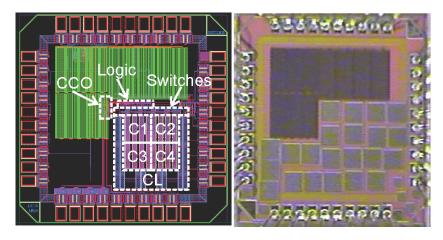

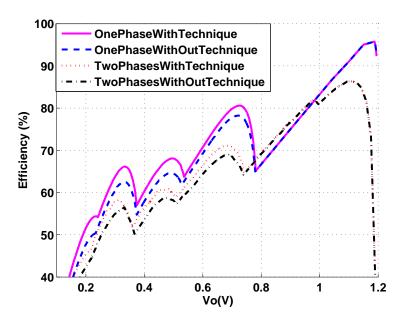

de dicho conversor. Esta mejora se logra a partir del uso de la técnica general presentada, que recicla la carga de las capacidades parásitas de top/bottom plate, y que permite una disminución en este tipo de pérdidas de  $52\,\%$ . Adicionalmente, se presentan resultados de medidas de un conversor modular. Dicha arquitectura permite una implementación de la técnica de reciclado de carga de las capacidades parásitas de top/bottom plate muy simple que mejora la eficiencia de forma significativa. Además, se probaron dos mecanismos para manejar las fases del conversor. Un ejemplo de este conversor modular fue fabricado en una tecnología CMOS de 130nm y con un número de 6 relaciones de conversión para el cual se presentan resultados de medidas. En este caso, se logró un pico de eficiencia de  $80,6\,\%$ , y un pico en la mejora de la eficiencia de  $4\,\%$  basado en una reducción en las pérdidas de de top/bottom plate de  $70\,\%$ .

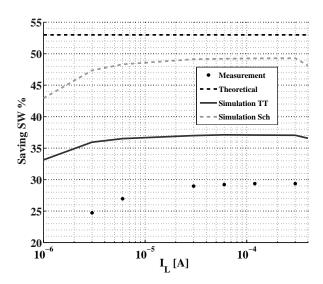

Por otro lado, se utilizó la técnica de "stepwise charging" en el gate de las llaves de otro conversor DC/DC de capacitores conmutados de relación de conversión 1/3, con el objetivo de ahorrar energía en los drivers. Si bien esta técnica es conocida y su aplicación se presenta en otros trabajos, no se han reportado resultados aplicando la técnica en conversores DC/DC de ultra bajo consumo. Adicionalmente, se hace un estudio analítico que determina bajo que circunstancias la aplicación de la técnica tiene sentido. Las mejoras en la eficiencia del conversor gracias a la aplicación de la técnica fueron confirmadas con medidas, y los resultados arrojan una eficiencia de 72.8% a partir de una mejora de 4% gracias a la aplicación de la técnica para una corriente entregada a la carga  $I_L = 60\mu A$  y una tensión de salida  $V_O = 0.37V$ . La tecnología en la que fue fabricado el conversor es 130nm y la alimentacion fue  $V_{DD} = 1.2V$

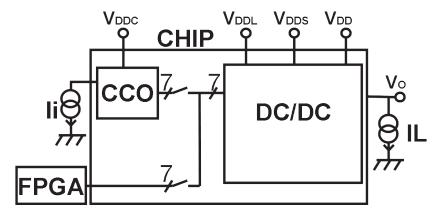

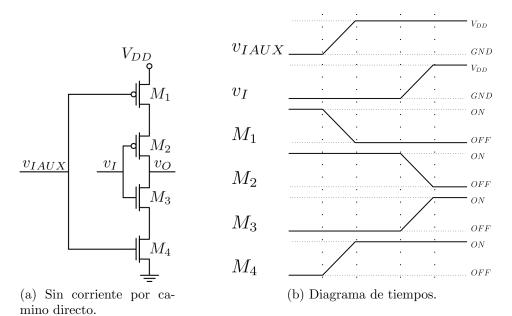

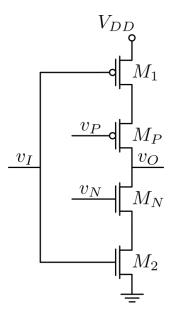

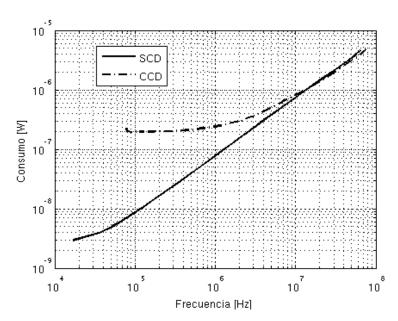

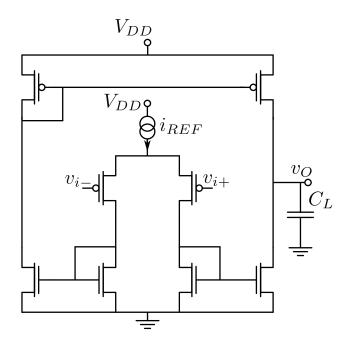

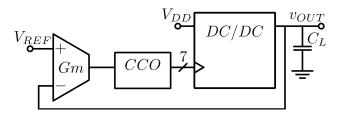

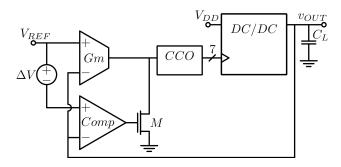

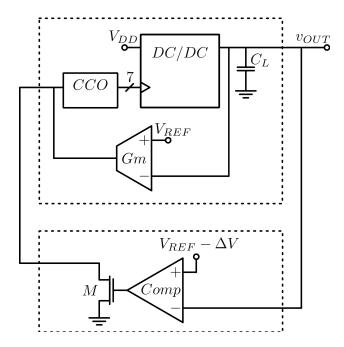

Dado que los conversores analizados son para aplicaciones de ultra bajo consumo, el conversor mismo debe tener esta característica. Por lo tanto, los circuitos que implementan el lazo de realimentación que regula la tensión de salida deben estar pensados con este objetivo. Para ello, se presenta un oscilador de anillo controlado por corriente (CCO), que tiene como novedad principal la eliminación de la corriente de camino directo. Esto logra un consumo de potencia proporcional a la frecuencia de oscilación lo cual es apropiado para no degradar la eficiencia del conversor. Resultados de simulación muestran un consumo que tienen una dependencia lineal con la frecuencia de conmutación. A nivel de simulaciones eléctricas post layout se pudo constatar que dicho CCO tiene un consumo de 3nW a una frecuencia de 10kHz y  $5\mu W$  a una frecuencia de 40MHz. Por otro lado, a nivel de medidas también se constató una dependencia lineal entre la frecuencia y el consumo. En este caso, la frecuencia mínima lograda dentro del comportamiento lineal es de 80kHz alcanzando un consumo de 50nW. En el otro extremo la frecuencia máxima alcanzada es de 100MHz con un consumo de  $10\mu W$ .

Por otro lado, se implementó un comparador que utiliza resistencias variables (implementadas con transistores en zona lineal) que permiten cambiar drásticamente el factor de copia de los espejos de corriente. De esta forma se logra un

circuito analógico que responde de forma muy rápida, siendo capaz de entregar un rango de corriente de varios órdenes de magnitud que van desde algunos nA hasta algunos  $\mu A$ , a partir de una corriente de polarización de 2,5nA. Estos resultados también fueron alcanzados mediante simulaciones utilizando una tecnología de 130nm.

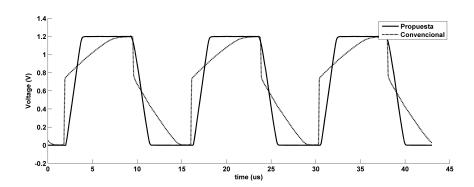

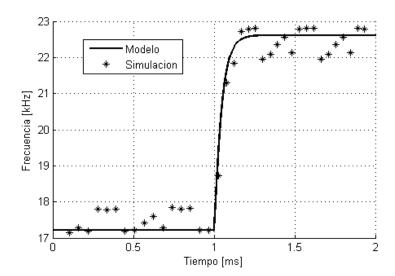

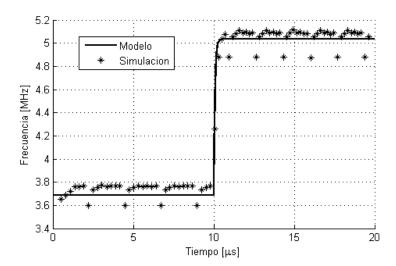

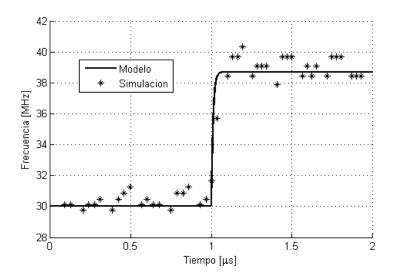

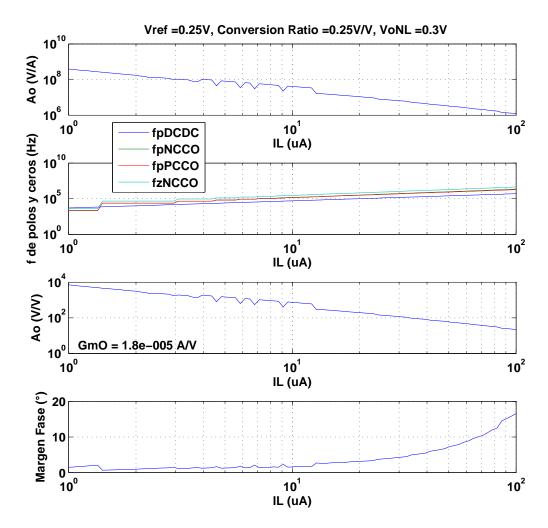

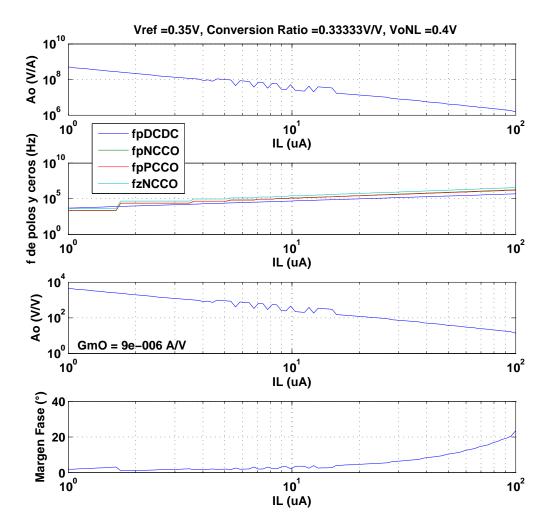

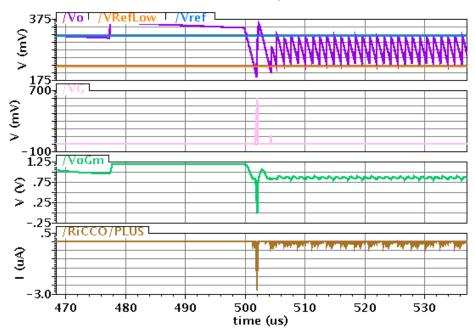

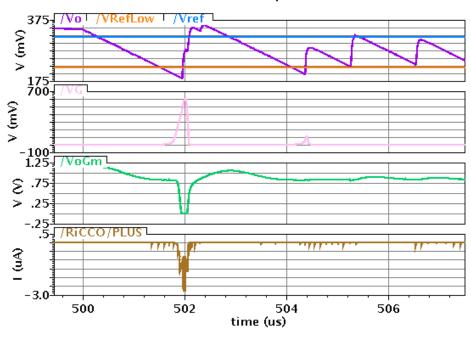

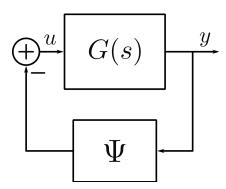

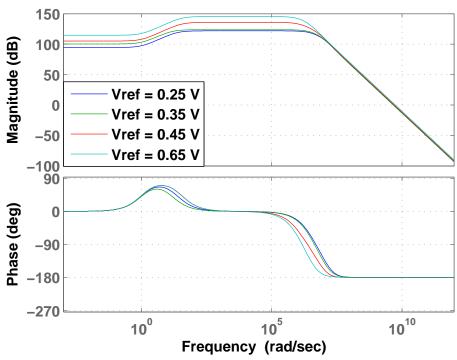

Otro tema que se abordó en este trabajo fue el de la regulación de esta clase de conversores de tensión. Para ello de desarrolló un modelo promediado lineal tanto para el conversor DC/DC modular fabricado como para el CCO. A partir de estos modelos se diseñó un controlador lineal que permite regular la tensión de salida. Dado que este sistema realimentado no es capaz de reaccionar suficientemente rápido frente a grandes picos crecientes en la corriente de carga, se diseñó un lazo no lineal adicional con una velocidad de respuesta muy alta que solo actúa cuando la tensión de salida cae por debajo de un cierto umbral. Esto permite que la tensión de salida no caiga por debajo de niveles no aceptables para la carga que esta siendo alimentada, incluso cuando existe un escalón creciente de varios órdenes de magnitud en la corriente de carga. Este sistema de realimentación fue comprobado mediante simulaciones eléctricas.

# Tabla de contenidos

| Αş | Agradecimientos |                                                                                                                                                |            |  |  |

|----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|

| Re | esum            | en                                                                                                                                             | v          |  |  |

| 1. | Intr            | roducción                                                                                                                                      | 1          |  |  |

|    | 1.1.            | Motivación                                                                                                                                     | 1          |  |  |

|    | 1.2.            | Consideraciones generales sobre conversores DC/DC de capacitores                                                                               |            |  |  |

|    |                 | conmutados                                                                                                                                     | 4          |  |  |

|    |                 | 1.2.1. Pérdidas y eficiencia en un conversor DC/DC de capacitores conmutados                                                                   | S          |  |  |

|    |                 | 1.2.2. Regulación de la tensión de salida y sus implicancias en la eficiencia                                                                  | 13         |  |  |

|    |                 | 1.2.3. Reciclado de carga                                                                                                                      | 16         |  |  |

| 2. | Téc             | nicas de reciclado de carga                                                                                                                    | 19         |  |  |

|    | 2.1.            | Técnica general de reciclado de carga para capacidades parásitas de                                                                            |            |  |  |

|    |                 | top/bottom-plate                                                                                                                               | 19         |  |  |

|    | 2.2.            | Reciclado de carga del gate de las llaves                                                                                                      | 24         |  |  |

|    |                 | 2.2.1. Análisis teórico de la técnica "stepwise charging"                                                                                      | 28         |  |  |

|    |                 | <ul><li>2.2.2. Límites de la técnica de stepwise charging</li><li>2.2.3. Aplicación de la técnica "stepwise charging" a un conversor</li></ul> | 33         |  |  |

|    |                 | $\mathrm{DC}/\mathrm{DC}$ de capacitores conmutados                                                                                            | 37         |  |  |

| 3. | Con             | nversor de arquitectura modular                                                                                                                | 41         |  |  |

|    | 3.1.            | Manejo del conversor modular con una fase                                                                                                      | 42         |  |  |

|    | 3.2.            | Manejo del conversor modular con dos fases                                                                                                     | 43         |  |  |

|    | 3.3.            | Técnica de reciclado de carga aplicada al conversor modular                                                                                    | 44         |  |  |

|    | 3.4.            | Resultados de simulación del conversor modular                                                                                                 | 48         |  |  |

|    | 3.5.            | Resultados de medidas del conversor modular                                                                                                    | 49         |  |  |

|    | 3.6.            | Comparación con el estado del arte                                                                                                             | 51         |  |  |

| 4. | Circ            | cuitos para la implementación de conversores DC/DC de ultra                                                                                    |            |  |  |

|    | •               | o consumo                                                                                                                                      | <b>5</b> 5 |  |  |

|    | 4.1.            | Oscilador de anillo y generador de pulsos de ultra bajo consumo   .                                                                            | 55         |  |  |

|    |                 | 4.1.1. Arquitectura propuesta para el CCO                                                                                                      | 58         |  |  |

|    |                 | 4.1.2. Generador de pulsos de ancho variable                                                                                                   | 62         |  |  |

### Tabla de contenidos

|        | 4.1.3. Resultados de simulación                              | 64         |

|--------|--------------------------------------------------------------|------------|

| 4.2.   | Transconductor de ultra bajo consumo                         | 65         |

|        | 4.2.1. Resultados de simulación sobre el comparador          | 69         |

| 5. Reg | gulación de la tensión de salida                             | 71         |

| 5.1.   | Modelo lineal promediado en lazo abierto                     | 72         |

|        | 5.1.1. Modelo lineal promediado del conversor                | 73         |

|        | 5.1.2. Modelo lineal promediado del CCO                      | <b>7</b> 4 |

|        | 5.1.3. Validación del modelo                                 | 80         |

| 5.2.   | Lazos de control                                             | 81         |

|        | 5.2.1. Lazo lineal                                           | 82         |

|        | 5.2.2. Lazo no lineal                                        | 86         |

| 6. Con | nclusiones y trabajo a futuro                                | 95         |

| 6.1.   | Trabajos a futuro                                            | 97         |

| 6.2.   | Lista de publicaciones asociadas a la tesis                  | 98         |

|        | 6.2.1. Artículos en revistas                                 | 98         |

|        | 6.2.2. Artículos en conferencias                             | 98         |

| 6.3.   | Lista de publicaciones no directamente asociadas a la tesis  | 99         |

|        | 6.3.1. Artículos en revistas                                 | 96         |

|        | 6.3.2. Artículos en conferencias                             | 99         |

| A. Aná | álisis de las pérdidas debido a las CPTBP                    | 101        |

| A.1.   | Análisis para el conversor 1/3                               | 102        |

| A.2.   | Análisis para el conversor modular                           | 103        |

|        | A.2.1. Análisis sin aplicar la técnica de reciclado de carga | 103        |

|        | A.2.2. Análisis aplicando la técnica de reciclado de carga   | 104        |

| Refere | ncias                                                        | 105        |

| Índice | de tablas                                                    | 109        |

| Índice | de figuras                                                   | 110        |

### Capítulo 1

### Introducción

### 1.1. Motivación

Desde hace varios años se ha incrementado notoriamente la existencia de dispositivos alimentados por batería (teléfonos móviles, tablets, redes de sensores inalámbricos, dispositivos implantables, etc). Esto ha implicado un aumento en los esfuerzos para alcanzar una mayor duración de las baterías y así una mayor autonomía. Los dispositivos implantables son los más críticos debido a que el agotamiento de la batería implica una cirugía para el paciente. Por otro lado, también se tienen las redes de sensores inalámbricos, en cuyo caso el agotamiento frecuente de las baterías incrementaría los costos asociados a logística si el número de nodos es grande y/o la distribución geográfica muy amplia.

Prácticamente en cualquier sistema electrónico los circuitos digitales juegan un rol muy importante y requieren de una fracción significativa del consumo total del circuito. De esta forma, minimizando el consumo de energía de los circuitos digitales se hace una gran contribución para aumentar la duración de la batería. Existen varias técnicas que permiten reducir el consumo de los circuitos digitales, una muy conocida denominada "escalado dinámico de voltaje" (DVS) consiste en reducir la tensión de alimentación [1] [2] [3], y en algunos casos se utiliza la lógica sub-umbral [2], [4], [5]. En este sentido, el desarrollo de sistemas con múltiples dominios de alimentación, permiten hacer un mejor aprovechamiento de la energía ya que se puede alimentar diferentes bloques de forma independiente con la tensión mínima necesaria en cada uno de ellos en todo instante de tiempo. De lo anterior, surge la necesidad de tener conversores totalmente integrados para que el número de componentes externos no se incremente por tener múltiples dominios.

Por otro lado, el escalado de la tecnología ha decrementado la máxima tensión permitida por los transistores, incluso por debajo de las tensiones suministradas por las baterías. Por lo tanto, tener la capacidad de entregar al circuito una tensión menor a la suministrada por la batería es esencial. Esto se debe lograr con eficiencia para que la energía ahorrada por tener una menor alimentación no sea

desperdiciada por el conversor DC/DC.

Una aplicación típica de mucha importancia es cuando se utilizan microcontroladores que tienen un comportamiento sistemático repetitivo entre un modo de bajo consumo (modo sleep) y un modo activo [6]. En general trabajan por períodos prolongados de tiempo en modo sleep consumiendo muy poca potencia, y se "despiertan" periódicamente para realizar una tarea específica para luego volver al modo sleep. En modo sleep el consumo que pueden alcanzar es menor al de algunos  $\mu A$  hasta los nA. A modo de ejemplo, PIC12(L)F1571/2 es una familia de microcontroladores de ultra bajo consumo (ULP) de la empresa Microchip que tiene un consumo en modo activo de  $30\mu A/MHZ_{@V_{DD}=1,8V}$ . En modo sleep tienen un consumo de  $20nA_{@V_{DD}=1,8V}$  aunque en este caso se necesita un evento externo para salir de dicho modo. Otra opción es la de modo sleep con un timer activo para salir de dicho modo en cuyo caso se tiene un consumo de  $260nA_{@V_{DD}=1,8V}$ . Otro ejemplo es la familia MSP430FR203X de la empresa Texas Instruments tiene un consumo en modo activo de  $126\mu A/MHZ_{@V_{DD}=3V}$ , un modo sleep que consume  $15nA_{@V_{DD}=3V}$ , y un modo sleep con timer activo que consume  $770nA_{@V_{DD}=3V}$ . Por lo tanto, contar con conversores que sean eficientes para estos ordenes de magnitud de corriente es importante. Si bien en las familias de microcontroladores presentados no se aplican técnicas que impliquen usar una tensión de alimentación diferente a la de la batería, dan una pauta de los órdenes de magnitud de consumo que las tecnologías disponibles permiten alcanzar.

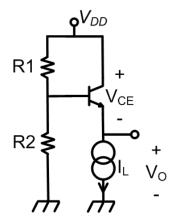

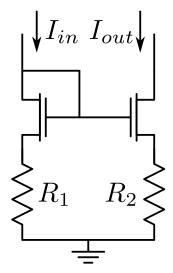

La opción más básica para implementar un conversor DC/DC step-down son los denominados conversores lineales. En la figura 1.1 se muestra una configuración básica para este tipo de arquitecturas (seguidor de emisor en este caso) donde la tensión de salida esta determinada por el divisor resistivo de R1 y R2 y la caída en la juntura base-emisor  $V_{BE}$  del transistor como lo muestra la ecuación 1.1.

$$V_O = V_{DD} \cdot \frac{R2}{R1 + R2} - V_{BE} \tag{1.1}$$

Este tipo de reguladores tienen la característica (a diferencia de los conversores inductivos y de los capacitivos) de que la corriente que se entrega a la carga es la misma que se toma de la fuente. De esta forma, la potencia entregada a la carga será menor que la entregada por la fuente y la eficiencia será peor cuanto menor la tensión de salida. Haciendo un balance de energía es evidente que la diferencia se tiene que estar disipando en algún componente del circuito. En el caso del conversor de la figura 1.1 esa potencia de disipa en el transistor que entrega la corriente a la carga (se asume que la potencia disipada en R1 y R2 es despreciable). Por lo tanto, son conversores muy ineficientes no convenientes para nuestras aplicaciones por lo que quedan descartados. De esta forma, solo quedan los conversores inductivos y los conversores de capacitores conmutados.

La familia de conversores inductivos se basan en entregar energía por parte de la fuente de alimentación a un inductor, para que luego éste entregue energía a la carga y a un condensador que mantiene la tensión de salida. Si bien son conversores

Figura 1.1: Conversor DC/DC lineal.

muy eficientes presentan algunas características que no los hace adecuados para las aplicaciones que se abordan en este trabajo. Primero que nada son conversores que son usados para entregar potencias significativamente mayores a las mencionadas en los párrafos anteriores. En particular mucho mayores a los consumos de modo sleep de los microcontroladores mencionados. A modo de ejemplo, en [7] se usa un conversor híbrido inductivo-capacitivo que usa el conversor capacitivo cuando la carga requiere baja potencia y el inductivo cuando se requiere mayor potencia. En [8] se presenta un análisis que compara los conversores inductivos con los capacitivos y llega a la conclusión que los inductivos no son apropiados para aplicaciones de ULP. Por otro lado, la integración de inductores obtiene bajos factores de calidad (Q), o se implementan usando tecnologías especiales. De esta forma, podemos concluir que los conversores inductivos no son apropiados para conversores totalmente integrados de ULP en tecnologías estándar.

A nivel comercial, existen opciones que logran buenas eficiencias para corrientes de algunos  $\mu A$ . A modo de ejemplo, el chip TS3310 de la empresa "Silicon Labs" es un conversor step-up inductivo que reporta una eficiencia por encima del 70% para corrientes de carga menores al  $\mu A$ . El chip LTC3250-1,2 de la empresa Linear Technology es un conversor step down de capacitores conmutados que si bien reporta una eficiencia mayor al 80% para corrientes de carga mayores a 1mA, para una corriente de carga de  $100\mu A$  la eficiencia ya cae al 53% y no se reportan resultados de eficiencia para corrientes menores. El chip TPS62730 de la empresa Texas Instruments es un conversor step down inductivo que logra eficiencias por encima del 90% pero para corrientes cercanas a los  $100\mu A$  se cae al entorno del 60% y sigue bajando para corrientes menores. Todos estos ejemplos tienen en común que necesitan componentes externos (inductores y/o capacitores) cuyos valores los hacen imposibles para ser integrados. Por lo tanto, todas estas opciones no son útiles para conversores DC/DC totalmente integrados . De lo previo, se puede concluir que para aplicaciones totalmente integradas de ULP,

los conversores DC/DC de capacitores conmutados son una buena opción.

A la fecha, existen varios trabajos respecto a conversores DC/DC totalmente integrados. [9] es una importante referencia que presenta un conversor totalmente integrado con múltiples relaciones de conversión. Logra buenos niveles de eficiencia reportando resultados por encima del 75 %, ayudado de una técnica que permite reducir la pérdidas debido a las capacidades parásitas de top/bottom plate (CPTBP). Utiliza una fuente de alimentación de 1,2V para el conversor, la lógica y las llaves de fase, y una alimentación extra de 1,8V para las llaves que definen la topología. Esta fuente de alimentación extra hace más difícil la comparación ya que implica un grado de libertad extra, además de implicar una complejidad mayor a nivel del sistema y la necesidad de manejar esta tensión más elevada.

- [10] presenta un conversor interleaved de dos fases con tres relaciones de conversion y una llave que conecta directamente la salida con la entrada para responder en caso de necesitar transiciones rápidas. Si bien esta técnica de la llave directa funciona correctamente, no parece apropiada para sistemas de ULP ya que en caso de ser usada frecuentemente podría causar una disipación de potencia importante. Se reporta una máxima eficiencia de 55 %.

- [11] presenta una estructura interleaved con 32 fases que manifiesta la utilidad de esta técnica para disminuir el ripple y así mejorar la eficiencia. Sin embargo, esta trabajo esta orientado a maximizar la densidad de potencia (en  $A/mm^2$ ) para lograr el uso de este tipo de conversores en sistemas multi-core. Incluso no se reportan datos sobre la potencia mínima entregada a la carga. Reporta una máxima eficiencia de 79.8%.

- [3] implementan un "system on a chip" (SOC) que tiene un  $\mu C$ ,memoria RAM y un conversor DC/DC de capacitores conmutados. El  $\mu C$  y la memoria fueron implementados usando lógica sub-umbral y el conversor DC/DC se usó para implementar la técnica de "escalado de voltaje". Se reporta una eficiencia superior al 75 % en un rango de potencia entregada a la carga de  $10\mu W$  a  $250\mu W$ , y una eficiencia menor al 65 % para potencias menores al  $\mu W$ .

- [12] también presenta un SOC que incluye un microcontrolador basado en un MSP430 (microcontrolador de "Texas Instruments"), memoria, y periféricos además de un conversor DC/DC de capacitores conmutados totalmente integrado. Si bien el conversor alcanza una eficiencia algo por encima de  $80\,\%$  usa un capacitor externo de 3.3nF que influye en la perofrmance del mismo.

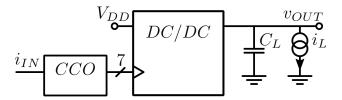

# 1.2. Consideraciones generales sobre conversores DC/DC de capacitores conmutados

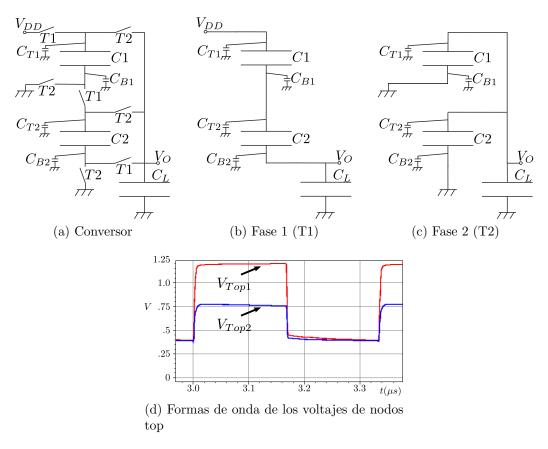

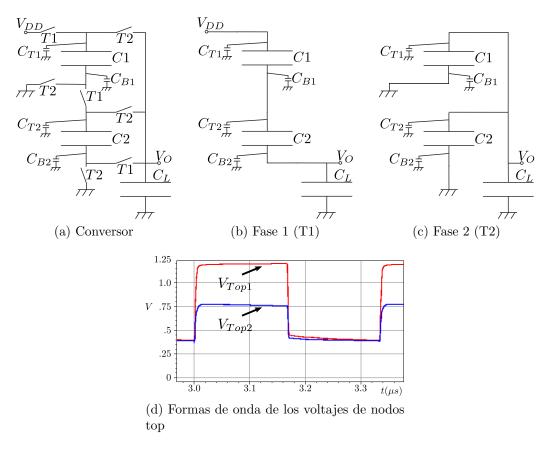

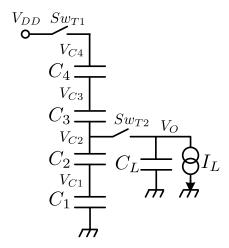

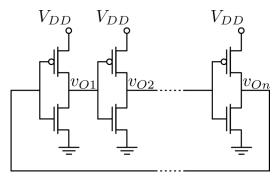

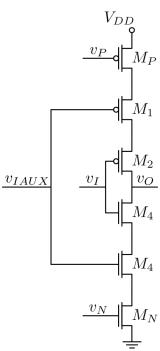

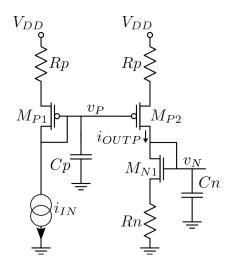

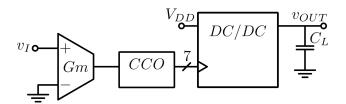

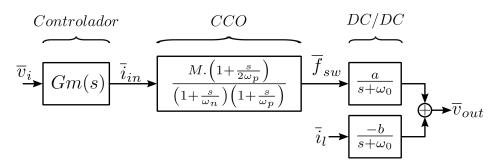

Un conversor DC/DC de capacitores conmutados utiliza un conjunto de condensadores y llaves para poder implementar diferentes configuraciones a las que se les denomina fases. A modo de ejemplo, en la figura 1.2a se muestra un conversor down converter de dos fases con relación de conversión 1/3. En la primera fase

T1 (figura 1.2b), el conversor está tomando energía de la fuente de alimentación  $V_{DD}$ , mientras que en la segunda fase T2 (figura 1.2c) el conversor entrega energía a la carga. En la figura 1.2d se muestran las formas de onda de los voltajes de las placas superiores de C1 y C2 ( $V_{Top1}$  y  $V_{Top2}$  respectivamente). Si bien existen distintos tipos de arquitecturas de conversores en las cuales se pueden tener dos o más fases, lo más usual es que tengan dos como en el ejemplo mostrado. La frecuencia de cada una de las fases se denomina frecuencia de conmutación ( $f_{SW}$ ).

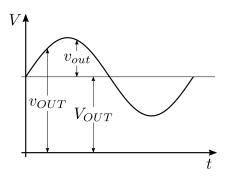

En funcionamiento normal, la entrega de carga se da en un formato cercano a una  $\delta(t)$  (función delta de Dirac). A modo de ejemplo, viendo el conversor de la figura 1.2, la entrega de carga (energía) se da en el comienzo de la fase T2, luego de este impulso de carga la tensión de salida alcanza un máximo para luego comenzar a decaer con una pendiente que depende de la corriente tomada por la carga. Por lo tanto, en sentido estricto la tensión de salida no será constante. Para medir este comportamiento se define el voltaje de ripple  $(V_{Ripple})$  que es la diferencia entre la máxima tensión de salida y la mínima como se muestra en la ecuación 1.2. En un conversor bien diseñado, es de esperar que este parámetro sea bastante menor que la tensión de salida promedio.

$$V_{Ripple} = V_O^{Max} - V_O^{Min} (1.2)$$

En los conversores a capacitores conmutados, el logro de altas eficiencias en comparación con los conversores lineales se basa en la ecuación 1.3. Esta ecuación da la energía disipada al conectar en paralelo dos capacitores Ca y Cb que tienen entre si una diferencia inicial de tensión  $\Delta V$ . De esta ecuación, se evidencia que si la diferencia de tensión inicial  $\Delta V$  es chica, cuando ambos se conecten en paralelo las pérdidas se pueden considerar chicas.

$$E_{Lost} = \frac{Ca.Cb.\Delta V^2}{2.(Ca+Cb)} \tag{1.3}$$

De esta forma, con una frecuencia de conmutación suficientemente alta se puede lograr variaciones de tensión despreciables en cada uno de los capacitores del conversor logrando pérdidas dadas por la ecuación 1.3 también despreciables. En una implementación real, donde las llaves se implementan mediante transistores MOS, ir muy rápido implica tener transistores grandes con lo que aumentan las pérdidas por el manejo de los mismos. Además, los capacitores principales cuentan con capacidades parásitas que implican también un consumo de energía, así como el lazo de control que regula la tensión de salida. No obstante, se logran eficiencias significativamente mejores que las de un conversor lineal. Más adelante se hace una definición formal de los diferentes tipo de pérdidas y de la eficiencia.

Figura 1.2: Conversor típico con relación de conversión 1/3.

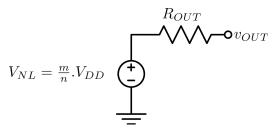

### Modelo de un conversor DC/DC de capacitores conmutados

Si bien un conversor DC/DC de capacitores conmutados es un circuito no lineal, existe un modelo lineal promediado<sup>1</sup> de tiempo continuo que describe de forma compacta su comportamiento general. Dicho modelo es similar al de un modelo Thevenin de un circuito lineal y es el que se muestra en la figura 1.3. Por un lado, al igual que el equivalente Thevenin, se tiene la tensión de circuito abierto que se obtiene viendo la tensión de salida cuando la corriente de carga es cero. A esta tensión se la llama voltaje sin carga  $(V_{NL})$ . Dicha tensión es una fracción entera de la fuente de alimentación  $(\frac{m}{n}.V_{DD})$ .

Por otro lado, se tiene la resistencia equivalente de salida  $R_{OUT}$ . El cálculo de esta resistencia es complicado y de hecho no existe un modelo general que permita tener una expresión exacta. Sin embargo, como se analiza en [13], existe un método

<sup>&</sup>lt;sup>1</sup>Un modelo promediado solo tiene en cuenta el promedio de las sañales del conversor. Esto significa que deja de lado las variaciones en torno a dicho promedio (como por ejemplo el ripple en el caso de la tensión de salida) a cambio de una mayor simplicidad para el análisis.

Figura 1.3: Modelo promediado lineal de un conversor DC/DC de capacitores conmutados.

para calcular dicha resistencia de forma aproximada pero que tiene resultados que se acercan mucho al valor real. Dicho método se basa en calcular la resistencia  $R_{OUT}$  para los casos límites en que la frecuencia de conmutación es muy lenta (a este modo de funcionamiento se le denomina "slow switching limit" (SSL)) y en el caso en que dicha frecuencia es muy rápida (a este modo de funcionamiento se le denomina "fast switching limit" (FSL)) <sup>2</sup>. A dichas resistencias se las denomina  $R_{SSL}$  y  $R_{FSL}$  respectivamente. Luego, la resistencia  $R_{OUT}$  se puede aproximar como la raíz cuadrada de la suma cuadrática de ambas resistencias como lo muestra la ecuación 1.4.

$$R_{OUT} = \sqrt{R_{SSL}^2 + R_{FSL}^2} \tag{1.4}$$

Como se ve en [13], para  $R_{SSL}$  y  $R_{FSL}$  existen métodos que permiten calcularlas de forma exacta. La aproximación se encuentra en usar la ecuación 1.4 como resistencia válida para todas las frecuencias de conmutación. Sin embargo, como ya se mencionó, dicha aproximación arroja muy buenos resultados.

### Calculo de $R_{SSL}$ para el conversor de la figura 1.2

Como se verá en la sección 1.2.2, este tipo de conversores, en la mayoría de los casos se utilizan en modo Slow Switching Limit. Por lo tanto, el calculo de  $R_{SSL}$  es de gran importancia. Para calcular  $R_{SSL}$ , se debe expresar la carga que pasa por cada capacitor en cada una de las fases, como una fracción de la carga entregada en un período de conmutación. Estas cargas se agrupan en lo que se denominan vectores de carga donde cada vector se corresponde con una de las fases (dos en nuestro caso). En [13] se hace un desarrollo detallado de este cálculo. La ecuación 1.5 muestra los vectores de carga ( $\mathbf{a}^1$  y  $\mathbf{a}^2$ ) para el caso del conversor de la figura 1.2.

$$\mathbf{a^1} = \begin{bmatrix} q_{C1_{T1}} & q_{C2_{T1}} \end{bmatrix} / qout$$

$$\mathbf{a^2} = \begin{bmatrix} q_{C1_{T2}} & q_{C2_{T2}} \end{bmatrix} / qout$$

(1.5)

$<sup>^2</sup>$ Cuando se menciona que la frecuencia de conmutación es muy "lenta" ("rápida") lo que se quiere decir es que la duración de cada fase es mucho mayor (menor) que las constantes de tiempo  $\tau$  del sistema.

Por un lado, si planteamos las ecuaciones de Kirchiff para ambas fases, llegamos a las ecuaciones 1.6, 1.7, 1.8 y 1.9.

$$q_{C1_{T1}} = q_{C2_{T1}} = q_{out_{T1}} (1.6)$$

$$V_O + V_{C1_{T1}} + V_{C2_{T1}} = V_{DD} (1.7)$$

$$q_{C1_{T2}} + q_{C2_{T2}} = q_{out_{T2}} (1.8)$$

$$V_O = V_{C1_{T2}} = V_{C2_{T2}} \tag{1.9}$$

Por otro lado, asumiendo que estamos en estado estable (la carga neta en un período de conmutación en cada condensador es nula), llegamos a las ecuaciones 1.10 y 1.11.

$$q_{C1_{T1}} + q_{C1_{T2}} = 0 (1.10)$$

$$q_{C2_{T1}} + q_{C2_{T2}} = 0 (1.11)$$

La ecuación 1.12 muestra el balance de carga en la salida.

$$q_{out} = q_{out_{T1}} + q_{out_{T2}} (1.12)$$

Asumiendo que las variaciones de tensión en los condensadores entre fase y fase son despreciables, se llega a que  $V_{C1_{T1}} = V_{C1_{T2}}$  y  $V_{C2_{T1}} = V_{C2_{T2}}$ . Usando estos resultados y las ecuaciones 1.7 y 1.9, llegamos a la ecuación 1.13.

$$V_O = \frac{V_{DD}}{3} \tag{1.13}$$

Aplicando la conservación de la energía llegamos a la ecuación  $V_{DD}.q_{out_{T1}} = V_O.(q_{out_{T1}} + q_{out_{T2}})$ . Luego, usando 1.13 llegamos a la ecuación 1.14.

$$q_{out_{T2}} = 2.q_{out_{T1}}$$

(1.14)

Usando 1.14 en 1.12 llegamos a 1.15 y 1.16.

$$q_{out_{T1}} = \frac{1}{3}.q_{out} \tag{1.15}$$

$$q_{out_{T2}} = \frac{2}{3}.q_{out} (1.16)$$

Sustituyendo 1.15 en 1.6 llegamos a la ecuación 1.17.

$$q_{C1_{T1}} = q_{C2_{T1}} = \frac{1}{3}.q_{out} (1.17)$$

Luego, usando 1.10, 1.11 y 1.17 llegamos a 1.18.

$$q_{C1_{T2}} = q_{C2_{T2}} = -\frac{1}{3}.q_{out} (1.18)$$

A partir de estos resultados se pueden construir los vectores de carga como se muestra en la ecuación 1.19.

$$\mathbf{a^1} = \begin{bmatrix} (1/3) & (1/3) \end{bmatrix}$$

$$\mathbf{a^2} = \begin{bmatrix} -(1/3) & -(1/3) \end{bmatrix}$$

(1.19)

El cálculo de la resistencia  $R_{SSL}$  se realiza usando la ecuación 1.20.

$$R_{SSL} = \sum_{i \in Cans} \sum_{j=1}^{n} \frac{(aci)^2}{2.Ci.f_{SW}}$$

(1.20)

Sustituyendo 1.19 en 1.20 y asumiendo que C1 = C2 llegamos a la ecuación de la resistencia de salida que se muestra en la ecuación 1.21.

$$R_{SSL} = \frac{2}{9.C1} \cdot \frac{1}{f_{SW}} = \frac{K_{SSL}}{f_{SW}} \tag{1.21}$$

# 1.2.1. Pérdidas y eficiencia en un conversor DC/DC de capacitores conmutados

A continuación, se definen la energía y potencia entregada a la carga y los distintos tipos de pérdidas que existen en un conversor real para luego definir su eficiencia.

#### Energía entregada a la carga

La potencia instantánea entregada a la carga es la que se muestra en la ecuación 1.22 donde  $V_O(t)$  es la tensión de salida e  $I_L(t)$  es la corriente entregada a la carga. Si asumimos que la corriente de carga es aproximadamente constante en un período de conmutación, se pude calcular la potencia promedio entregada a la carga según la ecuación 1.23.

$$P_{Load}(t) = V_O(t).I_L(t) \tag{1.22}$$

$$P_{Load} = \frac{1}{T_{SW}} \cdot \int_{0}^{T_{SW}} P_{Load}(t) \cdot dt = \left(\frac{1}{T_{SW}} \cdot \int_{0}^{T_{SW}} V_{O}(t) \cdot dt\right) \cdot I_{L} = \overline{V_{O}} \cdot I_{L} \quad (1.23)$$

Luego, para calcular la energía entregada a la carga  $E_{Load}$  durante un período de conmutación se tiene la relación de la ecuación 1.24.

$$E_{Load} = \frac{P_{Load}}{f_{SW}} \tag{1.24}$$

Figura 1.4: Llaves usadas en conversores DC/DC de capacitores conmutados.

### Pérdidas por conducción

Como se muestra en la figura 1.3, dada la existencia de la resistencia  $R_{OUT}$  siempre que se entregue corriente a la carga habrá una disipación de potencia en la misma. Esta potencia se muestra en la ecuación 1.25 y se le denomina "pérdidas por conducción". Dicha potencia representa las pérdidas de energía intrínsecas al proceso de transferir/tomar carga a/de un condensador.

$$P_{Cond} = \left(V_{NL} - \overline{V_O}\right) . I_L = R_{OUT} . I_L^2 \tag{1.25}$$

Otra conclusión que se puede sacar de la figura 1.3 es que no es posible alcanzar el voltaje  $V_{NL}$  si se entrega potencia a la carga, debido a la caída inevitable de tensión que aparece en  $R_{OUT}$ . Por lo tanto, cuando se regule la tensión de salida deberá hacerse a una tensión menor a  $V_{NL}$ .

Por otro lado, se tiene la energía consumida debido a la conducción en un período de conmutación que se muestra en la ecuación 1.26.

$$E_{Cond} = \frac{P_{Cond}}{f_{SW}} \tag{1.26}$$

De la ecuación 1.25 se puede ver que dichas pérdidas dependen de la diferencia de tensión entre  $V_{NL}$  y  $\overline{V_O}$ , y de la corriente de carga  $I_L$ .

Un punto importante a tener en cuenta, es que para las ecuaciones 1.23 y 1.25 se asume que la carga es una fuente de corriente cuyo valor es aproximadamente constante en un período de conmutación  $T_{SW}$ . Sin embargo, si la carga fuera del tipo resistiva, como se analiza en [11] las ecuaciones 1.23 y 1.25 también van a depender del voltaje de ripple  $V_{Ripple}$ .

#### Pérdidas de gate-drive

Las llaves usadas en conversores DC/DC de capacitores conmutados son como la que se muestra en la figura 1.4, las cuales consisten en conectar un transistor NMOS y uno PMOS en paralelo.

De esta forma, el encendido y apagado de las llaves se logra mediante la carga y descarga del gate de los transistores que componen la llave. Salvo que se aplique algún tipo de técnica especial para el manejo de estos componentes, los gates de estos transistores tienen variaciones de tensión entre 0 y la fuente de alimentación  $V_{DD}$  a la hora de cerrar/abrir la llave.

Teniendo en cuenta que la potencia disipada debido a cargar y descargar un capacitor  $C_L$  a una frecuencia f entre 0 y  $V_{DD}$  es la que se muestra en la ecuación 1.27, es posible calcular la potencia consumida debido al manejo de las llaves.

$$P_{Din} = f.C_L.V_{DD}^2 (1.27)$$

De esta forma, la potencia de gate-drive consumida es aproximadamente la que se muestra en la ecuación 1.28. En la misma,  $C_{ox}'$  es la capacidad por unidad de área del gate de los transistores,  $L_{min}$  es el largo mínimo de transistor permitido por la tecnología,  $W_i$  es el ancho del i-ésimo transistor, y  $\alpha_{SWi}$  es tal que  $f_i = \alpha_{SWi}.f_{SW}$  donde  $f_i$  es la frecuencia con la que se enciende y apaga el i-ésimo transistor.

$$P_{SW} = f_{SW}.C'_{ox}.L_{min}.\left(\sum_{i=1}^{n} \alpha_{SWi}.W_{i}\right).V_{DD}^{2}$$

(1.28)

Es importante notar que la potencia de gate-drive es directamente proporcional con la frecuencia de conmutación  $f_{SW}$ . Luego, se puede calcular la energía consumida por gate-drive dividiendo por la frecuencia de conmutación como se muestra en la ecuación 1.29.

$$E_{SW} = \frac{P_{SW}}{f_{SW}} = C'_{ox}.L_{min}.\left(\sum_{i=1}^{n} \alpha_{SWi}.W_i\right).V_{DD}^2$$

(1.29)

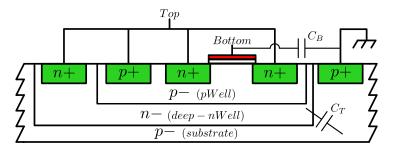

#### Pérdidas por capacidades parásitas de top/bottom plate

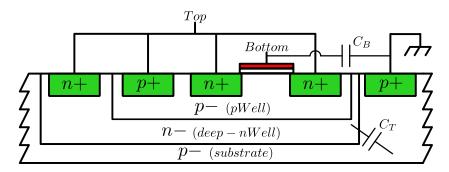

Los capacitores integrados cuentan con capacidades parásitas desde cada una de sus placas a sustrato. Estas capacidades son denominadas como "capacidades parásitas de top/bottom plate" (CPTBP). Una forma de implementar un capacitor es utilizando la capacidad de gate de los transistores. Para que los mismos sean flotantes (es decir que ninguno de sus terminales estén conectados a una tensión fija) es necesario o bien usar transistores PMOS, o transistores NMOS de doble pozo si la tecnología cuenta con la opción, como se muestra en la figura 1.5. En dicha figura se muestra esta implementación con sus correspondientes capacidades parásitas  $C_T$  y  $C_B$ . Por otro lado, en las tecnologías más nuevas se tienen capacitores metal-insulator-metal (MIM) que se implementan en capas altas de metal por lo que no tienen capacidades parásitas significativas a sustrato. Sin embargo, por razones que se analizan en el capitulo 2 (área y densidad de potencia) sigue teniendo sentido el uso de los capacitores MOS y por lo tanto se deben tener en cuenta las CPTBP a la hora de hacer el análisis de las pérdidas.

Figura 1.5: Capacitor NMOS de triple pozo con sus capacidades parásitas.

Como en cada cambio de fase la mayoría de los capacitores cambian sus voltajes referidos a tierra, se genera una carga/descarga de las CPTBP lo cual genera pérdidas de energía. La potencia disipada debido a este efecto es la que se muestra en la ecuación 1.30. En la misma  $f_{SW}$  nuevamente es la frecuencia de conmutación,  $C'_{par} = C'_{top} + C'_{bottom}$  es la capacidad total por unidad de área de las CPTBP,  $A_i$  es el área equivalente considerada para las capacidades parásitas del i-ésimo capacitor  $^3$ , y  $V_{DD}$  la alimentación. La constante  $\alpha_{f_{SW}i}$  cumple que  $f_i = \alpha_{f_{SW}i}.f_{SW}$  donde  $f_i$  es la frecuencia de conmutación de las CPTBP del i-ésimo condensador. La constante  $\alpha_{V_{DD}i}$  cumple que  $\Delta Vi = \sqrt{\alpha_{V_{DD}i}}.V_{DD}$  donde  $\Delta Vi$  es la variación de tensión de las CPTBP del i-ésimo capacitor.

$$P_{CPar} = f_{SW}.C'_{par}.\left(\sum_{i=1}^{n} \alpha_{V_{DD}i}.\alpha_{f_{SW}i}.A_{i}\right).V_{DD}^{2}$$

(1.30)

En la ecuación 1.30 se puede ver que la potencia disipada en este caso es proporcional a la frecuencia de conmutación  $f_{SW}$ . Por lo tanto, si se quiere calcular la energía consumida en un período de conmutación  $T_{SW}$ , dicha ecuación se debe dividir por  $f_{SW}$ , de esta forma  $E_{CPar}$  nos queda según la ecuación 1.31.

$$E_{CPar} = C'_{par} \cdot \left( \sum_{i=1}^{n} \alpha_{V_{DD}i} \cdot \alpha_{f_{SW}i} \cdot A_i \right) \cdot V_{DD}^2$$

(1.31)

#### Pérdidas por el lazo de control

Por último, siempre es necesario tener una lógica que maneje el conversor y que sea parte de un lazo de control que regula la tensión de salida. Esta lógica puede disipar una potencia proporcional a la frecuencia de conmutación si es puramente digital, o puede tener un término proporcional a la frecuencia de conmutación y un término constante que se corresponde con algún circuito analógico. La ecuación 1.32 expresa lo antes mencionado. En la misma,  $\alpha_{Ci}$  cumple que  $f_i = \alpha_{Ci}.f_{SW}$

$<sup>^{3}</sup>$ Si bien esta área sera diferente para  $C_{T}$  y  $C_{B}$ , es posible considerarlas iguales tomando la misma área para los dos e incorporando la diferencia correspondiente en los valores considerados de  $C'_{top}$  y  $C'_{bottom}$ .

donde  $f_i$  es la frecuencia de conmutación del i-ésimo nodo de la lógica, Ci es la capacidad del i-ésimo nodo de la lógica, e  $I_{An}$  es la corriente constante consumida por el circuito analógico (si las corrientes de fuga no fueran despreciables, se pueden incluir en este término).

$$P_{Logic} = f_{SW} \cdot \left(\sum_{i=1}^{n} \alpha_{Ci} \cdot Ci\right) \cdot V_{DD}^{2} + I_{An} \cdot V_{DD}$$

(1.32)

Para obtener la energía consumida en un período de conmutación  $T_{SW}$  se debe dividir la ecuación 1.32 por  $f_{SW}$ . Por lo tanto, la energía  $E_{Logic}$  es la mostrada en la ecuación

$$E_{Logic} = \left(\sum_{i=1}^{n} \alpha_{Ci}.Ci\right).V_{DD}^{2} + \frac{I_{An}.V_{DD}}{f_{SW}}$$

(1.33)

### Eficiencia de un conversor DC/DC de capacitores conmutados

La eficiencia de un conversor de energía se define como la potencia entregada a la carga, dividido la potencia tomada de la fuente. Dado que la potencia tomada de la carga se compone de la entregada a la carga y todas las pérdidas, la eficiencia para un conversor DC/DC de capacitores conmutados se define según la ecuación 1.34.

$$\eta_{P} = \frac{P_{Load}}{P_{Load} + P_{Cond} + P_{CPar} + P_{SW} + P_{Logic}}$$

(1.34)

Para expresar la eficiencia en términos de la energía consumida en un período de conmutación basta con multiplicar y dividir la ecuación 1.34 por  $f_{SW}$ . De esta forma, la eficiencia expresada en términos de energía es la que se muestra en la ecuación 1.35.

$$\eta_E = \frac{E_{Load}}{E_{Load} + E_{Cond} + E_{CPar} + E_{SW} + E_{Logic}}$$

(1.35)

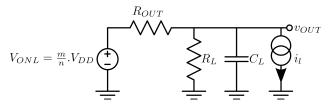

# 1.2.2. Regulación de la tensión de salida y sus implicancias en la eficiencia

Dado que con este tipo de circuitos se busca entregar a la carga una tensión constante, es necesario regular dicha tensión mediante un lazo de control. Como se puede apreciar de la figura 1.3, regular la tensión de salida es equivalente a lograr una caída de tensión constante en la resistencia  $R_{OUT}$ . Por lo tanto, para obtener una determinada tensión de salida se debe elegir la relación de conversión adecuada para luego variar algún/os parámetro/s de la resistencia de salida en función de la corriente de carga.

Como se mencionó previamente, el valor de dicha resistencia se puede aproximar mediante le ecuación 1.4. A continuación se hace un análisis de los parámetros que definen tanto a  $R_{SSL}$  como a  $R_{FSL}$  para poder seleccionar el o los parámetros que se pueden usar para regular la tensión de salida (un analisis más profundo de estas resistencias equivalentes se puede encontrar en [13]). La resistencia de Fast Switching Limit  $R_{FSL}$  depende de la arquitectura del conversor y de las resistencias de las llaves, mientras que la resistencia de Slow Switching Limit  $R_{SSL}$  depende de la arquitectura del conversor, las capacidades que lo componen, y de la frecuencia de conmutación  $f_{SW}$ .

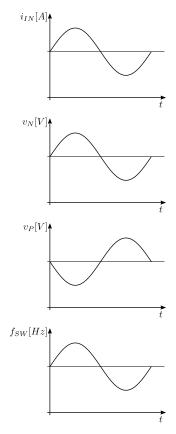

De todos estos parámetros, el único que se puede variar de forma continua y en tiempo real, es la frecuencia de conmutación  $f_{SW}$ . Por esta razón, en general se usa dicho parámetro para regular la tensión de salida y se trabaja en Slow Switching Limit. La resistencia de salida se puede aproximar según la ecuación 1.36. En la misma, se deja explícita la dependencia inversamente proporcional de  $R_{OUT}$  con  $f_{SW}$ .

$$R_{OUT} \simeq R_{SSL} = \frac{K_{SSL}}{f_{SW}} \tag{1.36}$$

La caída de tensión en la resistencia de salida será por lo tanto la que se muestra en la ecuación 1.37. De la misma se desprende que la regulación de la tensión de salida se logra variando la frecuencia de conmutación  $f_{SW}$  proporcional a la corriente de carga  $i_L$

$$V_{R_{OUT}} = \left(V_{NL} - \overline{V_O}\right) = R_{SSL} \cdot i_L = \frac{K_{SSL}}{f_{SW}} \cdot i_L \tag{1.37}$$

La relación entre  $f_{SW}$  e  $i_L$  será la que se muestra en la ecuación 1.38 cuyos términos son todos constantes.

$$\frac{i_L}{f_{SW}} = \frac{\left(V_{NL} - \overline{V_O}\right)}{K_{SSL}} = K_{Reg} \tag{1.38}$$

La relación lineal entre la corriente de carga y la frecuencia de conmutación tiene como corolario que la eficiencia del conversor se mantiene constante dentro del rango de funcionamiento normal del mismo. Esto se puede ver al analizar la ecuación 1.34. Por un lado, de las ecuaciones 1.28, 1.30 y 1.32 se puede ver que  $P_{SW}$ ,  $P_{CPar}$  y  $P_{Logic}$  tienen una dependencia lineal con la frecuencia de conmutación <sup>4</sup>. Por otro lado, combinando las ecuaciones 1.25 y 1.38 se tiene que  $P_{Cond} = (V_{NL} - \overline{V_O}) .K_{Reg}.f_{SW}$ , y combinando las ecuaciones 1.23 y 1.38 se tiene que  $P_{Load} = \overline{V_O}.K_{Reg}.f_{SW}$ . De este análisis se desprende que en un conversor regulado, todos los términos de la ecuación 1.34 son proporcionales a la frecuencia de conmutación  $f_{SW}$ . Por este motivo, dicha ecuación se puede rescribir como la

$<sup>^4</sup>$ Si bien  $P_{Logic}$  en general puede tener un término constante, el término que depende linealmente con la frecuencia de conmutación va a dominar a partir de una cierta frecuencia

Figura 1.6: Ejemplo de gráfica de eficiencia en función de la corriente de carga  $i_L$  para un convesor regulado y trabajando en modo slow switching limit.

ecuación 1.39 en donde se puede ver que efectivamente si la tensión de salida es constante, todos los términos de dicha ecuación también lo serán.

$$\eta_{cte} = \frac{\overline{V_O}.K_{Reg}}{\overline{V_O}.K_{Reg} + \left(V_{NL} - \overline{V_O}\right).K_{Reg} + E_{CPar} + E_{SW} + E_{Logic}}$$

(1.39)

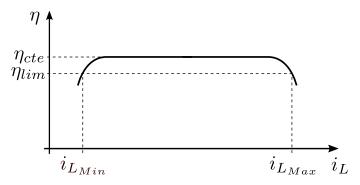

Las dos hipótesis principales realizadas para alcanzar la ecuación 1.39 son que el término independiente de  $f_{SW}$  de la ecuación 1.32 es despreciable frente a los otros términos del denominador de la ecuación 1.34, y que se está trabajando en modo Slow Switching Limit. Por un lado, cuando la potencia entregada a al carga es suficientemente chica y sigue decreciendo, se alcanzará un punto a partir del cual se deja de cumplir la primer hipótesis. Por lo tanto, a partir de ahí el término independiente de  $f_{SW}$  de la ecuación 1.32 se torna cada vez más significativo y la eficiencia comienza a decaer. Por otro lado, si la corriente de carga aumenta (y según la ecuación 1.38 también lo hace  $f_{SW}$ ), se llegará a un punto donde la segunda hipótesis deja de ser válida y se entra en modo Fast Swtiching Limit. En este punto, la tensión de salida comenzará a caer por falta de regulación, por lo que la eficiencia también caerá. En la figura 1.6, se muestra una gráfica que ejemplifica la curva de la eficiencia en función de la corriente de carga  $i_L$ . En la misma, se aprecia una zona plana correspondiente a la eficiencia constante  $\eta_{cte}$ , además se aprecia como la curva decae a partir de las corrientes  $i_{L_{Min}}$  e  $i_{L_{Max}}$ .

A continuación se hace un análisis sobre como abordar el punto  $(i_{L_{Min}}, \eta_{lim})$ . Como primer paso debemos definir la relación que existe entre el valor de la eficiencia en la zona plana de la curva  $\eta_{cte}$  y la eficiencia del punto en cuestión  $\eta_{lim}$ . Esta relación se define según la ecuación 1.40. El valor de este parámetro es arbitrario y dependerá de la tolerancia de cada aplicación a la pérdida de eficiencia.

$$K_{eff} = \frac{\eta_{lim}}{\eta_{cte}} \tag{1.40}$$

Por otro lado, la ecuación 1.39 la vamos a expresar como  $\eta_{cte} = \frac{P_L}{P_L + P_{Losses}}$ , donde  $P_{Losses}$  incluye todas las pérdidas del conversor a excepción del término

independiente de  $f_{SW}$  de la ecuación 1.32. De dicha ecuación, podemos despejar la relación que existe entre la  $P_L$  y  $P_{Losses}$  lo que nos da la ecuación 1.41.

$$\frac{P_{Losses}}{P_L} = \frac{1 - \eta_{cte}}{\eta_{cte}} \tag{1.41}$$

La ecuación de la eficiencia que también considera el término independiente de  $f_{SW}$  de la ecuación 1.32 se puede expresar como se muestra en la ecuación 1.42 donde  $P_{An} = I_{An}.V_{DD}$  es dicho término.

$$\eta_{lim} = \frac{P_{Load}}{P_{Load} + P_{Losses} + P_{An}} \tag{1.42}$$

Luego, combinando las ecuaciones 1.40, 1.41 y 1.42, llegamos a la ecuación 1.43 que muestra la relación ente la potencia entregada a al carga  $P_{Load}$  (cuando la corriente es  $i_{L_{Min}}$ ) y  $P_{An}$  en función de  $\eta_{cte}$  y  $K_{eff}$ .

$$\frac{P_{An}}{P_{Load}} = \left(\frac{1 - K_{eff}}{K_{eff}}\right) \cdot \frac{1}{\eta_{cte}} \tag{1.43}$$

Si seguimos trabajando sobre la ecuación 1.43, podemos obtener la relación que existe entre  $I_{An}$  y la potencia mínima entregada a la carga. Esto da como resultado la ecuación 1.44.

$$I_{An} = \frac{P_{L_{Min}}}{V_{DD}} \cdot \left(\frac{1 - K_{eff}}{K_{eff}}\right) \cdot \frac{1}{\eta_{cte}}$$

(1.44)

Esta ecuación puede ser usada de dos formas. Por un lado, si tenemos circuitos analógicos que consumen una cierta corriente  $I_{An}$ , la ecuación nos va a decir para cada relación de conversión y cada tensión de salida  $\overline{V_O}$  cual es la mínima potencia que puedo entregar a la carga. Por otro lado, si tenemos como objetivo alcanzar una cierta potencia mínima entregada a la carga  $P_{L_{Min}}$ , esta ecuación nos va a decir cuánta corriente tenemos para polarizar los circuitos analógicos en caso de que los necesitemos.

### 1.2.3. Reciclado de carga

El funcionamiento normal de un conversor DC/DC de capacitores conmutados hace que se genere una carga y descarga sistemática de capacidades parásitas. Estos procesos de carga y descarga generan pérdidas de energía que de una forma u otra provienen de la fuente de alimentación. Como esta energía no llega a la carga (se disipa en la resistencia de las llaves) este fenómeno implica una disminución en la eficiencia como se puede ver en la ecuación 1.34. Cuando se habla de reciclado de carga se habla de usar parte de la energía que naturalmente se disipa en las llaves debido a estos procesos para darle una utilidad que permite mejorar la eficiencia del conversor. En particular, en lugar de "tirar" la carga de las capacidades parásitas que en un determinado momento se estan descargando, se reutilizan para cargar otras capacidades parásitas que necesitan ser cargadas.

### Organización del documento

En esta tesis, se verá en el capitulo 2 el estudio de técnicas generales de reciclado de carga tanto para disminuir las pérdidas debido a las CPTBP  $(E_{CPar})$ , como para las pérdidas debido al manejo de las llaves  $(E_{SW})$ . En el capítulo 3 se presentan los resultados de simulación y medidas de un conversor de arquitectura modular. Gracias a la regularidad de dicha arquitectura, la técnica de reciclado de carga de las CPTBP se implementa de una forma más sencilla. En el capítulo 4 se presentan dos circuitos usados para implementar el lazo de control en los que se aplican técnicas novedosas para reducir el consumo. En el capítulo 5 se hace un análisis del lazo de control aplicado al conversor presentado en el capítulo 3. Por último, en el capítulo 6 se presentan las conclusiones y los trabajos a futuro.

### Capítulo 2

### Técnicas de reciclado de carga

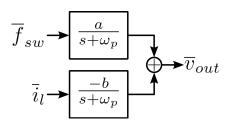

Si se analizan los tipos de pérdidas presentados en la sección 1.2, se puede apreciar que solo las pérdidas de gate-drive y las debido a las capacidades parásitas de top/bottom-plate (CPTBP) pueden ser usadas para reciclar carga. Por un lado, las pérdidas de conducción son intrínsecas a la tensión de salida que deseamos obtener (Figura 1.3) por lo que difícilmente se pueda reciclar algo de carga. Por otro lado, dado que la lógica siempre se implementa con transistores mínimos, hacer un reciclado de carga no tiene sentido ya que cualquier medida que se tome tendrá un costo mayor que el ahorro obtenido. Sin embargo, tanto las pérdidas debido a las CPTBP como a las debido al manejo de las llaves, tiene capacidades suficientemente grandes como para justificar el uso de técnicas de reciclado de carga. En este capítulo se presentan técnicas de reciclado de carga (TRC) para ambos casos.

# 2.1. Técnica general de reciclado de carga para capacidades parásitas de top/bottom-plate

El contenido de esta sección refleja el contenido de la sección II de [14].

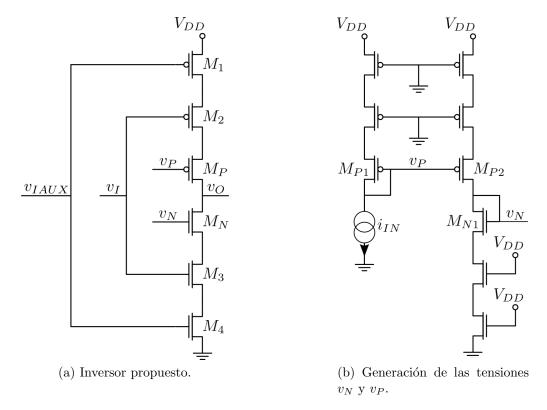

Las pérdidas debido a las CPTBP en un conversor DC/DC de capacitores conmutados provienen del cambio de posición de los condensadores principales en las transiciones de fase. Si bien las CPTBP son mucho menores que las capacidades principales, las variaciones de tensión a las cuales son sometidas en las transiciones de fase son significativas. A modo de ejemplo, en el conversor típico de relación de conversión 1/3 mostrado en la figura 2.1, la variación de voltaje en una transición de fase son  $\frac{2.V_{DD}}{3}$ ,  $\frac{2.V_{DD}}{3}$ ,  $\frac{V_{DD}}{3}$  and  $\frac{V_{DD}}{3}$  para  $C_{T1}$ ,  $C_{B1}$ ,  $C_{T2}$ ,  $C_{B2}$  respectivamente como se puede deducir de la figura 2.1d. Las pérdidas  $(E_{1/3})$  asociadas a un ciclo completo (incluyendo las transiciones Fase1-Fase2 y Fase2-Fase1) es la presentada en la ecuación 2.1, donde se asume que:  $C_{top} = C_{T1} = C_{T2}$ ,  $C_{bottom} = C_{B1} = C_{B2}$ , y  $C_{t/b} = C_{top} + C_{bottom}$ . La deducción para dicha ecuación se presenta en el apéndice A.1.

### Capítulo 2. Técnicas de reciclado de carga

Figura 2.1: Conversor típico con relación de conversión 1/3.

$$E_{1/3} = \frac{5.C_{t/b}.V_{DD}^2}{9} \tag{2.1}$$

Las pérdidas de energía se anotan con la letra E con un sufijo que indica el conversor al cual se hace referencia (ejemplo: 1/3 para el conversor que se considera en esta sección). La identificación del conversor será seguida de las letras RC si la TRC se ha aplicado. Para disminuir las pérdidas por CPTBP , en cada transición de fase es posible transferir energía desde las CPTBP que pierden energía a las que la ganan. Si bien en algunos conversores (como se mostrará en el capitulo 3) se presenta dicha situación (algunas CPTBP ganan energía mientras otras la pierden), en otras arquitecturas comúnmente usadas esta situación no se da y el concepto antes mencionado no puede ser aplicado. Por ejemplo, para el conversor mostrado en la figura 2.1 o bien todas las CPTBP pierden energía, o bien todas ganan. Por lo tanto el concepto de transferir energía desde las capacidades que deben perderla a las que deben ganarla, no se puede aplicar.

Para resolver dicho problema, una técnica conocida es la de usar un reservorio de energía como se presenta en [15] o como se analizará en la sección 2.2, lo cual

# 2.1. Técnica general de reciclado de carga para capacidades parásitas de top/bottom-plate

Figura 2.2: TRC para un conversor general.

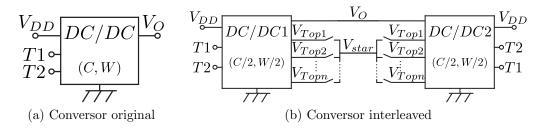

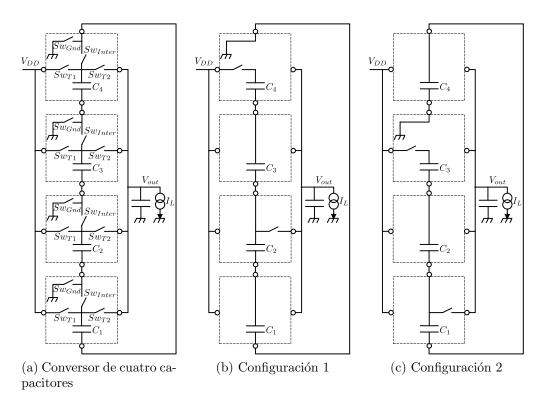

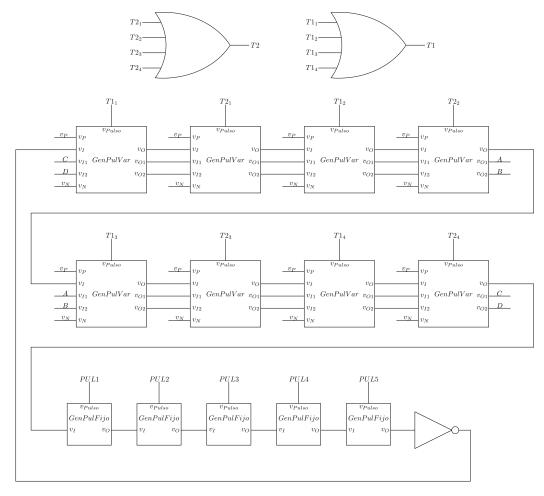

tiene el costo de gastar área extra de silicio. Otra alternativa para tener una solución general, que haga aplicable la técnica independientemente de la arquitectura del conversor, es la técnica propuesta en la presente tesis. La misma consiste en usar dos conversores interleaved ("entrelazados", con capacidades principales C/2 y ancho de llaves W/2) como se muestra en la figura 2.2b, en lugar de usar un conversor simple (con capacidades principales C y ancho de llaves W) como se muestra en la figura 2.2a.

Usar un conversor interleaved no solo tiene el beneficio de disminuir el ripple ( [11] y [16]), sino que además resulta en un conversor con una simetría suficiente como para aplicar la TRC independientemente de la arquitectura original. En cada transición de fase, cada una de las CPTBP del conversor DC/DC 1 que está ganando (perdiendo) energía, tiene su análogo en el conversor DC/DC 2 que está perdiendo (ganando) energía.

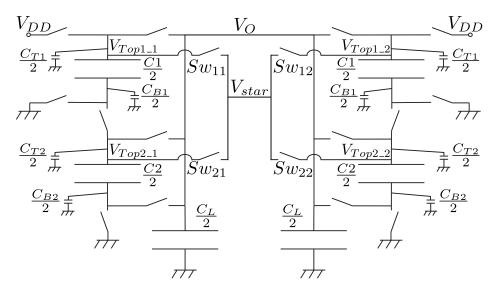

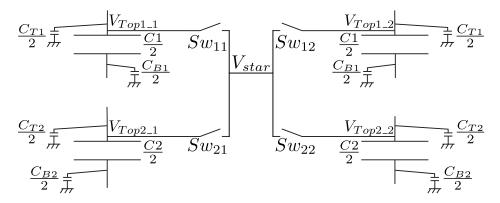

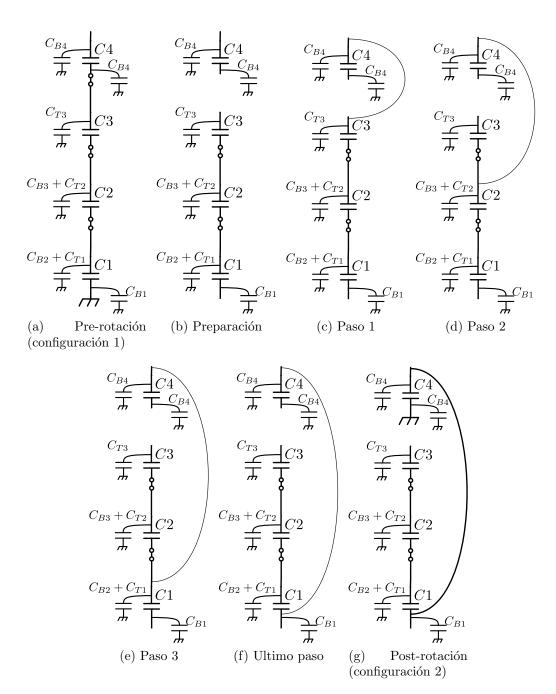

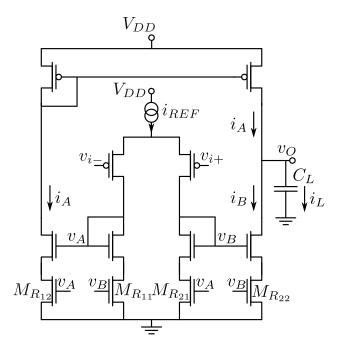

Para implementar la TRC de las CPTBP todos las placas superiores de los capacitores principales (C1 y C2 en el conversor de la figura 2.1) deben ser conectadas a un nodo común ( $V_{star}$  en la figura 2.2b). De esta forma, usando una lógica dedicada para generar los pulsos necesarios puede ser implementada la mencionada técnica. Para el conversor mostrado en la figura 2.1, la implementación da como resultado el conversor interleaved de dos fases como el mostrado en la figura 2.3. Luego, en la figura 2.4 se muestra la implementación de la TRC para este conversor donde se puede ver que justo antes de comenzar el proceso de reciclado de carga, todos los capacitores principales están "flotando" y el voltaje de sus placas superiores (VTop1-1, VTop2-1, VTop1-2 and VTop2-2) referidos a tierra están determinados por la carga en las CPTBP. Las llaves Sw11, Sw21, Sw12, y Sw22 conectan todas las placas superiores de los condensadores principales al nodo  $V_{star}$ .

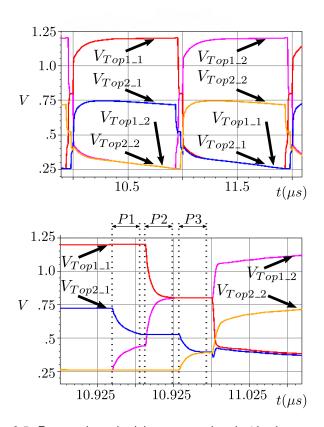

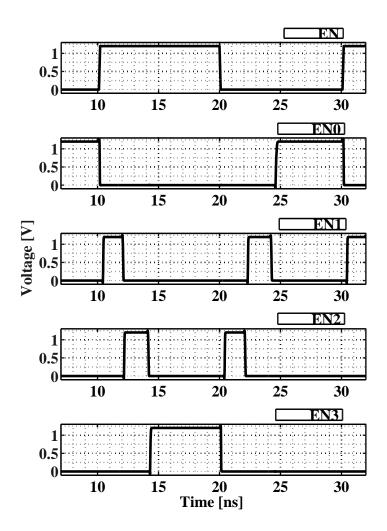

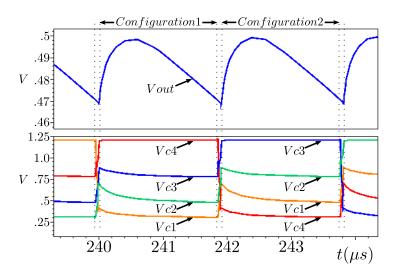

En la figura 2.5 se presentan los voltajes referidos a tierra correspondientes a las placas superiores de los cuatro capacitores principales. En la gráfica superior se muestran las dos fases completas (T1 y T2), donde se puede ver que en la primera fase (T1) el primer conversor interleaved está tomando energía de la fuente de alimentación  $(VTop1\_1 \simeq V_{DD}, VTop2\_1 \simeq (2/3).V_{DD})$ , y el segundo está entregando energía a la carga $(VTop1\_2 \simeq VTop2\_2 \simeq (1/3).V_{DD} \simeq Vo)$ . En la siguiente

### Capítulo 2. Técnicas de reciclado de carga

Figura 2.3: El conversor mostrado en la figura 2.1 con la implementación de la TRC.

Figura 2.4: Conversor de relación de conversión 1/3 preparado para la aplicación de la TRC.

fase (T2) los roles se intercambian. En la parte inferior de la figura 2.5 se presenta un zoom de la transición entre las fases T1 y T2 ilustrando el intercambio de carga entre las CPTBP mediante el uso de tres pulsos  $(P1,\ P2,\ y\ P3)$  no mostrados en la figura. La tabla 2.1 muestra los pares de llaves  $Sw11,\ Sw21,\ Sw12$  y Sw22 (mostrados en la figura 2.4) que se cierran en cada uno de estos pulsos.

En el primer pulso (P1) el intercambio de energía se da desde las CPTBP asociadas a  $VTop2\_1$  hacia las asociadas a  $VTop1\_2$ , en el segundo pulso (P2) el intercambio se da desde las CPTBP asociadas a  $VTop1\_1$  a las asociadas a  $VTop1\_2$ , y finalmente en el tercer pulso (P3) el intercambio se da desde las CPTBP asociadas a  $VTop2\_1$  a las asociadas a  $VTop2\_2$ . La energía disipada en la transición de fase es la expresada en la ecuación 2.2. La deducción de dicha ecuación se puede apreciar en el apéndice A.1. Es importante resaltar que el reciclado de carga de

# 2.1. Técnica general de reciclado de carga para capacidades parásitas de top/bottom-plate

|   |      | P1      | P2      | P3      |

|---|------|---------|---------|---------|

| ĺ | Sw11 | ABIERTO | CERRADO | ABIERTO |

| Ì | Sw12 | CERRADO | CERRADO | ABIERTO |

| ĺ | Sw21 | CERRADO | ABIERTO | CERRADO |

| ĺ | Sw22 | ABIERTO | ABIERTO | CERRADO |

Tabla 2.1: Activación de las llaves que implementan la TRC, según los pulsos de control  $P1,\ P2$  y P3.

Figura 2.5: Formas de onda del conversor de relación de conversión 1/3.

las capacidades de bottom se da en conjunto con la de top. Esto es así porque la capacidad parásita de bottom está conectada en serie con el capacitor principal correspondiente el cual es mucho más grande. Por lo tanto, el capacitor principal actúa como un corto circuito en serie con la capacidad parásita de bottom durante el reciclado de carga (ver figura 2.4).

$$E_{1/3CR} = \frac{C_{t/b} \cdot V_{DD}^2}{4} \tag{2.2}$$

La ecuación 2.3 presenta la relación de pérdidas debido a las CPTBP para los

#### Capítulo 2. Técnicas de reciclado de carga

dos casos (aplicando y no aplicando la TRC), donde se aprecia que dichas pérdidas se reducen al 45 % cuando la TRC es aplicada. Aunque la ecuación 2.3 solo tiene en cuenta las pérdidas debido a cargar y descargar las CPTBP, como se verá más adelante, las pérdidas asociadas a la lógica y las llaves extra que implementan la TRC no tienen un impacto significativo y la eficiencia del conversor se mejorará.

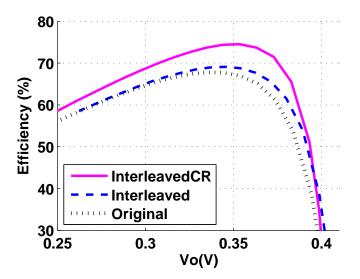

$$S_{1/3} = \frac{E_{1/3CR}}{E_{1/3}} = \frac{9}{20} \tag{2.3}$$

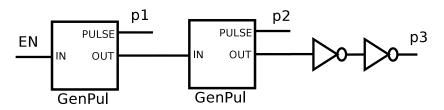

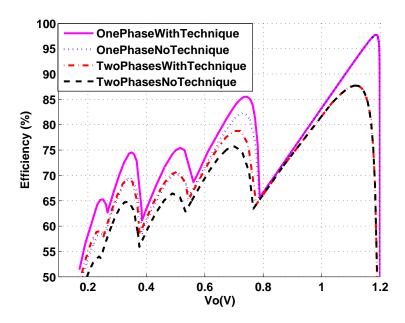

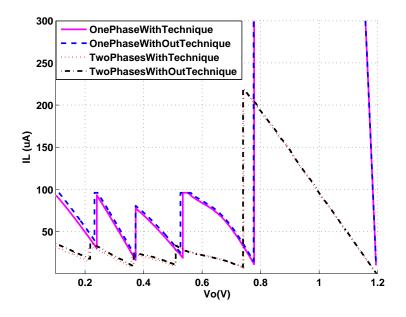

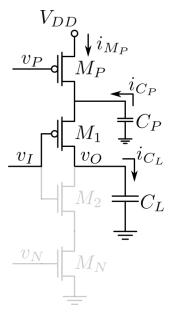

Para mostrar la efectividad de la TRC, se implementó y se probó a nivel de simulaciones el conversor que se presenta en la figura 2.1. Las simulaciones fueron realizadas usando una tecnología "CMOS" de 130nm, el valor de las capacidades C1, C2, y CL es de 580pF. La tensión de alimentación usada es de 1,2V, el rango de tensión de salida es de 0.25V - 0.39V, y la máxima potencia entregado a la carga es de  $240\mu W$ . Todos los condensadores se construyeron a partir de transistores "NMOS" de triple pozo, y la lógica y las llaves implementadas con transistores MOS de bajo consumo. La figura 2.6 muestra la implementación de los capacitores principales y se resaltan las capacidades parásitas de top  $(C_T)$  y bottom  $(C_B)$ . En este caso, la capacidad parásita de bottom es despreciable frente a la de top. El valor de la capacidad parásita de top está un poco por debajo del 10% respecto de la capacidad principal. La eficiencia resultante (simulación del esquemático) en función del voltaje de salida se muestra en la figura 2.7. Esta eficiencia tiene en cuenta las pérdidas debido a la lógica (incluyendo la lógica auxiliar cuando la TRC es aplicada), las de gate-drive (incluyendo las llaves auxiliares cuando la TRC es aplicada), CPTBP y conducción. La lógica que genera los pulsos auxiliares fue generada a partir de un circuito similar al presentado en la sección 4.1. En la figura 2.7 se aprecian tres curvas: la primera corresponde al conversor original ("Original"), la segunda al conversor interleaved ("Interleaved"), y la tercera al conversor interleaved incluyendo la TRC ("InterleavedCR"). Como se puede apreciar de dichas curvas, usar un conversor interleaved mejora la eficiencia debido a la disminución del ripple pero no de forma significativa, esto se debe a que se necesitan más fases para obtener una mejora mayor [11]. Sin embargo, con un conversor interleaved de solo dos fases, se logra una mejora significativa en la eficiencia si se aplica la TRC propuesta. A modo de ejemplo, para un voltaje de salida de Vo = 0.35V, la mejora en la eficiencia tiene una mejora de siete puntos porcentuales que va desde el 67,5 % al 74,5 %.

### 2.2. Reciclado de carga del gate de las llaves

Como se menciona en la sección 1.2.1, otra de las pérdidas presentes en este tipo de conversores son las debidas al manejo de las llaves. En general, las llaves usadas son significativamente grandes y cuentan con capacidades de gate que generan un consumo suficiente para degradar la eficiencia del conversor. Por ejemplo, en [9] para una potencia entregada a la carga de  $100\mu W$  se logra una eficiencia de 76,3%. Las pérdidas por manejo de las llaves en este caso genera una pérdida de

# 2.2. Reciclado de carga del gate de las llaves

Figura 2.6: Implementación de los capacitores principales usando transistores NMOS de triple pozo.

Figura 2.7: Resultados de simulación de eficiencia vs. voltaje de salida para el conversor de relación de conversión 1/3.

eficiencia de 4%.

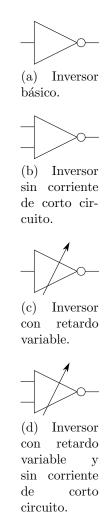

Por lo tanto, toda técnica que pueda ser usada para disminuir las pérdidas de este tipo tendrá un impacto favorable en términos de la eficiencia del conversor. Una conocida técnica que permite mejorar la eficiencia de carga y descarga de una capacidad es la llamada "adiabatic switching" que consiste en cargar la capacidad a partir de una fuente de corriente constante y con un tiempo de carga T mucho mayor a la constante de tiempo  $\tau$  ( [17], [18]). Esto permite en un caso límite  $\tau \ll T$  lograr pérdidas que se pueden considerar despreciables a costa de disminuir la frecuencia de carga y descarga de la capacidad en cuestión. El problema de este tipo de técnicas es que necesitan de inductores [18] (los cuales tienen factores de calidad bajos )y funcionan para una frecuencia fija y dependiente de la capacidad a manejar la cual en general tiene un valor con mucha incertidumbre.

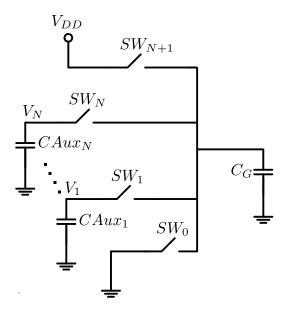

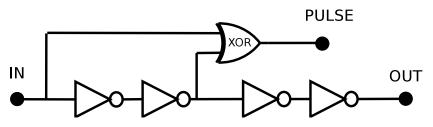

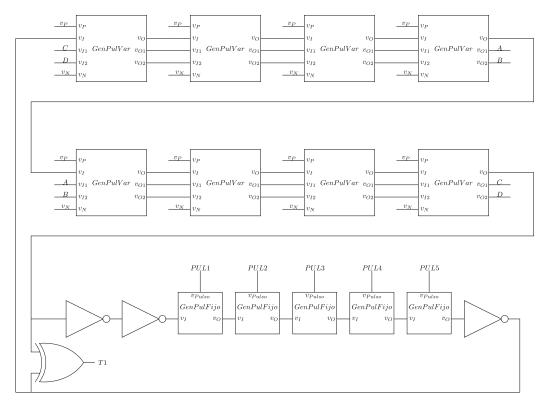

En lugar de usar una fuente de corriente constante con los problemas que esto conlleva, otra forma de implementar la técnica de "adiabatic switching" es mediante la aplicación de una rampa de voltaje a la capacidad en cuestión. En términos prácticos, la implementación de una rampa de tensión con una eficiencia energética en su generación es muy difícil de lograr, porque siempre provendrá de una fuente de tensión constante. En cambio, lo que se implementa en forma casi equivalente es dar varios saltos pequeños de tensión hasta alcanzar la tensión objetivo, dicha técnica se denomina "stepwise charging". A modo de ejemplo, en [19] se utiliza un conversor DC/DC de capacitores conmutados con múltiples tensiones de salida para emular dicha rampa. En [20] se utilizan un conjunto de condensadores auxiliares que toman y entregan energía según la capacidad en cuestión esta siendo cargada o descargada.

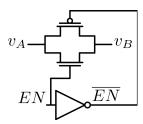

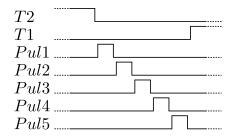

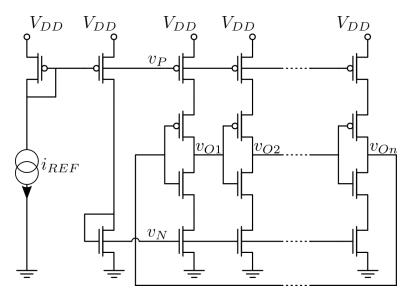

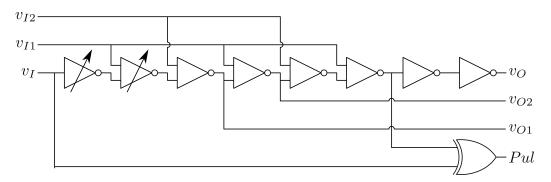

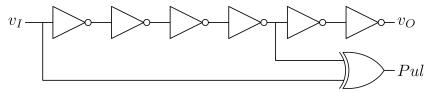

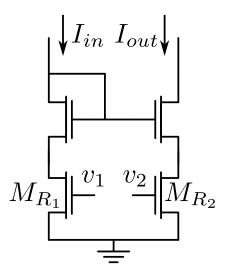

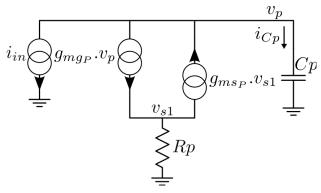

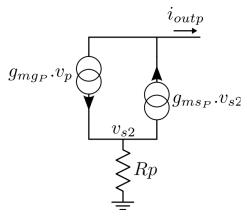

Esta última implementación (la que usa condensadores auxiliares) es posible solo en casos de carga y descarga cíclica que permitan asegurar la convergencia de las tensiones promedio de cada uno de los condensadores auxiliares, y tiene la ventaja de que no se necesita regulación en la tensión de ninguno nodo como se estudia en [21]. En este sentido, las llaves de un conversor DC/DC de capacitores conmutados son manejados cíclicamente. Por lo tanto, la capacidad del gate de dichos transistores serán cargadas y descargadas de forma cíclica también. De esta forma, la aplicación de la técnica de "stepwise charging" en el gate de las llaves de un conversor DC/DC de capacitores conmutados, usando condensadores auxiliares es apropiada. La figura 2.8 muestra un esquema del circuito donde la capacidad  $C_G$  representa la capacidad de una de las llaves a las cuales se quiere aplicar la técnica,  $CAux_i$  representa el i-esimo capacitor auxiliar, y  $SW_i$  la i-esima llave auxiliar usada para conectar la capacidad en cuestión con los capacitores auxiliares. Nótese que si se tienen N capacitores auxiliares, se deben usar N+2 llaves auxiliares ya que se debe tener la opción de conectar a fuente y tierra también.

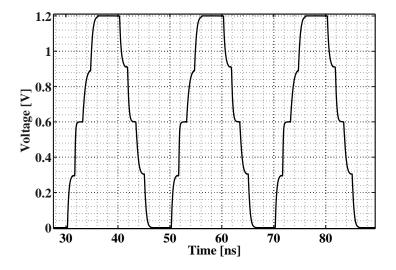

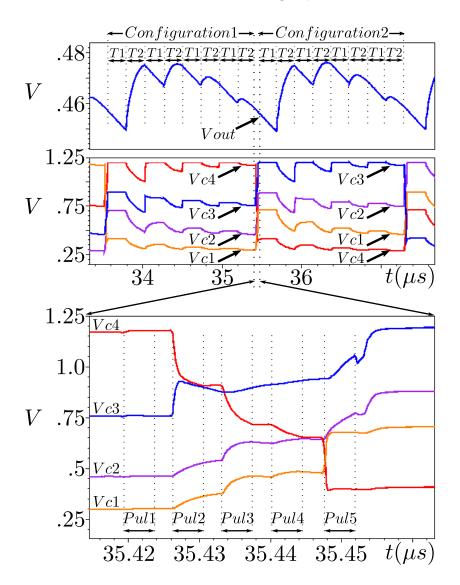

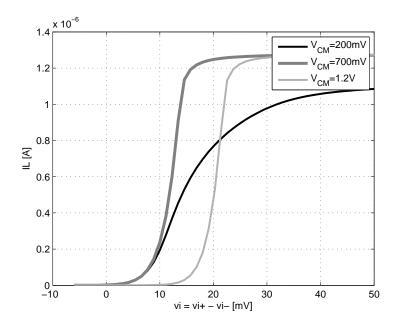

En un contexto donde todas las capacidades  $C_G$  se cargan y descargan periódicamente usando el mismo conjunto de capacitores auxiliares es posible asegurar la convergencia de la tension de cada uno de estos condensadores auxiliares como se estudia en [21] y [22]. Si se tienen N condensadores auxiliares, la tensión del i-esimo convergerá a  $V_i \simeq \frac{i.V_{DD}}{N+1}$ . En la figura 2.9 se muestra la tensión de la capacidad  $C_G$  en tres ciclos de carga y descarga para el caso N=3.

En [23] se presenta la posibilidad de aplicar esta técnica al gate de las llaves de un conversor DC/DC. Sin embargo, este análisis solo tiene en cuenta el flujo de energía de carga y descarga de las capacidades de los gates; pero no se analiza la pertinencia de la técnica en un sentido integral teniendo en cuenta todas las pérdidas involucradas. En esta sección se presenta un análisis teórico integral del ahorro que es posible alcanzar aplicando esta técnica al proceso de carga y descarga de una capacidad teniendo en cuenta todas las pérdidas involucradas. Por otro lado, se presentan resultados de medidas para un conversor DC/DC de capacitores conmutados a cuyas llaves se aplica la técnica de "stepwise charging".

# 2.2. Reciclado de carga del gate de las llaves

Figura 2.8: Stepwise charging.

Figura 2.9: Forma de onda de stepwise charging para  ${\cal N}=3.$

# 2.2.1. Análisis teórico de la técnica "stepwise charging"

Como toda técnica, su aplicación tiene un costo asociado debido a circuitos auxiliares. En este caso, se necesitan los capacitores auxiliares, las llaves que conectan  $C_G$  a los capacitores auxiliares fuente y tierra, y la lógica auxiliar que maneja el proceso de carga y descarga.

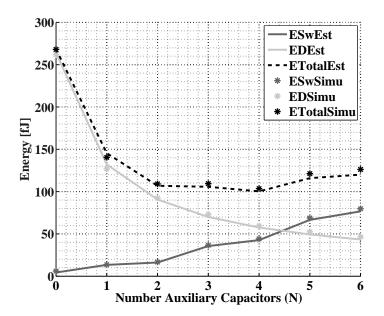

Un aspecto del sobre costo pagado por implementar la técnica es el área de silicio. Dado que el área en un conversor DC/DC de capacitores conmutados está largamente dominada por las capacidades principales del mismo, el overhead en área no es significativo y puede considerarse despreciable.

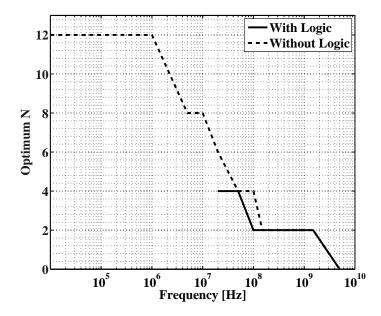

Por otro lado, se tiene un sobre costo en términos de consumo. Dicho sobre costo tiene una consecuencia mucho más importante que el área de silicio ya que directamente puede implicar que la aplicación de la técnica no tenga sentido. Si el consumo debido a los circuitos auxiliares es mayor que el ahorro entonces será mejor no aplicar la técnica. En esta sección se hace un análisis teórico que permite determinar en que casos es apropiado aplicar la técnica y el ahorro que se obtiene. Cuantos más condensadores auxiliares (y por lo tanto cuanto más chicos sean los saltos de tensión) mayor será el ahorro de energía en el proceso de carga y descarga. Sin embargo, también sera mayor el consumo debido a las llaves auxiliares y a la lógica que los maneja. Por lo tanto, habrá un número óptimo de condensadores auxiliares que maximiza el ahorro de energía.

Como se mencionó anteriormente, el proceso de carga y descarga de las capacidades de gate de las llaves de un conversor DC/DC se realiza de forma cíclica. Por lo tanto, si se usan capacitores auxiliares mucho más grandes que cualquiera de las capacidades a las que se quiere aplicar la técnica, entonces se podrá considerar los voltajes  $V_i$  como aproximadamente constantes. Además, dichos voltajes van a converger naturalmente a la tensión deseada sin necesidad de regulación. Esta convergencia está asegurada precisamente por la periodicidad de la carga y descarga ([21]).

Otro punto importante a tener en cuenta es la frecuencia a la cual se debe dar el proceso de carga y descarga. Cuanto mayor sea la frecuencia a la cual hay que cargar y descargar  $C_G$ , menor deberán ser las resistencias de las llaves auxliares, y por lo tanto mayor el ancho de los mismos y por lo tanto mayor la capacidad de los gates. Por todo esto, la frecuencia de carga y descarga debe ser tenida en cuenta también para realizar el análisis teórico.

#### Análisis de las pérdidas

Se tienen tres tipo de pérdidas en este escenario. Primero se tiene la energía  $(E_D)$  tomada desde la fuente para dar el ultimo salto de tensión y alcanzar la tensión de alimentación  $V_{DD}$  por intermedio de la llave  $SW_{N+1}$  (ver figura 2.8), segundo el consumo debido al manejo de las llaves auxiliares, y tercero el consumo

de la lógica que genera los pulsos para el manejo de las llaves auxiliares. Dado que existen muchas formas de implementar la lógica de control, en el análisis hecho en esta sección la misma no sera tenida en cuenta. Luego, en la siguiente sección se incluye el análisis que tiene en cuenta el consumo de la lógica que fue implementada.

La energía tomada desde la fuente para dar el último salto de tensión se puede calcular en función de que dicho salto vale  $\frac{V_{DD}}{N+1}$ . De esta forma la carga entregada por la fuente es  $Q_{V_{DD}}=C_G.\frac{V_{DD}}{N+1}$ . Por lo tanto, la energía consumida es la que se muestra en la ecuación 2.4.

$$E_D(C_G, N) = C_G \cdot \frac{V_{DD}^2}{N+1}$$

(2.4)

Luego, la energía consumida para el manejo de las llaves es la mostrada en al ecuación 2.5. En esta ecuación la capacidad  $C_{SW}$  es la suma de las capacidades de las distintas llaves auxiliares tendiendo en cuenta la frecuencia de uso de cada una de ellas según se muestra en la ecuación 2.6. En la misma, las capacidades correspondientes a las llaves que conectan la capacidad  $C_G$  a los condensadores auxiliares están multiplicados por un factor 2 debido a que se activan tanto para la carga como para la descarga de  $C_G$ , sin embargo  $SW_0$  solo se activa en el último paso del proceso de descarga y  $SW_{N+1}$  en el último paso del proceso de carga. Por esta razón no están afectados por dicho factor.

$$E_{SW}(C_G, N, f) = C_{SW} \cdot V_{DD}^2$$

(2.5)

$$C_{SW} = C_{SW_0} + C_{SW_{N+1}} + 2.\sum_{i=1}^{N} C_{SW_i}$$

(2.6)

Un punto fundamental en este análisis es la estimación de la capacidad de las llaves  $C_{SW_i}$  la cual dependerá de la frecuencia f a la cual se quiere conmutar la capacidad  $C_G$ . Cuanto mayor sea dicha frecuencia, menor deberá ser al constante de tiempo  $\tau$  de cada uno de los circuitos RC implementados por la capacidad  $C_G$ , las distintas capacidades auxiliares  $CAux_i$  y las resistencias  $R_{SW_i}$  de sus correspondientes llaves  $SW_i$ . Por lo tanto, la resistencia de la llave correspondiente deberá ser menor, para lo cual el ancho  $W_{SW_i}$  deberá ser mayor, y en consecuencia  $C_{SW_i}$  será mayor. En este punto es importante aclarar que si bien las constantes de tiempo  $\tau$  están determinadas por las capacidads  $CAux_i$ ,  $C_G$  y por  $R_{SW_i}$ , dado que  $CAux_i \gg C_G$  se tiene la siguiente aproximación:

$$\tau_i \simeq C_G.R_{SW_i} \tag{2.7}$$

Si consideramos que queremos cargar y descargar la capacidad en cuestion a una frecuencia f, y asumimos que la mitad del período se usa para cargar y la otra para descargar dicha capacidad, entonces podemos decir que cada uno de los saltos que se dan se deben lograr en un tiempo máximo  $T_{Aux}$  dado por la ecuación 2.8 donde  $T = \frac{1}{f}$

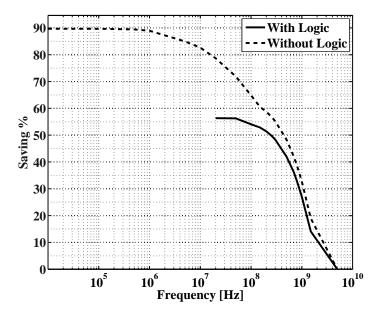

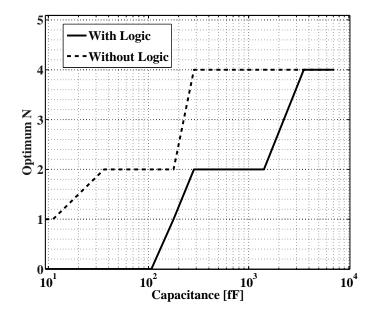

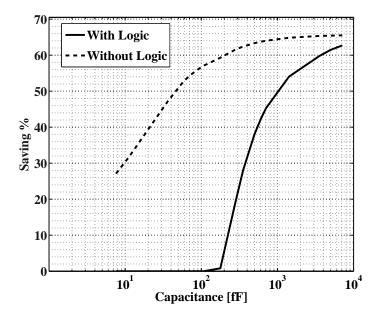

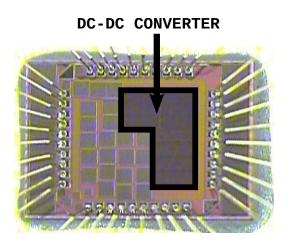

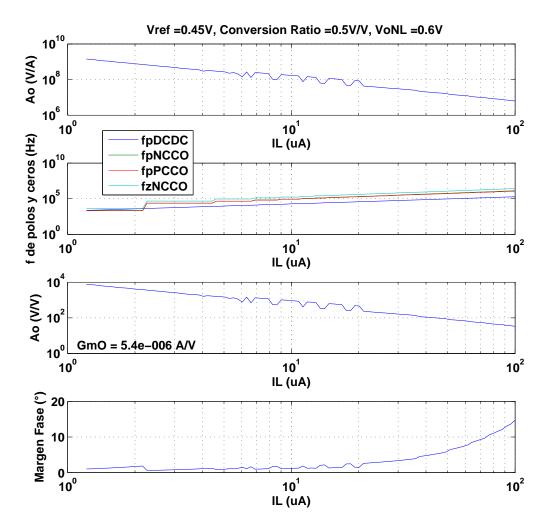

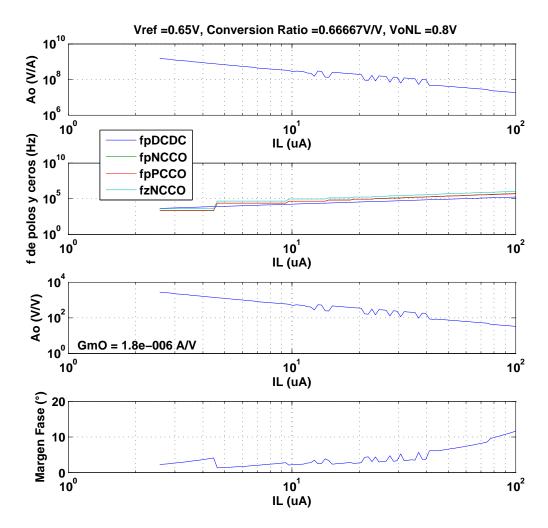

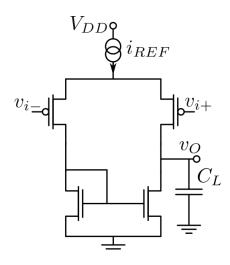

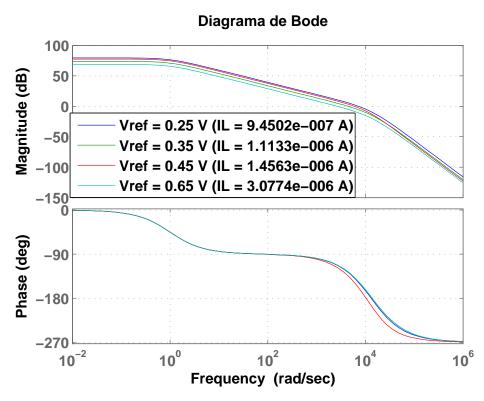

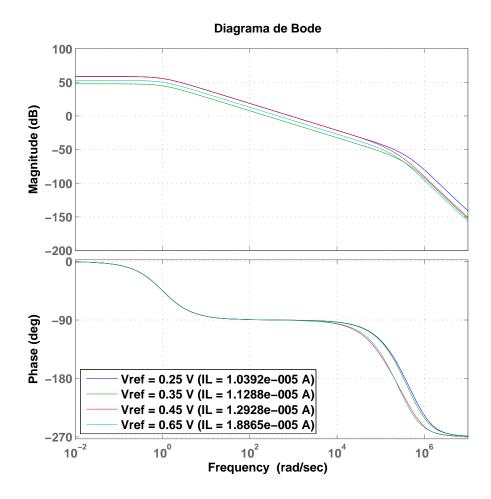

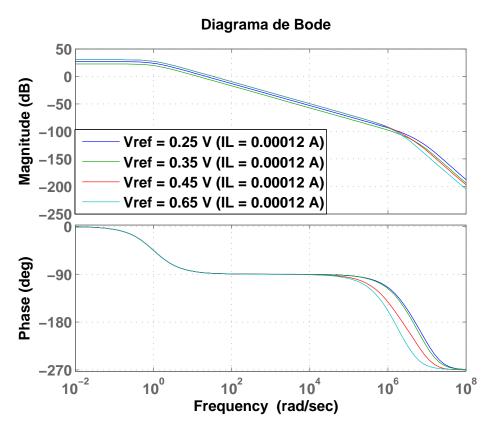

$$T_{Aux} = \frac{T}{2.(N+1)} \tag{2.8}$$